# ALMA MATER STUDIORUM - UNIVERSITÀ DI BOLOGNA

#### SCHOOL OF ENGINEERING AND ARCHITECTURE

Department of Electrical, Electronic, and Information Engineering "Guglielmo Marconi" DEI

# INGEGNERIA DELL'ENERGIA ELETTRICA curriculum ELECTRICAL ENGINEERING

MASTER THESIS in Power Electronic Circuits M

# A Modular Interleaved Converter for Output Current Ripple Minimization in DC Fast Chargers for Electric Vehicles

Presented by: Riccardo Mandrioli Supervisor: Prof. Gabriele Grandi

Co-supervisors: Prof. Mattia Ricco Dr. Manel Hammami Dr. Stefania Cuoghi

Academic Year 2018/2019 Session II

To whom made possible this path of personal and intellectual growth.

# Sommario

In questo lavoro viene presentata, progettata e testata una topologia circuitale per un caricabatterie DC off-board. Si prevede che sarà in grado di combattere l'ansia da autonomia riducendo significativamente gli attuali tempi di ricarica delle auto elettriche fino a 15-20 minuti, mantenendo contemporaneamente bassi costi di produzione, funzionamento e manutenzione. Il caricabatterie è composto da due stadi di potenza principali, i convertitori AC/DC e DC/DC. Al fine di mantenere i costi più bassi possibili, entrambe le parti sono progettate utilizzando topologie parallelizzate ed organizzate utilizzando gli stessi moduli trifase a due livelli accoppiati tramite induttori. Questa architettura consente di utilizzare i classici moduli trifase industriali sfruttando i vantaggi garantiti dalla produzione in serie e consentendo allo stesso tempo un'espansione senza sforzo grazie alla sua intrinseca modularità. Grazie alle connessioni interlacciate, è possibile raggiungere un'alta efficienza distribuendo simmetricamente corrente e potenza tra i rami. Inoltre, questa topologia può gestire flussi di potenza bidirezionali e potrebbe essere utilizzata per operare in entrambe le modalità Grid to Vehicle (G2V) e Vehicle to Grid (V2G). Al fine di ridurre le dimensioni e i costi dei componenti reattivi, viene sviluppata una strategia di controllo in grado di mantenere un ripple di corrente teoricamente nullo in qualsiasi condizione operativa. L'architettura del caricatore proposta utilizza un BUS AC di ingresso seguito da uno stadio raddrizzatore attivo. Una strategia di minimizzazione del ripple agisce sulla tensione variabile del BUS DC in accordo con il duty cycle del chopper mantenendo nullo il ripple di corrente. Nel frattempo, lo stadio DC/DC fornisce la corrente di uscita richiesta. Questa strategia coinvolge l'AC/DC con i compiti di regolare il livello di tensione del DC BUS e correggere il fattore di potenza in ingresso. Viene utilizzato un sistema di controllo modelbased in grado di assicurare che la corrente di ogni ramo segua un riferimento di corrente medio. Attraverso una rete di ribilanciamento gli sbilanciamenti di corrente vengono attivamente compensati. Le simulazioni vengono eseguite utilizzando l'ambiente MATLAB Simulink e convalidate attraverso misurazioni in laboratorio su un prototipo dimensionato su scala ridotta di potenza.

# Abstract

In this work, a DC off-board fast battery charger topology is presented, designed, and tested. It is expected to be able to fight the range anxiety by significantly diminish the EVs' charging times up to 15-20 minutes, meanwhile keeping low manufacturing, Operation and Maintenance (O&M) costs. The charger is made out of two main power stages the AC/DC and DC/DC converters. In order to keep the costs lower as possible, both parts are designed using interleaved topologies organized by using the same two-level three-phase modules coupled through reactors. This architecture allows to use the already well-known industrial three-phase modules taking advantage of the benefits guaranteed by mass production and at the same time permitting an effortless expansion thanks to its modularity. Thanks to the interleaved connections, it is possible to reach a high efficiency by distributing current and power evenly among the legs. Furthermore, this topology can handle bidirectional power flows, and it might be used for operating in both Grid to Vehicle (G2V) and Vehicle to Grid (V2G) modalities. In order to reduce the dimensions, and the costs of the filters, a control strategy able to keep a zero current ripple at any operative condition is developed. The proposed charger architecture uses an AC input BUS followed by an active rectifier stage. A ripple-free strategy acts on the variable DC BUS voltage according to the chopper duty cycle keeping the current ripple null. Meanwhile, DC/DC provides the requested output current. This strategy involves the AC/DC with the tasks to regulate the DC BUS voltage level and correcting the input power factor. A model-based control system ensures that every leg's current follows an average current reference signal. Legs' currents are actively rebalanced throughout a current rebalancing network. Finally, the simulation results are carried out trough MATLAB Simulink and validated with laboratory measurements on an adequately scaled prototype.

# Contents

| Sc       | omma              | ario          |                                                |   |  |   |  |  |   | 1         |

|----------|-------------------|---------------|------------------------------------------------|---|--|---|--|--|---|-----------|

| A        | bstra             | $\mathbf{ct}$ |                                                |   |  |   |  |  |   | <b>2</b>  |

| In       | trod              | uction        |                                                |   |  |   |  |  |   | 6         |

| 1        | Proposed Topology |               |                                                |   |  |   |  |  |   |           |

|          | 1.1               | Back t        | to Back AC/DC Interleaved Converter            |   |  |   |  |  |   | 13        |

|          |                   | 1.1.1         | Active Rectifier Power Stage                   |   |  |   |  |  |   | 15        |

|          |                   | 1.1.2         | Interleaved Buck Converter                     |   |  |   |  |  |   | 24        |

|          | 1.2               | IBC's         | Inherent Ripple Reduction                      |   |  |   |  |  |   | 27        |

|          |                   | 1.2.1         | Current Ripple in Full Legs                    |   |  |   |  |  |   | 27        |

|          |                   | 1.2.2         | Current Ripple in Interleaved Topologies       | • |  | • |  |  | • | 29        |

| <b>2</b> | Rip               | ple Fre       | ee Strategy                                    |   |  |   |  |  |   | <b>37</b> |

|          | 2.1               | -             | Free Strategy in the Proposed Case with 9 Legs |   |  |   |  |  |   | 37        |

|          |                   | 2.1.1         | DC Link Voltage Variation Range                |   |  |   |  |  |   | 38        |

|          |                   | 2.1.2         | Legs Ripple Minimization Criterion             |   |  |   |  |  |   | 40        |

|          |                   | 2.1.3         | DC Link Voltage Transients                     |   |  |   |  |  |   | 43        |

|          | 2.2               | Ripple        | • Free Strategy in a General Case with N Legs  |   |  |   |  |  |   | 43        |

|          |                   | 2.2.1         | General Algorithm                              |   |  |   |  |  |   | 45        |

|          |                   | 2.2.2         | Transients Maximum Output Current Ripple       |   |  |   |  |  |   | 47        |

| 3        | Ger               | neral C       | ontrol Strategy                                |   |  |   |  |  |   | 50        |

|          | 3.1               | Averag        | ged Main Control                               |   |  |   |  |  |   | 51        |

|          |                   | 3.1.1         | Possible Transfer Function Assumptions         |   |  |   |  |  |   | 57        |

|          |                   | 3.1.2         | Average Duty Cycle Control                     |   |  |   |  |  |   | 61        |

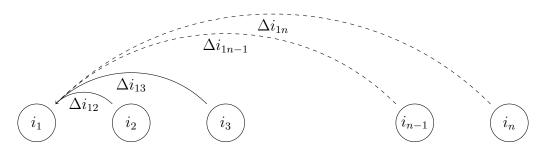

|          | 3.2               | Currer        | nt Rebalancing Network                         |   |  |   |  |  |   | 63        |

|          |                   | 3.2.1         | Duty Cycles Computation                        |   |  |   |  |  |   | 65        |

|          |                   | 3.2.2         | Rebalancing Action and Ripple-Free Strategy .  |   |  |   |  |  |   | 71        |

|          | 3.3               | PWM           | Generation and Current Sampling                |   |  |   |  |  |   | 71        |

| 4        | Sim               | ulatior       | ns and Measurements                            |   |  |   |  |  |   | <b>74</b> |

|          | 4.1               | IAR S         | imulation                                      |   |  |   |  |  |   | 75        |

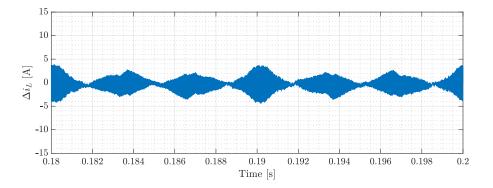

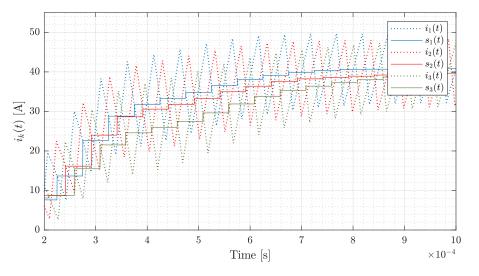

|          |                   | 4.1.1         | IAR's Input Currents Ripple Reduction          |   |  |   |  |  |   | 75        |

|          | 4.2               | IBC S         | imulations                                     |   |  |   |  |  |   | 76        |

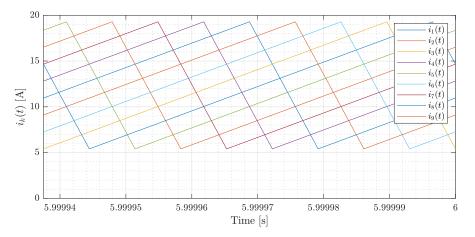

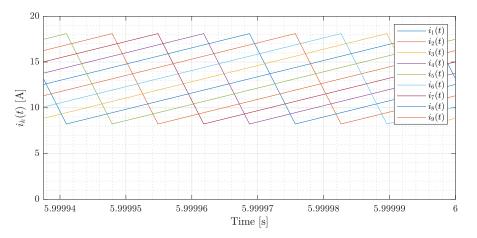

|          |                   | 4.2.1         | IBC's Output Current Ripple Reduction          |   |  |   |  |  |   | 76        |

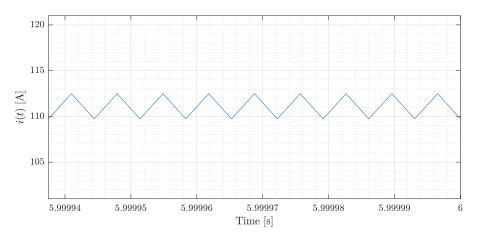

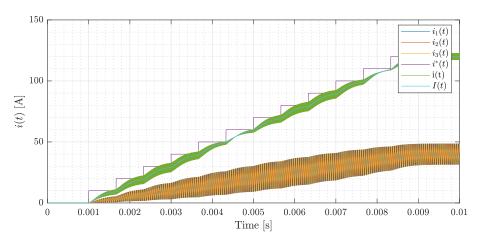

|          |                   | 4.2.2         | IBC's Output Current Ripple Cancellation       |   |  |   |  |  |   | 77        |

|          |                   | 4.2.3         | Equivalent IBC for Control Purposes            |   |  |   |  |  |   | 78        |

| 4.3                                      | 4.3 Ripple-Free Strategy Simulations |                                                               |    |  |  |  |

|------------------------------------------|--------------------------------------|---------------------------------------------------------------|----|--|--|--|

|                                          | 4.3.1                                | Ripple-Free Strategy Total Output Current Ripple Cancellation | 81 |  |  |  |

|                                          | 4.3.2                                | Ripple-Free Transients                                        | 81 |  |  |  |

| 4.4 General Control Strategy Simulations |                                      |                                                               |    |  |  |  |

|                                          | 4.4.1                                | Mean Value Sampling Strategy                                  | 85 |  |  |  |

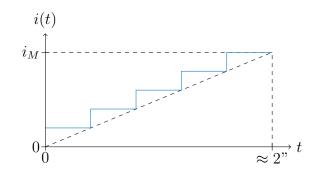

|                                          | 4.4.2                                | Precharge Current Staircase                                   | 86 |  |  |  |

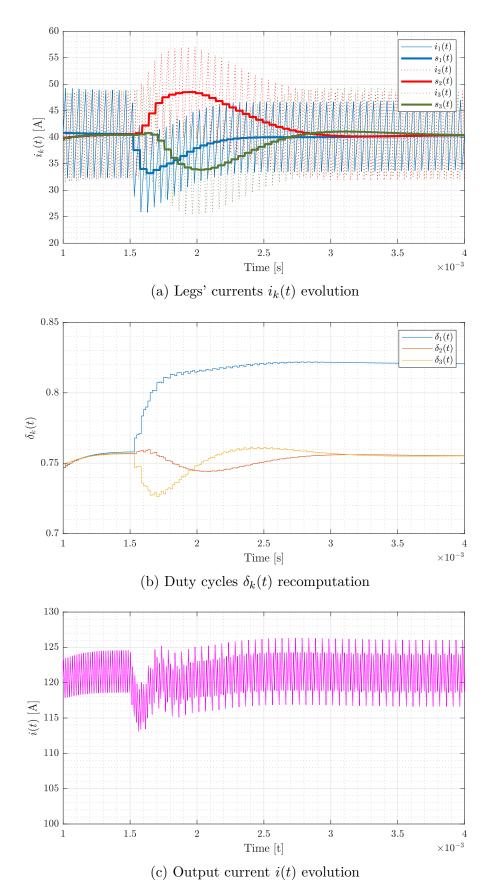

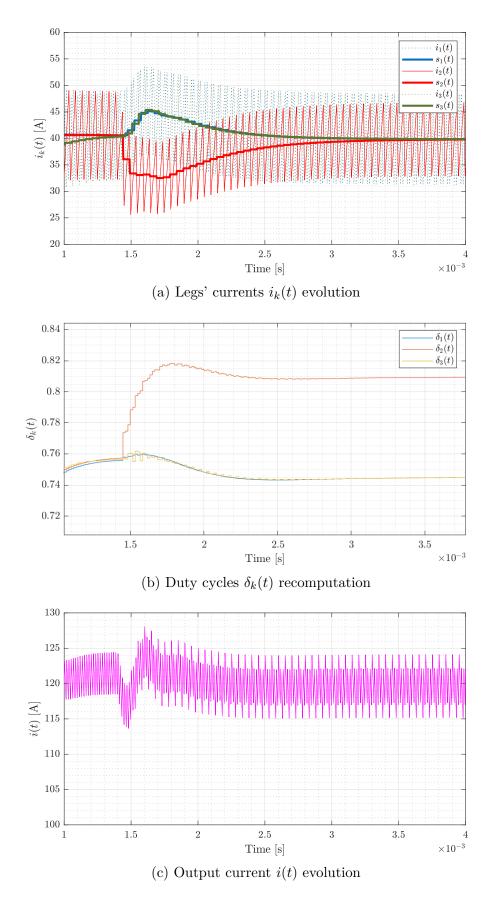

|                                          | 4.4.3                                | Current Rebalancing Network                                   | 87 |  |  |  |

| 4.5 Experimental Measurement             |                                      |                                                               |    |  |  |  |

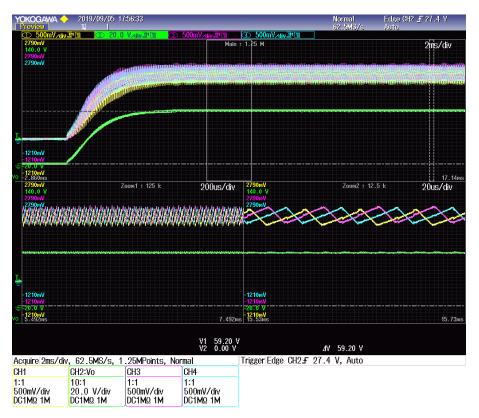

|                                          | 4.5.1                                | Averaged Main Control Step Response                           | 91 |  |  |  |

|                                          | 4.5.2                                | Capacitor Branch Removal Assumption                           | 92 |  |  |  |

|                                          | 4.5.3                                | Inductance Unbalance Robustness Test                          | 93 |  |  |  |

|                                          | 4.5.4                                | Current Rebalancing in Unbalanced System                      | 94 |  |  |  |

| Conclu                                   | sion                                 |                                                               | 95 |  |  |  |

| Bibliography                             |                                      |                                                               |    |  |  |  |

| List of Figures 1                        |                                      |                                                               |    |  |  |  |

| List of Tables 1                         |                                      |                                                               |    |  |  |  |

| Acrony                                   | Acronyms 1                           |                                                               |    |  |  |  |

| Nomen                                    | Nomenclature 11                      |                                                               |    |  |  |  |

# Introduction

The highly globalized society heavily underpins on transport systems. They are directly involved in the creation of market value, and their relevance in the Gross Domestic Product (GDP) computation has increased in the last decades. Transport improves the standard of life and rate of employment thanks on its capability to connect people, goods, and services. However, it has adverse effects on the environment, climate, and human health. In order to attenuate these drawbacks, a green shift towards decarbonized transport systems is necessary.

Although Europe managed to obtain a generally noticeable Greenhouse Gasses (GHGs) emissions reduction, the transport systems sector is still responsible for a quarter of them. Furthermore, it can be directly linked to the deteriorated urban areas quality of air that often does not meet standards set by European Union (EU), World Health Organization (WHO), and Environmental Protection Agency (EPA) [1].

Institutions and governments are setting multiple future targets to reduce anthropological environmental impacts. In the last decades, multiple worldwide organizations have faced this problem. United Nations (UN) Intergovernmental Panel on Climate Change (IPCC) throughout, United Nations Framework Convention on Climate Change (UNFCCC) have produced famous legally binding treaties like the Kyoto Protocol and Paris Agreement. EU's overall goal is to reduce by 85-90% GHG emissions by 2050. A gradual reduction pattern able to provide relevant outcomes without giving up current economic growth rates has been studied.

Firstly, throughout Horizon 2020 and NER300 financing programs, research and innovation are being carried out in fields like transports and low-carbon projects. Carbon dioxide removing technologies such as Land Use, Land-Use Change, and Forestry (LULUCF) and Carbon Capture and Storage (CCS) have been funded with about 2 billion euro. The 2020 main targets are to cut GHG emissions by 20% (compared to 1990 levels), having 20% of the produced energy using Renewable Energy Sources (RES) and increase by 20% the overall energy efficiency.

Secondly, in the 2030 climate-energy framework, previously cited data are expected to reach 40%, 32% and 32.5% for GHG emissions cuts, RES share, and energy efficiency improvement, respectively.

Finally, Europe plans to become the world's first major economy to go climateneutral by 2050 [2]. In [3] European Commission (EC) have set 10 goals for reaching the 60% transport GHG emission reduction benchmark. Among them, the first goal explicitly referred to new sustainable propulsion systems able to reduce to the half the use of Internal Combustion Engine Vehicles (ICEVs) in urban transport by 2030, phase them out in cities by 2050 and lastly achieve essentially carbon-free city logistics in major urban centers by 2030. Achieving these commitments require complete decarbonization of the passenger car fleet by 2050. Meanwhile, the more ambitious COP21 that have stipulated the Paris Agreement demands a complete decarbonization of transport to limit temperature rises to 1.5°C.

It is then apparent how a relevant part of the planned GHGs emissions reduction is expected to come from newer and cleaner road transports technologies. Transport is the only primary sector having increased its environmental impact since 1990, and a considerable effort is therefore necessary. For this reason, more efficient ICEVs are unlikely to be sufficiently compelling to achieve previously cited targets. EV is one of the most promising ways of moving toward a more sustainable transport system [1]. Although replacing ICEVs with EVs is not enough, the  $CO_2$  emissions reduction strongly depends on the mix of primary energy sources used to generate electricity. As relevant, the RES component is as powerful the  $CO_2$  reduction could be.

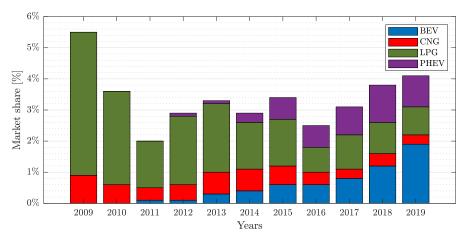

As aforementioned, EVs are expected to be a key component of the future mobility system. Moreover, cars are much easier to decarbonize if compared to other vehicle types. The market is entering a more mature stage, and comparisons at least between Alternative Fueled (AF) vehicles can be made. As visible in Figure 1, since 2016, electricity-powered vehicles have constantly outperformed gas-based solutions (Compressed Natural Gas (CNG) and Liquefied Petroleum Gas (LPG)) in terms of European new registrations AF market share. Battery Electric Vehicles (BEVs) and Plug-in Hybrid Electric Vehicles (PHEVs) comprised both around 1.2% of the new car registrations in 2018. Moreover, BEVs are expected to roughly double 2019 PHEVs' new registrations with respectively 1.9% and 1%. Fuel Cell Electric Vehicles (FCEVs) have not reached yet a satisfying Technology Readiness Level (TRL) for being widely distributed in the market. Previously stated selling considerations are performed using European Alternative Fuels Observatory (EAFO)<sup>1</sup> data.

Figure 1: AF vehicles new registrations market share

Although forecasts are still unreliable most of the financial surveyors and analysts agree that break-even point between ICEVs and BEVs purchase cost should be met during the mid-2020s, with Total Cost of Ownership (TCO) lagging from two to four years [4]. The sales parity should be reached around 2037, and in 2040,

<sup>&</sup>lt;sup>1</sup>More information can be found at European Alternative Fuels Observatory (EAFO) website www.eafo.eu

30% of the global fleet could be electric. Prices and diffusion of Zero-Emissions Vehicles (ZEVs) are strictly correlated with charging infrastructure diffusion. In the next decade, a relevant acceleration in BEVs diffusion is expected. However, if a comparable acceleration does not involve charging points diffusion, a relevant slow down is expected to happen during the early 2030s. Customers able to take advantage of overnight home charge are expected to be the first ongoing electric, a second customers wave is expected as soon as a reliable charging network is available. Furthermore, the current selling trend of hybrid solutions could gradually fade and become a negligible fraction of BEVs sales.

Many barriers to electric vehicles are incrementally being overcome. Batteries cost is falling, it is reaching the industrial target of 100\$/kWh and in 2030 is expected to halve current prices and stabilize around 70\$/kWh. This prices evolution is helping on addressing the initial cost barrier and driving to greater battery sizes. Overall the average range availability has more than doubled its value from the 160km of 2010 to about 400km of 2019. The increasing availability of electric vehicle models is attracting more prospective vehicle owners. However, the development of sufficient charging networks, is still a work in progress. Although the regular overnight home charging constitutes one of the great advantages of electric automotive technology, it does not fulfill every charging needs, and a mix of workplace charging, public charging, and fast charging is indispensable [5]. As described above, BEVs offer relevant opportunities to reduce GHGs and local air pollution, especially in the "inuse" phase of vehicle life. However, considering the whole Life Cycle Assessment (LCA) of an EV, there is the possibility to increase impacts in other areas such as human toxicity and ecosystem impacts. Focusing on vehicle design, the battery pack constitutes the most environment impacting part of the vehicle. Customers' expectations might be a key factor for future battery development. Larger batteries provide greater energy leading to a reduction of users' "cruising range anxiety". However, larger batteries require a higher quantity of raw materials and greater manufacturing energy resulting in greater environmental impacts. Furthermore, the extra weight also leads to a bigger energy requirement during BEVs usage. Those impacts cross the life cycle could be minimized if the automotive industry is encouraged to propose vehicles with modest ranges and batteries sizing but able to fully charge in a few minutes.

A huge effort is put on research around the feasibility of BEV batteries playing an active role in the electricity grid, to store excess renewable power and provide grid-stabilizing services. These services are commonly described under umbrella terms such as Vehicle to Grid (V2G), Vehicle for Grid (V4G) and Vehicle to Home (V2H). In order to take advantage of the relevant energy stored inside BEVs, more ductile converters topologies able to withstand bidirectional power flows are necessary.

The aforementioned regulatory and design constraints must be balanced with wide charging networks with an appropriate number of outlet per stations and charging settings.

Usage statistics have pointed out how fast-charging stations play a key role thanks to their ability to guarantee excellent distance coverage and the broad charging flexibility. Data shows how fast charge outlets have been used not only for long

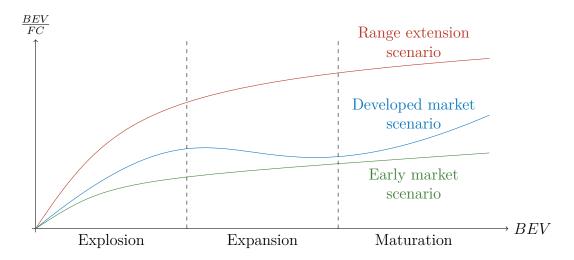

Figure 2: Possible scenarios of BEV over FC ratio in different BEVs' penetration stages

journey charging but also as a substitute for the home and the slower public charging. During the early market (green line in Figure 2), more fast chargers (FCs) per vehicle are needed to obtain sufficient geographic coverage, regardless on the market stage. As the market develops (blue line in Figure 2), less FCs per vehicle are needed as utilization increases. In a market scenario where FCs are employed for extension range only (red line in Figure 2), fast charging Electric Vehicle Supply Equipment (EVSE) are expected to have a marginal relevance if compared with the previously cited scenarios once the market have reached a considerable expansion. On the other hand, only a limited range of models are already able to take advantage of the full available power. An economically speaking feasible way for achieving these targets is to implement low cost and modular convert topologies able to guarantee a wide multi-column stations diffusion and aposteriori power scaling capability. Moreover, a discrete fast charging power deploying by mean modules based paradigm permits to effectively response to the different market stimulations in terms of FCs' diffusion and absolute power capability. Charging infrastructure is the most significant longterm challenge for EV, and comprehensive, user-friendly urban and long-distance fast-charging stations are a precondition to the growth of the market.

When new technologies start to grow multiple standards appear on the market. Every Operation and Maintenance (O&M) try to impose its own standard in order to gain market share and customers loyalty. For what it concerns EV standards, two main areas should be considered, charging plugs and charging levels standards.

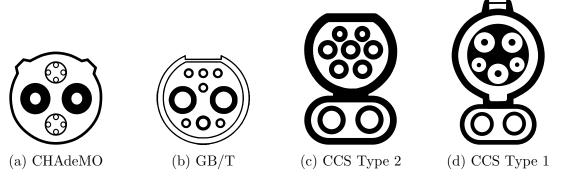

When it comes to speak about charging plugs, there are mainly four main standards, each of one well settled in a particular market and geographical area. Moreover, depending on what kind of charging is carried out, plugs can carry AC or DC for respectively onboard and offboard chargers. In this thesis, offboard DC fast charging is considered. Combined Charging System (CCS) type 2 (also known as Combo 2) (Figure 3c) has been introduced as a common DC charging plug for all the European market. It shares most of the connection available in the AC Type 2 connector. However, it adds two power pins able to carry DC. Similarly, CCS type 1 (Figure 3d) is mainly employed in the North America market. One of the most used standard is the Chinese Guobiao Standard (GB/T) (Figure 3b) charging plug that shares most of the features present in other standards [6]. One of the oldest DC charging plug is the so-called CHArge de MOve (CHAdeMO). It is mainly employed in the Japanese market, although, it has initially diffused in North America and Europe it is rapidly being overcome from CCS standards. All the connectors have in common the presence of power connectors and a communication link between the offboard power converter and the internal Battery Management System (BMS). Tesla motors have introduced in the North America market a property standard able to carry DC power over a regular Type 1 AC plug. Most of them have been described inside IEC 62196 and SAE J1772 standards [7], [8]. In Table 1, DC charging plug features are collected.

Table 1: DC charging plugs standards

| Denomination | Region  | Typical power | Maximum power | Standard    |

|--------------|---------|---------------|---------------|-------------|

| CHAdeMO      | Japan   | 50kW          | 400kW         | IEC 62196   |

| CCS Type 1   | America | 50kW          | 400kW         | IEC 62196   |

| CCS Type 2   | Europe  | 50kW          | 400kW         | IEC 62196   |

| GB/T         | China   | 50kW          | 240kW         | GB/T 20234  |

| Tesla        | America | 125kW         | 145kW         | Proprietary |

For what it concerns charging power, multiple denominations have been introduced during the time. A first classification based on the power rating is known as charging level. Level 1 is considered the slowest charging rate, and it is usually employed in nations where the grid phase voltage is 120V AC for no more than 11kW. Level 2, is considerably faster than Level 1 because able to reach 22kW, it employs AC 230V grids. The charging rate considered in this thesis is Level 3 (also known as Fast Charging). It employs DC voltages up to 1000V and powers than start from 50kW and reaches 400kW in the latest installations.

Figure 3: DC charging plugs

Depending on what type of connection and on the safety devices used, charging modes are defined. Mode 1 does not require any protection device or communication channel between EV and charger. Mode 2, it employs a communicating channel called pilot function, and a protective circuit breaker is required. Mode 3 differs from Mode 2 for the requirement to have one cable terminal hardwired to the EVSE. Moreover, Mode 4 adds a continuous bidirectional communication between EV's BMS and the EVSE. This communication can be made throughout different technologies depending on what plug is used. For instance, CCS and CHAdeMO plugs, respectively employ Power Line Communication (PLC) and Controller Area Network (CAN) bus.

Overall, EVSEs equipped with modular highly standardizes bidirectional modules are expected to be one of the key part in the transport electrification in the near future. Moreover, power converters are expected to successfully follow market and political scenarios. Charging power availability must be tuned according to the EV diffusion. Generally, charging times should be guarantee as lower as possible, ensuring an EVs charging experience more similar to the common ICEVs refueling. For the above mentioned reasons, a battery charger topology able to ensure modularity, upgrade capability, low cost and fast charging is introduced in next chapters.

# Chapter 1 Proposed Topology

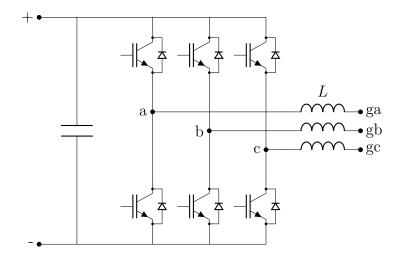

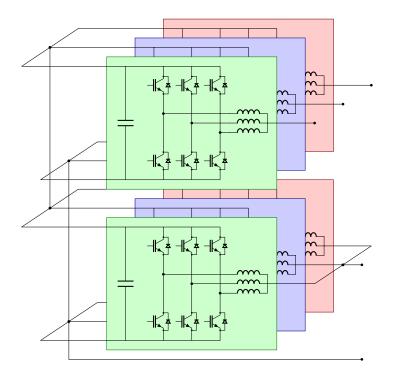

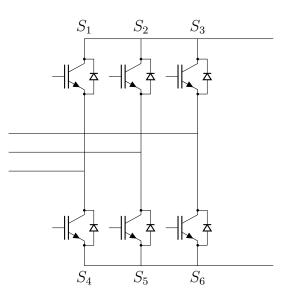

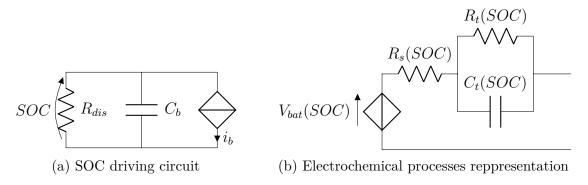

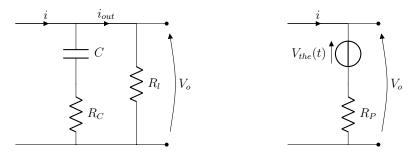

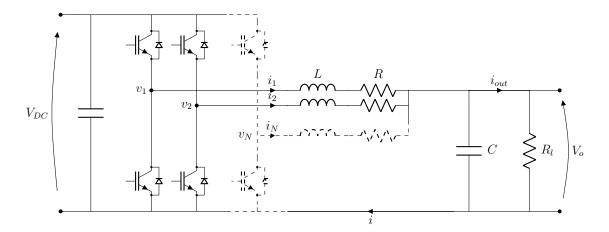

Many converter topologies and modulation strategies have been introduced in the literature. Speaking about inverters (DC/AC converters), most of the research activities are oriented to the multilevel topologies such as Neutral Point Clamped (NPC) [9], [10], Level Doubling Network (LDN) [11], Modular Multi-level Converter (MMC) [12], Flying Capacitor (FC) and cascaded H-bridge [13]. Despite the improvement of the performances in terms of harmonic content and ripple amplitude of the output current and voltage, they all require more components if compared with the standard two-level three-phase converter. In the field of rectifiers, the academic interest has passed from passive diodes-based solutions like 6 and 12 pulses rectifiers to active rectifiers, based on power switches solutions such as Vienna [14], Swiss [15], [16], and Totem Pole rectifier (also simply known in literature as Active Rectifier (AR)) [17], [18]. However, it can be seen that by considering a three-phase system the Totem Pole topology becomes like a three-phase inverter used in the opposite direction, having also a Power Factor Correction (PFC) capability. Concerning bidirectional DC/DC voltage lowering stage, the most widely studied topology is the synchronous buck converter and its multi-phase version called synchronous multiphase Buck Converter (BC) [18]. It can be noticed that if the number of considered phases is set to three the topology coincides to three full legs with the poles coupled with an interleaved connection. It can be then concluded how every power stage (regardless if it is an active rectifier, inverter or chopper) can be implemented by means of two-level three-phase modules with the connections properly handled in order to achieve the desired tasks (Figure 1.1). Despite it is not the best solution when speaking about harmonics and ripple amplitude, it can be certainly concluded that it constitutes the most standardized solution among all the proposed topologies presented in the literature.

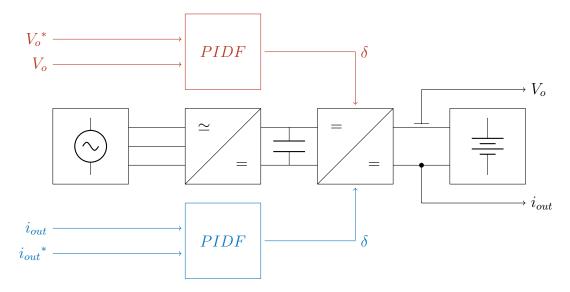

By mean of a proper routing of these simple blocks, it is possible achieving improvements in terms of ripple and efficiency. Interleaved configurations are one of the most suitable topologies for charging EVs since they are able to ensure modular design approaches. The best performances can be achieved for level 4 DC fast charging rates thanks to the possibility to evenly share the great involved power. As visible in Table 1.1, most of the EVSE power electronic producers have currently in their portfolio at least one series of products that implements somehow the modularity paradigm explained before [19]-[24].

It is possible to make either AC/DC and DC/DC based on multiple standardized bidirectional two-level three-phase block (Figure 1.1). Interleaved version of AR and

| Producer    | Denomination | Base unit           | Power module      | Available ratings            |

|-------------|--------------|---------------------|-------------------|------------------------------|

| ABB         | Terra HP     | N/A                 | $175 \mathrm{kW}$ | $175/350 {\rm kW}$           |

| Watt&Well   | BMPU-11      | $11 \mathrm{kW}$    | N/A               | $150/300 {\rm kW}$           |

| Alpitronic  | Hypercharger | N/A                 | $75 \mathrm{kW}$  | $75/150/225/300 \mathrm{kW}$ |

| ChargePoint | Express Plus | $31.25 \mathrm{kW}$ | $156 \mathrm{kW}$ | 156/312/468/500kW            |

| Signet      | FC100K       | N/A                 | N/A               | $50/100 {\rm kW}$            |

| Efacec      | HV175        | N/A                 | $163 \mathrm{kW}$ | $163/326 {\rm kW}$           |

| BTC Power   | HPCT         | N/A                 | $50 \mathrm{kW}$  | $100/150/200 \mathrm{kW}$    |

| Tesla       | Supercharger | 11.5kW              | N/A               | 120/150kW                    |

Table 1.1: Overview of DC modular fast charger commercially available

the BBC are know respectively as Interleaved Active Rectifier (IAR) and Interleaved Buck Converter (IBC). The main idea is to share current equally (and therefore power) on multiple legs, regardless of what task the block is doing (AC/DC or DC/DC operations) and on the power flow direction. This inherent capability to carry bidirectional power flows makes it particularly suitable for storage management application like BEVs charging and V2G services.

Figure 1.1: Two-level three-phase base block

In order to share current that usually would flow into a single leg among multiple legs is necessary to interleave them using properly sized reactors (visible in Figure 1.1 as L) [25]–[27].

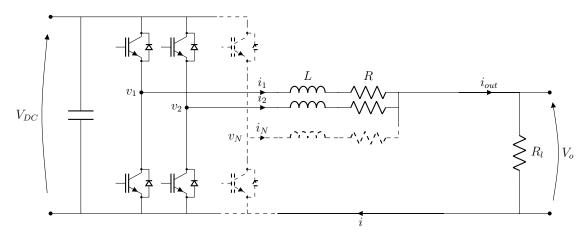

# 1.1 Back to Back AC/DC Interleaved Converter

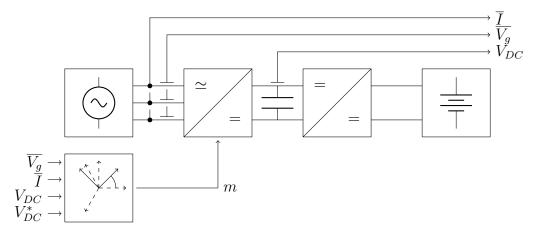

The interleaving fast charger topology shown in Figure 1.2 is considered in this thesis. It must respect all the design and economic constraints mentioned before. The proposed topology can be connected to a low voltage grid and provide an output voltage range suitable for battery charging purposes.

Firstly, a modular configuration able to use the same block of Figure 1.1 in both AC and DC side has to be considered. Thanks to this technical solution it facilitates a future power scaling by simply stacking more blocks in parallel to the

| Parameter                     | Symbol    | Value | Unit      |

|-------------------------------|-----------|-------|-----------|

| Rated power                   | Р         | 150   | kW        |

| Base block rated power        | $P_b$     | 50    | kW        |

| Number of block per side      | $M_s$     | 3     |           |

| Total number of block         | M         | 6     |           |

| Number of legs per base block | $N_b$     | 3     |           |

| Number of legs per side       | N         | 9     |           |

| Line to line RMS voltage      | $V_g$     | 400   | V         |

| Grid frequency                | f         | 50    | Hz        |

| Maximum DC link voltage       | $V_{DCM}$ | 800   | V         |

| Minimum DC link voltage       | $V_{DCm}$ | 600   | V         |

| Maximum output voltage        | $V_{oM}$  | 800   | V         |

| Minimum output voltage        | $V_{om}$  | 200   | V         |

| Switching frequency           | $f_{sw}$  | 16    | kHz       |

| Reactors inductance           | L         | 0.5   | mH        |

| Reactors resistance           | R         | 20    | $m\Omega$ |

| DC link capacitance           | C         | 1     | mF        |

Table 1.2: Proposed system parameters

already present one without oversizing the system and keeping initial deployment cost as lower as possible. A further benefit is the possibility to operate with a smaller power rating in case of faults or programmed maintenance. It is possible to freely keep out blocks without shutting completely down the converter. Underload conditions can be avoided implementing the classic, N + 1 redundancy. Overall, the system becomes more fault resilient and at the same time "low cost".

Secondly, each module is a replica of the others. Moreover, the three-phase two-level module is by far the most common power block thanks to its broad commercialization and ductility. These considerations ensure to take advantage of mass production economic benefits keeping production and therefore replacement and expansion costs as small as possible. Despite being "low cost" blocks, they have reached a high level of standardization and can ensure optimization in terms of Electromagnetic Interference (EMI) [28], [29], thermal layout, protection devices, and driving units.

Finally, this redundancy adds a further degree of freedom on the firing timing of each leg. Thanks to proper handling of the driving signal, it is possible to automatically reduce ripple in every part of the converter (I/O currents and DC link voltage) [30]–[35]. Reactive components sizing constraints are therefore less strict and in general, smaller components are needed. Inductors and capacitors are usually the bulkier components in a power converter. It is then possible space and weight saving leading to a more efficient room utilization. When it comes to speak about bus DC capacitor, it is known that ripple is one of the most degrading agent in electrolytic capacitors [36], [37].

In this thesis a symmetrical scheme (Figure 1.2) with nine legs and therefore three blocks for either the AR/inverter stage and the chopper has been developed.

Figure 1.2: Battery charger topology

In Table 1.2 design parameters are summarized.

# 1.1.1 Active Rectifier Power Stage

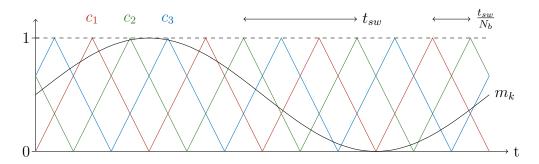

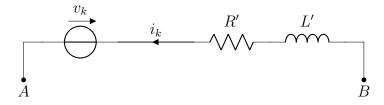

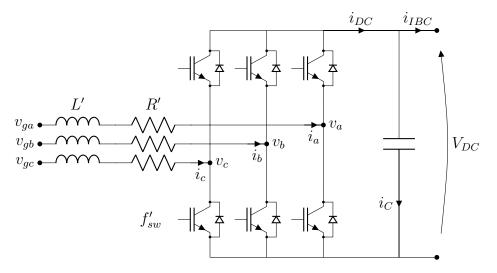

As visible in Figure 1.3 the AC/DC stage (suitable for both active rectifier and inverter purposes) takes advantage of three legs per phase. As explained above the power can be evenly shared among them, making therefore possible using small size low-cost power switches. As shown in [33], [35], [38], DC link and input current ripple decrease when each leg of each phase is driven by mean of uniformly shifted carriers (Figure 1.4) [18], [39]–[42]. In each power block, there are  $N_b$  carriers, and each one has been shifted by  $t_{sw}/N_b$ . When it comes to speak about the modulating

Figure 1.3: Interleaved active rectifier topology

signal generation it is necessary to operate on a synchronous framework able to take into account the parallelized design property of each phase. Despite what it has been done in section 1.2.2, inductors' ohmic component has been taken into account. For the sake of completeness, a generic analysis on  $N_b$  legs is carried out.

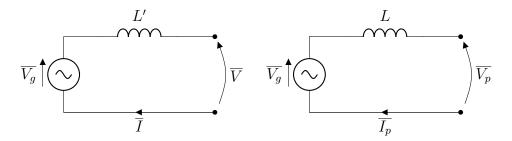

Figure 1.4: Drawing that shows  $N_b = 3$  shifted carriers  $(c_1, c_2, \text{ and } c_3)$  and a generic modulating signal  $m_k$  (SPWM)

As visible in Figure 1.5 each phase leg can be averaged on a switching period leading the whole phase power block to a simplified single branch equivalent system (Figure 1.6) [43]. The resultant system is equivalent to a standard two-level inverter driven with a switching frequency  $N_b$ -fold times higher (same finding shown in 1.2.2) and equivalent line parameter  $N_b$  times lower (Figure 1.7). An equivalent circuit based on computations made on the Staimnetz domain is found (Figure 1.9).

Figure 1.5: Generic phase block legs averaged on a switching period

Driving PWM signals generation is not done having as a primary task the pole voltages generation but the DC link voltage stabilization. For the sake of simplicity, conduction and commutation losses are neglected. As visible in Figure 1.7, capacitor's current depends on either load  $(i_{IBC})$  and line currents (by mean of  $i_{DC}$ ). Each phase current is combination of legs' current joining the same point of common coupling.

$$i_k = \sum_{p=1}^{N_b} i_{kp}$$

(1.1)

Figure 1.6: Generic phase block averaged on a switching period

Figure 1.7: Equivalent three phase inverter

each leg inside the same power block is driven using the same modulating signal. It is then possible consider each pole voltage equal if averaged on a switching period  $t_{sw}$ . Therefore it is possible state that:

$$v_k = v_{k1} = v_{k2} = v_{k3} = v_{kp} \tag{1.2}$$

Being  $v_k = m_k V_{DC}$ , (1.2) can be rewritten as:

$$m_k = m_{k1} = m_{k2} = m_{k3} \tag{1.3}$$

What state above can be easily seen by mean of the following power balance:

$$P_{IAR} = \sum_{k=a}^{c} \sum_{p=1}^{3} v_{kp} i_{kp} = \sum_{k=a}^{c} v_k i_k = V_{DC} i_{DC} = V_{DC} (i_C + i_{IBC}) = P_C + P_{IBC} \quad (1.4)$$

deviding each term by  $V_{DC}$ :

$$\sum_{k=a}^{c} m_k i_k = i_{DC} = i_C + i_{IBC} \tag{1.5}$$

where  $v_{kp}$  are pole voltages,  $v_k$  phase block equivalent pole voltages,  $i_k$  line currents and  $i_{kp}$  legs currents. Moreover,  $m_k$  blocks' duty cycle,  $V_{DC}$  bus DC voltage,  $i_C$ capacitor's current and finally  $i_{IBC}$  buck power stage input current. Letters k and p are respectively referring to phases denomination a, b and c and legs numbering 1, 2 and 3. Instead of finding a proper PWM able to generate  $i_{DC}$ , the control criteria is to keep constant (on a switching period base)  $V_{DC}$ . Having a constant DC link voltage is equivalent to state that  $i_C$  and  $P_C$  are both nulls. Indeed:

$$P_{C} = \frac{\mathrm{d}W_{C}}{\mathrm{d}t} = \frac{\mathrm{d}}{\mathrm{d}t}(\frac{1}{2}CV_{DC}^{2}) = \frac{1}{2}CV_{DC}\frac{\mathrm{d}V_{DC}}{\mathrm{d}t}$$

(1.6)

Condition (1.6) ensures the maximum transfer of power between IAR and IBC. Neglecting losses it can be written as:

$$P_{IAR} = P_{IBC} \tag{1.7}$$

#### Voltage Oriented Control

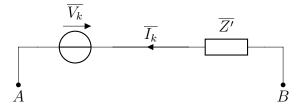

The actual control is carried out on a synchronous system (Park's framework) [44]– [46]. However, to compute needed space vectors, an equivalent circuit for each phase is necessary. Taking advantage of (1.2) it is possible to replace each leg pole voltage with an independent voltage source equal to  $v_k$ . In this way, one could immediately see that each phase power block can be decoupled from the others. Indeed, following statements refer to a generic power block ( $N_b$  legs) of the generic phase k. Furthermore, being the front end side of the AR operating on a sinusoidal regime, all the quantities are treated as phasors and impedances. In Figure 1.9, the

Figure 1.8: System in the Steinmetz domain

equivalent Thèvenin bipole of the circuit in Figure 1.8 has been depicted. Where:

Figure 1.9: Thèvenin equivalent circuit

$$\overline{V_k} = \frac{\sum_{p=1}^{N_b} \frac{\overline{V_{kp}}}{\overline{Z}}}{\sum_{p=1}^{N_b} \frac{1}{\overline{Z}}} = \frac{1}{N} \sum_{p=1}^{N_b} \overline{V_{kp}}$$

(1.8)

$$\overline{Z'} = \frac{1}{\sum_{p=1}^{N_b} \frac{1}{\overline{Z}}} = \frac{\overline{Z}}{N_b} = \frac{R+j\omega L}{N_b} = R' + j\omega L'$$

(1.9)

That is like have a standard three-phase AR with Z' = Z/3, L' = L/3 and R' = R/3. It must be noticed how (1.8) provides the same equality of (1.3).

Having depicted the whole AC/DC as in Figure 1.7 makes possible use it in the same way as it would have been an inverter. Indeed, in order to keep  $V_{DC}$  constant, a three-phase set of sinusoidal voltages is computed.

By means of space vector representation, it is possible to represent the three phases quantities as vectors. Starting from (1.10), it is possible firstly get (1.11) in the Clarke's framework and then obtain (1.12) in Park's synchronous framework.

$$\frac{L}{3}\frac{\mathrm{d}i_k(t)}{\mathrm{d}t} + \frac{R}{3}i_k(t) = L'\frac{\mathrm{d}i_k(t)}{\mathrm{d}t} + R'i_k(t) = V_{gk} - v_k \tag{1.10}$$

$$L'\frac{\mathrm{d}\overline{I}^s}{\mathrm{d}t} + R'\overline{I}^s = \overline{V_g}^s - \overline{V}^s \tag{1.11}$$

$$L'\frac{\mathrm{d}\overline{I}}{\mathrm{d}t} + j\omega L'\overline{I} + R'\overline{I} = \overline{V_g} - \overline{V}$$

(1.12)

It is possible project (1.12) into the *d* and *q* axis, respectively real and imaginary axes of the Argand-Gauss' plane:

$$L'\frac{\mathrm{d}I_d}{\mathrm{d}t} - \omega L'I_q + R'I_d = V_{gd} - V_d \tag{1.13}$$

$$L'\frac{\mathrm{d}I_q}{\mathrm{d}t} + \omega L'I_d + R'I_q = V_{gq} - V_q \tag{1.14}$$

it must be pointed out that if the *d*-axis takes as reference the grid voltage space vector happens that  $V_{gkq} = 0$  and therefore  $|\overline{V_{gk}}| = V_{gkd}$ . Introducing internal voltages  $u_d$ , and  $u_q$ .

$$u_{d} = L' \frac{\mathrm{d}I_{d}}{\mathrm{d}t} = V_{gd} + \omega L' I_{q} - R' I_{d} - V_{d}$$

(1.15)

$$u_q = L' \frac{\mathrm{d}I_q}{\mathrm{d}t} = V_{gq} - \omega L' I_d - R' I_q - V_q \tag{1.16}$$

In steady state both internal voltages are equal to zero. Neglecting voltage drop on R', it is possible to state:

$$I_d \approx \frac{V_d - V_{gd}}{\omega L'} \tag{1.17}$$

$$I_q \approx \frac{V_q - V_{gq}}{\omega L'} \tag{1.18}$$

that yields to:

$$\overline{V_g} \approx j\omega L'\overline{I} + \overline{V} \tag{1.19}$$

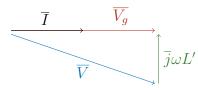

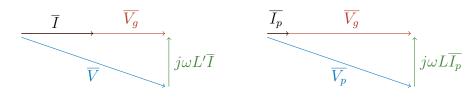

Complex relation (1.19) has been drawn in Figures 1.10 and 1.11 rispectively as vector diagram and equivalent circuit. Having defined an equivalent circuit with new

Figure 1.10: Park's framework vector diagram with unitary power factor

Figure 1.11: Park's framework equivalent circuits for either phases (left) and legs (right) quantities

variables (R' and L') does not provide any change on the voltage vector diagram. Moreover, writing line equations referring to each p leg (employing L, using (1.2) and setting  $\overline{I_{kp}} = \overline{I_k}/3$ ) shows the equivalence between (1.20) and (1.19). In Figure 1.12 both voltage diagrams are depicted.

$$\overline{V_g} \approx j\omega L\overline{I_p} + \overline{V_p} = 3\frac{j\omega L'\overline{I}}{3} + \overline{V_p} = j\omega L'\overline{I} + \overline{V}$$

(1.20)

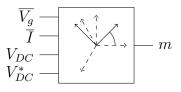

In order to rebalance  $V_{DC}$  voltage is necessary to drain a proper amount of grid active power. Since no reactive power is involved, it is preferable having an unitary input power factor. It is possible to demonstrate that active power  $P_g$  and reactive power  $Q_g$  are respectively proportional to  $I_d$  and  $I_q$ . Following what state above, the reference value  $I_q^*$  is set to zero. Meanwhile,  $I_d^*$  is generated with the task to provide the desired  $V_{DC}^*$ . In Figure 1.13, IAR voltage oriented control scheme is depicted. The  $I_d^*$  is computed by mean of a Proportional–Integral Controller (PI) that compensates the voltage error on the DC link. Internal voltages  $u_d$  and  $u_q$  are computed by mean of another couple of PI controllers with the task to compensate the displacements on  $I_d$  and  $I_q$ . Once  $u_d$  and  $u_q$  have been computed, (1.21) and (1.22) provide the AR front end voltage components  $V_d$  and  $V_q$ . The set of voltages  $V_k$  is ready to be used for generating the  $N_b$  modulating signals (in the current topology there are 3 modulating signals for each phase).

$$V_d = V_{qd} - u_d - R'I_d + \omega L'I_q \tag{1.21}$$

$$V_q = V_{gq} - u_q - R'I_q - \omega L'I_d$$

(1.22)

The system quantities used for the computation are  $V_{DC}$ ,  $I_d$ ,  $I_q$ ,  $V_{gd}$ , and  $V_{gq}$ . Most of them are expressed in the Park's reference frame and therefore grid voltage angle  $\theta$  is necessary. IAR's voltage oriented control mask depicted in Figure 1.14 have been introduced in the general scheme of Figure 1.15.

Figure 1.12: Park's framework vector diagrams for either phases (left) and legs (right) quantities

$$V_{DC}^{*} \longrightarrow \stackrel{+}{\longrightarrow} \stackrel{PI}{\longrightarrow} \stackrel{+}{\longrightarrow} \stackrel{PI}{\longrightarrow} \stackrel{+}{\longrightarrow} \stackrel{V_{gd}}{\longrightarrow} \stackrel{+}{\longrightarrow} \stackrel{+}{\longrightarrow} \stackrel{-}{\longrightarrow} \stackrel{+}{\longrightarrow} \stackrel{-}{\longrightarrow} \stackrel{-}{\longrightarrow} \stackrel{+}{\longrightarrow} \stackrel{-}{\longrightarrow} \stackrel{-}{\longrightarrow}$$

Figure 1.13: IAR voltage oriented control

#### Minimum DC Link Voltage Computation

In chapter 2 a control strategy able to provide  $V_{DC}^*$  is explained. However, the minimum DC bus voltage  $V_{DCm}$  depends on the grid voltage. In order to avoid the turning on of the diodes during inverter operations, it is necessary a proper value of  $V_{DC}$ . In the following, an analytical treatment is provided. In order to avoid legs' short circuits, upper and lower switches of each leg follow a complementary commutation scheme. It is then clear to notice that each upper switch of every leg can be turned on at the same time to one of the lower switches of the remaining legs without leading to short circuits. Referring to Figure 1.16, considering leg aupper switch  $S_1$ , it can be turned on when legs b or c lower switches (respectively  $S_5$  and  $S_6$ ) are turned on. In a similar way, the same criterion can be applied in the other way around considering one lower switch. The total number of not null possible commutation patterns is equal to six. Indeed, having three degrees of freedom (legs, a, b, and c) with two possible state, provides a total number of state combinations equal to  $2^3 = 8$ , of which two combinations are null. Are therefore necessary six systems of equations for describing the AR operations at any moment (neglecting null configurations). Moreover, it must be noticed that with the averaged method introduced above,  $N_b$  does not influence the number of possible combinations. Starting from diode turning off condition:

$$v_s \ge 0 \tag{1.23}$$

Considering commutation pattern involving  $S_1$  and  $S_5$  it is possible to state:

$$v_a = V_{DC} - v_{s1} \tag{1.24}$$

$$v_b = v_{s5} \tag{1.25}$$

computing the line to line pole voltage  $v_{ab} = v_a - v_b$ :

$$v_{ab} = V_{DC} - v_{s1} - v_{s5} \tag{1.26}$$

Figure 1.14: Active rectifier voltage oriented control mask

Figure 1.15: Voltage oriented control mask driving the IAR

replacing (1.26) in (1.23):

$$V_{DC} - v_{ab} = v_{s1} v_{s5} \ge 0 \tag{1.27}$$

rewriting (1.27):

$$V_{DC} \ge v_{ab} \tag{1.28}$$

in a similar way it is possible find the remaining conditions. Collecting everything together:

$$V_{DC} \ge v_{ab} \tag{1.29}$$

$$V_{DC} \ge v_{bc} \tag{1.30}$$

$$V_{DC} \ge v_{ca} \tag{1.31}$$

$$V_{DC} \le v_{ba} \to V_{DC} \le -v_{ab} \tag{1.32}$$

$$V_{DC} \le v_{cb} \to V_{DC} \le -v_{bc} \tag{1.33}$$

$$V_{DC} \le v_{ac} \to V_{DC} \le -v_{ca} \tag{1.34}$$

therefore, in any moment:

$$V_{DC} \ge max(|v_{ab}|, |v_{bc}|, |v_{ca}|) = 400\sqrt{2} \approx 566V$$

(1.35)

It must be noticed that  $V_{DCm}$  shown in Table 1.2 fully satisfy condition (1.35). Moreover, having chosen a Centered Pulse Width Modulation (CPWM) scheme, it could theoretically be possible generate sinusoidal waveform with a Root Mean Square (RMS) value of 230V without leading into over modulation distortion that it would have been with Sinusoidal Pulse Width Modulation (SPWM). Indeed:

$$v_{gk} = \frac{2}{\sqrt{3}} \frac{V_{DCm}}{2} = 400 \sqrt{\frac{2}{3}} \approx 230V \tag{1.36}$$

Figure 1.16: Three-phase inverter switch denomination

### IAR Ripple Computation

For what it concern legs input currents ripple, it is possible compute its amplitude according to [47]:

$$\Delta i_{ACM}^{l} = \frac{m}{4\sqrt{3}} \frac{V_{DC}}{Lf_{sw}} \tag{1.37}$$

where m is the modulating index.

From [41] it might be possible to state that a factor of about  $N_b$  reduces the total phase current ripple. Rewriting (1.37) considering the number of legs in each power block:

$$\Delta i_{ACM} \approx \frac{1}{N_b} \frac{m}{4\sqrt{3}} \frac{V_{DC}}{L f_{sw}} \tag{1.38}$$

Ripple reduction simulation introduced by IAR topology have been provided in section 4.1.

It is therefore evident that interleaving multiple legs provides an improvement on the input current ripple and can potentially bring to a reduction of the coupling reactors magnitude. From Table 1.2, it can be seen that  $V_{DC}$  ranges between  $V_{DCm} =$ 600V and  $V_{DCM} = 800V$ . Moreover, being *m* inversely proportional to the DC bus voltage, it can change during the operations according to the  $V_{DC}$  variation requested by the control strategy explained in chapter 2 [48]. Rewriting (1.37):

$$\Delta i^l_{ACM} \propto m V_{DC} \tag{1.39}$$

and being:

$$m = 2\sqrt{2} \frac{v_{gk}}{V_{DC}} \tag{1.40}$$

replacing (1.40) into (1.39):

$$\Delta i_{ACM}^l \propto 2\sqrt{2} \frac{v_{gk}}{V_{DC}} V_{DC} = 2\sqrt{2} v_{gk} \propto v_{gk} \tag{1.41}$$

it is possible to notice that the DC link voltage variation does not directly affects  $\Delta i_{ACM}$ . Conversely, in chapter 2 it is possible to notice how the DC bus voltage

floatability bring relevant improvement on both IBC's inductors' and total currents. However, as shown in (1.20) and depicted in Figure 1.12,  $\overline{V}$  and therefore  $v_{gk}$  depends on the current drained by the following IBC stage. Different charging profiles or State of Charge (SOC) can lead to a slightly (line parameters R and L lead to negligible voltage drops) different ripple amplitude on the AC side currents. Moreover, it is known that an active power variation meanly leads into a variation on the phase shift angle  $\phi$  between  $\overline{V}$  and  $\overline{V_g}$  and a negligible variation of the  $\overline{V}$  amplitude. Meanwhile, reactive power variations meanly lead to  $\overline{V}$  variations. Having set  $I_q^* = 0$  in section 1.1.1 leads to null steady state reactive power (steady state unitary power factor), and therefore  $\Delta i_{ACM}$  can be considered practically constant in any working condition. A ripple reduction is anyway introduced by the interleaving topology.

As said before, having interleaved  $N_b$  legs for each phase caused a  $V_{DC}$  pulses frequency rising of a factor  $N_b$ . It can be demonstrated that the voltage ripple on the bus DC is inversally proportional to  $N_b f_{sw}$ . As higher the number of power block staked together in the IAR is, as lower the voltage ripple is. A smaller capacitor voltage ripple brings to a lower Equivalent Series Resistance (ESR) energy dissipation and a longer capacitor life [30], [38].

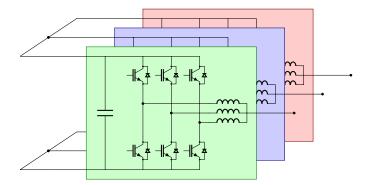

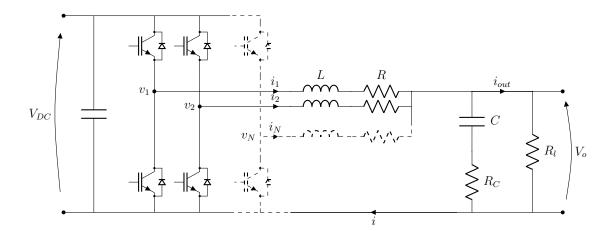

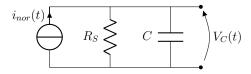

## 1.1.2 Interleaved Buck Converter

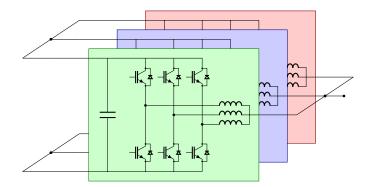

The DC/DC stage take advantage of the parallelization introduced by the interleaving connection. The power is evenly shared between the N IBC's legs. As visible in Figure 1.17, proposed IBC has three power blocks having three legs each one.

Figure 1.17: Interleaved Buck Converter

Furthermore, similarly to what emphasized in section 1.1, the usage of this configuration guarantees relevant ripple mitigation effects that are deeply discussed in the next sections [18], [31], [49].

The main task done by the IBC is to deliver at the battery the requested current or voltage. Charging procedures are carried out by means of multiple charging profiles. Each charging profile could be created by means of multiple charging methods properly scheduled. Some of the most common charging methods are:

- Constant voltage;

- constant current;

- tapper current;

- pulsed charge;

- burp charging;

- equalization charging;

- trickle charge;

- float charge;

- random charging.

and they can be carried out through multiple charging rates. Charging rates are usually classified into three main groups:

- Slow charge/Overnight;

- quick charge;

- fast charge.

Each of them has different features and may not be suitable for every batteries chemistry. Since the current proposal aims to provide fast charging rates for mainly Lithium-Ion batteries, constant voltage and current are the only methods considered in this work. However, it must be pointed out that pulse charge is getting increasing interest in the literature.

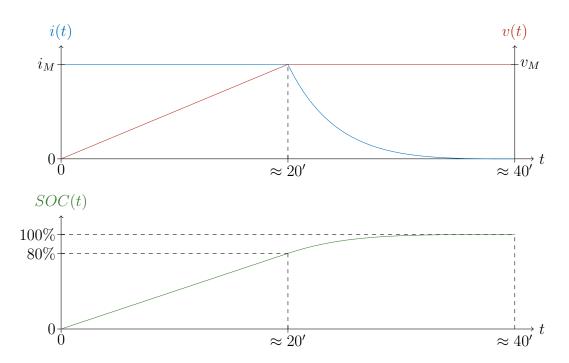

Constant Voltage (CV) and CC can be used for obtaining one of the most common charging profile, the CC-CV. It is constituted by a first charging period (bulk) where a constant current is fed inside the battery until battery voltage level reaches a cut off value. Once, the battery has reached the maximum voltage able to guarantee safe usage, the charging profiles switches from CC to CV charging method. In this last charging period where a constant voltage is provided to the battery (absorption), current decreases following a pseudo exponential profile until reaching the full charge condition. Many improvements have been introduced to previously showed charging scheme. Three-stage charging, differs from CC-CV profile, for having a further CV charging period called "floating". This new stage is able to maintain in time the full charge condition without leading to early aging and battery damages. In a similar way, four-stage charging introduces a fourth equalization stage with the task to remove chemicals products (for instance sulphation) from the battery plates surfaces, and it is mainly used for Lead-Acid chemistries.

As visible in Figure 1.18, CC bulky charging stage lasts until the battery SOC reaches a value of about 80%. The following CV stage provides the remaining 20% with times that may be comparable to the whole CC stage duration. The main task of automotive fast charging is to provide the highest quantity of charge in the shortest time possible. It is evident that (especially in a high usage scenario) the CV provides a relatively low quantity of charge in an unacceptable time. Furthermore, being the current billing politics carried out by EVSE authorities based on a "pay per charge" scheme, CV may lead to economic losses caused by a slow but time-consuming charging rate. Future politics may provide pricing tariffs made out of a mixed "charge and time" system able to encourage fast charge CC operations only.

As described in the introduction, fast charger level 4 can provide multiple hundred of kW. Being BEVs battery sizes ranging around 60/70kWh, charging times in the tens of minutes order of magnitude are possible. It is evident that charging rates ranging from 3C to 6C (charging from 10 minutes to 20 minutes) are needed.

Figure 1.18: CC-CV charging profile's (level 4) voltage, current and SOC evolution

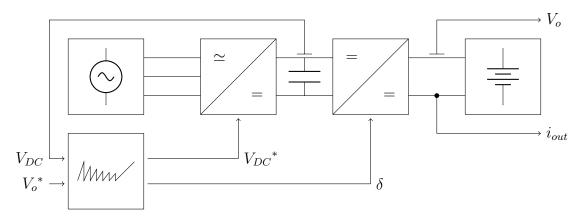

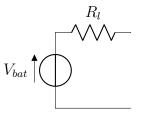

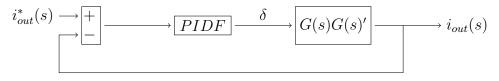

A proper control strategy is shown in chapter 3. A generic scheme showing the possible control loops with the necessary transducers is depicted in Figure 1.19. It is possible obtaining CC-CV profile either with current and voltage control loops. However, in order to have CV using a current loop is necessary in-depth knowledge of the battery model, similarly, for having CC using a voltage loop. Since charger could not know the battery status in term of SOC and State of Health (SOH), a transition from the current loop to voltage loop is usually done. In this way, a constant current can be quickly done throughout a current loop. Meanwhile, the voltage loop takes care of the constant voltage stage. Following the earlier mentioned reasons, in chapter 3 the control scheme has been implemented for a current control loop only.

In order to have an uniform power share (and therefore equal aging) among IBC's legs, it is necessary a proper current handling. Theoretically, being each leg identical to one another, the current would be evenly shared automatically. However, environmental, production, and aging conditions can lead to unbalance on legs. Unbalances could lead to an uneven current share. In order to deal with this issue, a rebalancing control system has been developed. One of the main features that the control system must have is the possibility to be easily scalable whenever a new power block is added. In chapter 3, multiple rebalancing strategy are described, and in Chapter 4 an example have been tested on one power block.

In subsection 1.2, a deep explanation of interleaved inherent ripple minimization and driving signal handling in the time domain is given. In order to further take advance of inductors size reduction in the DC/DC side, a control strategy able to provide a theoretically ripple-free condition in steady-state operations is presented in subsection 2.

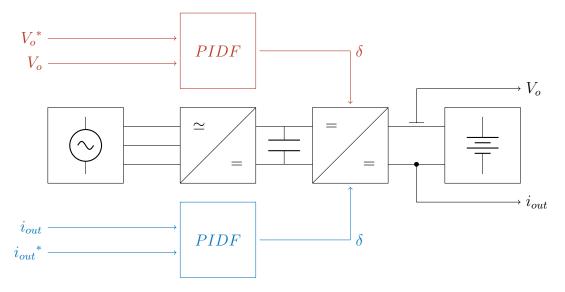

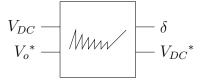

Figure 1.19: Possible voltage (red) and current (blue) control loops

# **1.2** IBC's Inherent Ripple Reduction

Multiple test have been done on lithium-based batteries with the target to understand the effect of high frequency components on battery aging. Chemical effects have not been fully understood. Multiple studies [50], [51] have emphasized that high frequency components does not produce appreciable battery capacity degradation. Meanwhile, low frequency components have been indicated as cause of a capacity decreasing of about 2% (especially on the early cycles). It is therefore evident that increase ripple frequency could mitigate the aging effects of this not yet fully known phenomena. However, it have also been shown that when high currents and temperatures are involved, new chemical processes might take places and provide an early battery degradation even for high frequency ripple components [52], [53].

As explained below, interleaved configurations, if properly driven, can lead to effective switching frequency increase proportional to the number of legs involved. However, ripple minimization may helps on mitigating the negative effects that an high power (high temperatures and currents involved) fast charging operations may introduce. In order to face aforementioned issues, a ripple-free strategy able to take advantage of the interleaved topology have been developed in Chapter 2. Since no battery current ripple quality constraints have been published yet, short ripple transients have been tolerated.

In section below, care have been dedicated on understanding interleaved ripple inherent minimization (and frequency multiplication) carried out by interleaved topologies. Meanwhile in Chapter 2 a general ripple cancellation strategy is introduced.

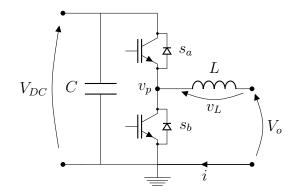

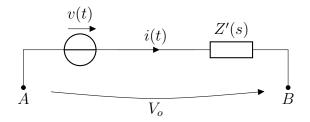

# **1.2.1** Current Ripple in Full Legs

Taking as a reference the full leg visible in the Figure 1.20, it can be easily seen from equation (1.42) that the inductor's voltage  $v_L$  depends on both  $v_p$  and  $V_o$ .

$$v_L = v_p - V_o \tag{1.42}$$

Figure 1.20: Full leg

where the pole voltage  $v_p$  can be set equal to 0 or  $V_{DC}$  and the output voltage  $V_o$  is defined as:

$$V_o = \delta V_{DC} \tag{1.43}$$

with  $\delta$  known as duty cycle.

The ripple amplitude can be easily computed by means of the physical relationship (1.44) characterizing inductors. Although the following approach represents a simplification that does not take into account the resistive component of the inductor, it can be seen as a linearization of the RL exponential transient on a span comparable to the switching period  $t_{sw}$  and therefore it does not introduce any relevant error on the ripple computation [54].

$$v_L = L \frac{\mathrm{d}i(t)}{\mathrm{d}t} \tag{1.44}$$

From the theory describing the PWM technique, the current i(t) flowing into the inductor can be described as the summation of two components, an average part I and a variable part  $\Delta i(t)$  usually called current ripple (1.45).

$$i(t) = I + \Delta i(t) \tag{1.45}$$

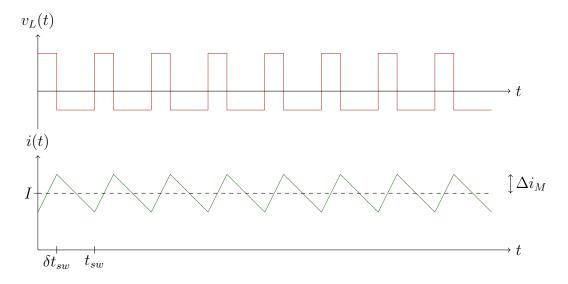

The derivative of the current i(t) depends on the sign of the voltage  $v_L$ . Figure 1.21 can be taken as an example. The typical sawtooth waveform is the outcome of the integration of  $v_L$  over a switching period  $t_{sw}$ . Referring to the time span ranging from 0 to  $\delta t_{sw}$ , where  $v_p = V_{DC}$ , the maximum current ripple can be easily computed with the following equation:

$$\Delta i_M = \frac{1}{2} \frac{\mathrm{d}i(t)}{\mathrm{d}t} \delta t_{sw} \tag{1.46}$$

by means of (1.42)-(1.44), equation (1.46) can be rewritten specifically showing the dependence on  $V_{DC}$ ,  $f_{sw}$ , L and  $\delta$ :

$$\Delta i_M = \frac{1}{2} \frac{v_L}{L} \delta t_{sw} = \frac{1}{2} \frac{V_{DC} - V_o}{L f_{sw}} \delta = \frac{1}{2} \frac{V_{DC}}{L f_{sw}} (1 - \delta) \delta$$

(1.47)

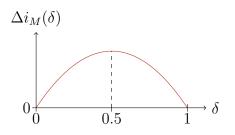

From (1.47) it is visible how  $\Delta i_M \propto (1 - \delta)\delta$  and therefore for any value  $\delta$  a multitude  $\Delta i_M$  values are expected. Furthermore, as visible in Figure 1.22, there is a geometrical symmetry for value above and below  $\delta = 0.5$ .

Figure 1.21: Drawing representing the ripple for  $\delta = 1/3$

Figure 1.22: Geometrical symmetry of  $\Delta i_M$  among the whole  $\delta$  span

## **1.2.2** Current Ripple in Interleaved Topologies

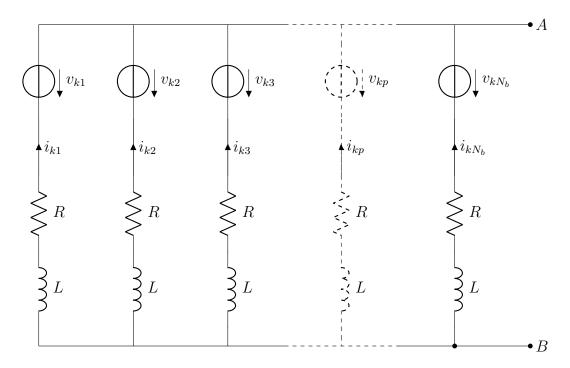

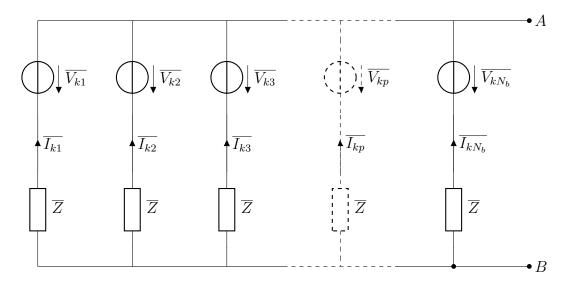

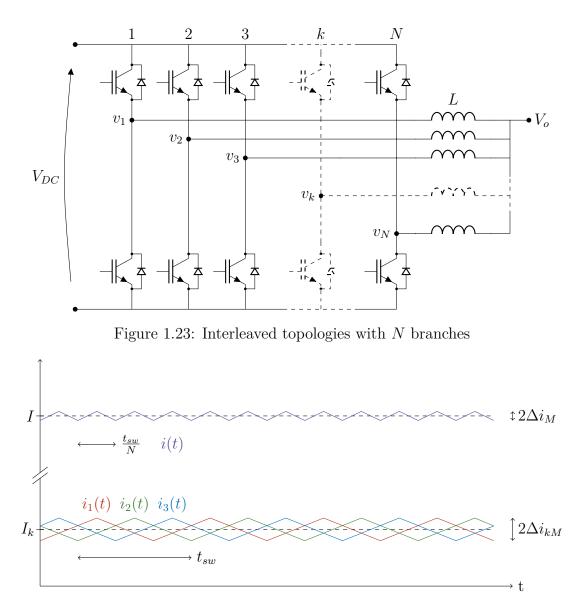

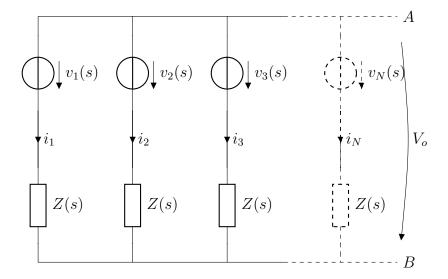

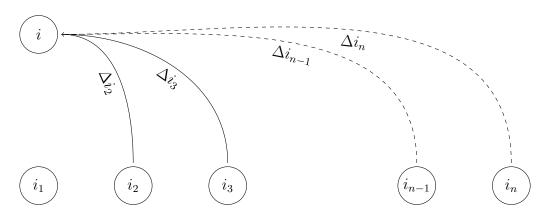

Interleaved topologies are built by mean of multiple full legs stacked in parallel to each other. A general case with N parallel branches has been considered (Figure 1.23).

As explained in Chapter 1, the possibility to share power among many branches by mean of proper routing of the total current through each full leg represents one of the benefits of using interleaved topologies. A further well-known advantage is the automatic ripple reduction obtained by mean of a suitable PWM carrier handling able to create a geometric total or partial compensation of the current ripple. The best choice is to evenly shift each PWM carrier by mean of a factor  $t_{sw}/N$  (360°/N if considered as a phase delay). Since the total current i(t) is the summation of all the branches' currents  $i_k(t)$ , also the output ripple  $\Delta i(t)$  is the summation of all the branches' ripple currents  $\Delta i_k(t)$ . The previous statement can be see in (1.48)-(1.52). Figure 1.24 provides a visual representation of the aforementioned phenomena considering  $\delta = 0.5$  and three branches only. Regardless from the number of parallel legs, the average output voltage  $V_o$  does not change in interleaved configurations, therefore, (1.43) is still valid.

$$i(t) = \sum_{k=1}^{N} i_k(t)$$

(1.48)

where each  $i_k(t)$  is constituted by an average value  $I_k$  and an instantaneous ripple

Figure 1.24: Shifted branches' currents  $i_k(t)$  and total outoput current i(t)

component  $\Delta i_k(t)$

$$i_k(t) = I_k + \Delta i_k(t) \tag{1.49}$$

and in a similar way i(t):

$$i(t) = I + \Delta i(t) \tag{1.50}$$

therefore,

$$I = \sum_{k=1}^{N} I_k \tag{1.51}$$

and,

$$\Delta i(t) = \sum_{k=1}^{N} \Delta i_k(t) \tag{1.52}$$

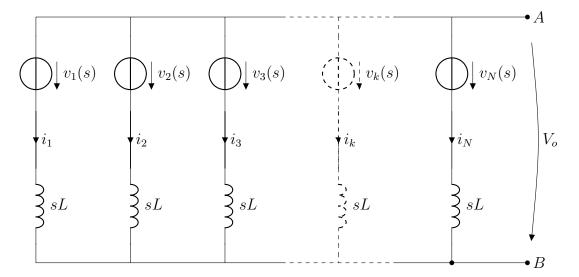

In order to compute a formula able to describe the maximum ripple  $\Delta i_M$  of an interleaved connection (similar to what done in (1.47)), an equivalent circuit is necessary. Substituting each full leg by mean of an independent voltage source able to generate  $v_k(t)$  and transforming the whole system on a Laplace domain (for the sake of simplicity no energy is stored inside inductors), the following circuit is obtained:

Figure 1.25: System in the Laplace domain

Thanks to Thévenin's and Millman's theorems the bi-nodal circuits can be massively simplified in a series of two elements v and  $Z_L$ .

$$v = \frac{\sum_{k=1}^{N} \frac{v_k(s)}{sL}}{\sum_{k=1}^{N} \frac{1}{sL}} = \frac{1}{N} \sum_{k=1}^{N} v_k(s) \quad \stackrel{\mathcal{L}^{-1}}{\to} \quad v(t) = \frac{1}{N} \sum_{k=1}^{N} v_k(t) \tag{1.53}$$

$$Z_L = \frac{1}{\sum_{k=1}^{N} \frac{1}{sL}} = s\frac{L}{N} = sL'$$

(1.54)

Once the system have been anti-transformed back it looks like what depicted in Figure 1.26. It is worth noticing that the Thévenin's equivalent voltage (1.53) is the mean value of the instantaneous pole voltages and the equivalent impedance (1.54) is based on an inductance L' that is N times lower than L.

Figure 1.26: Thèvenin equivalent circuit

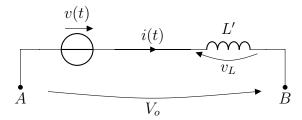

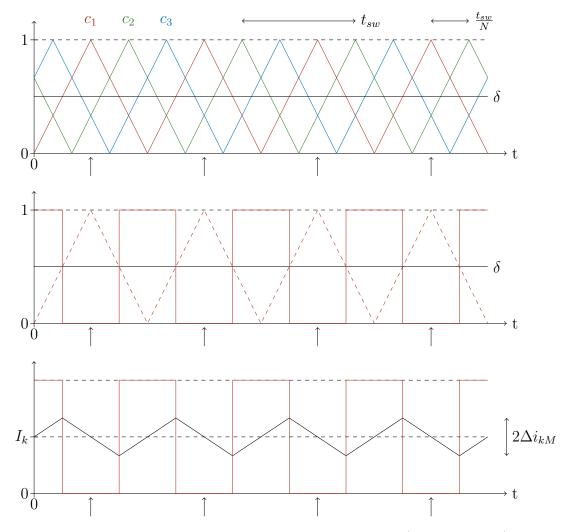

From the (1.43), (1.53), and knowing that each leg is fired with an even time delay of  $t_{sw}/N$  it is possible notice that the resulting v is a periodic signal of frequency  $Nf_{sw}$ . Therefore, it worth studying the system dividing the switching period  $t_{sw}$ in N time slots and introducing new conventional variables  $\delta'$ , L',  $f'_{sw}$  and  $t'_{sw}$ . Furthermore, since there is always a relationship between the active time  $t_{on}$  and  $\delta$ (being  $t_{on} = \delta t_{sw}$ ), it could be useful divide the duty cycle in N sectors each one identifiable by mean of a new index p. In the following subsections cases p = 1(Figure 1.27), p = 2 (Figure 1.28), and the general case p = p (Figure 1.29) are analyzed.

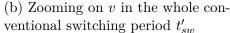

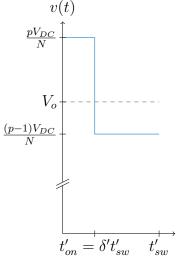

## Case p=1, $0 \le \delta \le 1/N$

As visible in Figure 1.27a the active period  $t_{on}$  of a generic pole voltage  $v_k$  falls inside the first time slot. The equivalent voltage v is a rectangular wave ranging within 0 and  $V_{DC}/N$  with a period  $t'_{sw}$ , it can therefore being study with an approach similar to what done in section 1.2.1. New variables must be defined:

$$t'_{sw} = \frac{t_{sw}}{N} \quad \longleftrightarrow \quad f'_{sw} = Nf_{sw} \tag{1.55}$$

$$t'_{on} = \delta' t'_{sw} = t_{on} = \delta t_{sw} \tag{1.56}$$

and therefore:

period  $t_{sw}$

$$\delta' = \frac{t'_{on}}{t'_{sw}} = N \frac{t_{on}}{t_{sw}} = N\delta$$

(1.57)

$$L' = \frac{L}{N} \tag{1.58}$$

$$V_o = \frac{V_{DC}}{N} \delta' = V_{DC} \delta \tag{1.59}$$

(a) Drawing of  $v_k$  and v in the whole switching (b) Zooming period t

Figure 1.27: Generic pole voltage  $v_k$  and equivalent voltage v for  $0 \le \delta \le 1/N$ (sector p = 1)

Rewriting the (1.47) with reference to the equivalent circuit and the active period  $t'_{on}$ :

$$\Delta i_M = \frac{1}{2} \frac{\mathrm{d}i(t)}{\mathrm{d}t} \delta' t'_{sw} = \frac{1}{2} \frac{v_{L'}}{L'} \delta' t'_{sw} = \frac{1}{2} \frac{1}{L' f'_{sw}} \delta' (\frac{V_{DC}}{N} - V_o) = \frac{1}{2} \frac{V_{DC}}{L' f'_{sw}} \frac{(1 - \delta') \delta'}{N} \quad (1.60)$$

It is worth noticing the direct proportionality with  $(1 - \delta')\delta'$  in a similar way to what previously emphasized in Figure 1.22. Substituting the new variable inside the (1.60):

$$\Delta i_M = \frac{1}{2} \frac{V_{DC}}{L f_{sw}} (1 - N\delta)\delta \tag{1.61}$$

Noticing that  $(1 - N\delta) \leq (1 - \delta)$ , it is already possible state that, as many legs are stacked in the converter as lower the output current ripple will be.

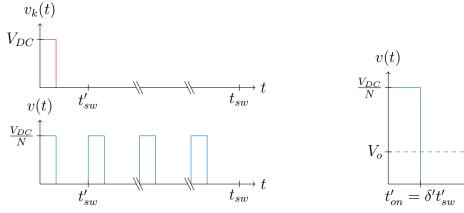

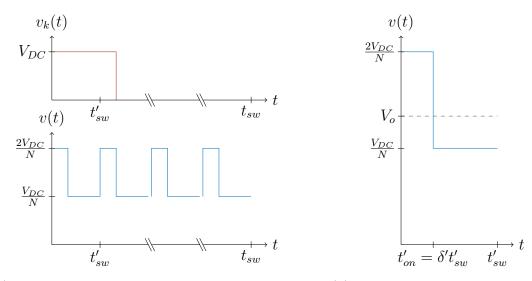

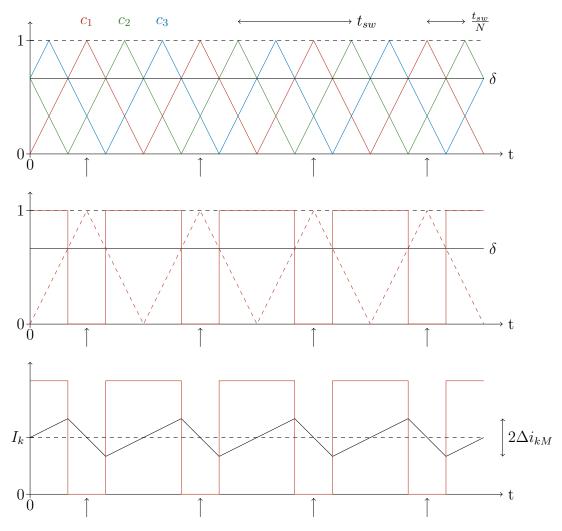

#### Case p=2, $1/N \le \delta \le 2/N$

As visible in Figure 1.28a the active period  $t_{on}$  of a generic pole voltage  $v_k$  falls inside the second time slot. The equivalent voltage v is a rectangular wave ranging within  $V_{DC}/N$  and  $2V_{DC}/N$  with a period  $t'_{sw}$ , it can therefore being study with an approach similar to what did in the previous case. Despite (1.55) and (1.58) are still valid, some changes are required:

$$t'_{on} = \delta' t'_{sw} = t_{on} - t'_{sw} = N\delta t'_{sw} - t'_{sw} = t'_{sw}(N\delta - 1)$$

(1.62)

and therefore:

$$\delta' = \frac{t'_{on}}{t'_{sw}} = N(\delta - \frac{1}{N}) \tag{1.63}$$

$$V_{o} = \frac{V_{DC}}{N}\delta' + \frac{V_{DC}}{N} = V_{DC}(\frac{\delta'}{N} + \frac{1}{N}) = V_{DC}\delta$$

(1.64)

(a) Drawing of  $v_k$  and v in the whole switching period  $t_{sw}$

(b) Zooming on v in the whole conventional switching period  $t'_{sw}$

Figure 1.28: Generic pole voltage  $v_k$  and equivalent voltage v for  $1/N \le \delta \le 2/N$ (sector p = 2)

Updating the (1.60) at the second case:

$$\Delta i_M = \frac{1}{2} \frac{1}{L' f'_{sw}} \delta' (2 \frac{V_{DC}}{N} - V_o) = \frac{1}{2} \frac{1}{L' f'_{sw}} \delta' \frac{V_{DC}}{N} (2 - \delta' - 1) = \frac{1}{2} \frac{V_{DC}}{L' f'_{sw}} \frac{(1 - \delta') \delta'}{N} \quad (1.65)$$

It is visible a perfect overlapping between the 1.60 and 1.65. Substituting the new variable inside the (1.65):

$$\Delta i_M = \frac{1}{2} \frac{V_{DC}}{L f_{sw}} [1 - N(\delta - \frac{1}{N})] (\delta - \frac{1}{N})$$

(1.66)

As expected, the 1.66 is similar to the 1.61 apart from the fact that  $\delta$  have being shifted by a value 1/N during the passage between the first and the second case.

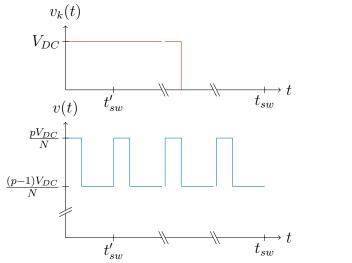

#### General case $p=p, (p-1)/N \le \delta \le p/N$

As visible in Figure 1.29a the active period  $t_{on}$  of a generic pole voltage  $v_k$  falls inside the generic *p*-th time slot. The equivalent voltage v is a rectangular wave ranging within  $(p-1)V_{DC}/N$  and  $pV_{DC}/N$  with a period  $t'_{sw}$ , it can therefore being study with an approach similar to what did in the previous cases. As done before, in order to compute the general case, few changes are required:

$$t'_{on} = \delta' t'_{sw} = t_{on} - (p-1)t'_{sw} = N\delta t'_{sw} - (p-1)t'_{sw} = t'_{sw}[N\delta - (p-1)]$$

(1.67)

and therefore:

$$\delta' = \frac{t'_{on}}{t'_{sw}} = N(\delta - \frac{p-1}{N})$$

(1.68)

$$V_o = \frac{V_{DC}}{N}\delta' + (p-1)\frac{V_{DC}}{N} = V_{DC}(\frac{\delta'}{N} + \frac{p-1}{N}) = V_{DC}\delta$$

(1.69)

Updating (1.60), and (1.65) to the general case:

(a) Drawing of  $v_k$  and v in the whole switching period  $t_{sw}$

(b) Zooming on v in the whole conventional switching period  $t'_{sw}$

Figure 1.29: Generic pole voltage  $v_k$  and equivalent voltage v for  $(p-1)/N \le \delta \le p/N$  (generic sector p = p)

$$\Delta i_M = \frac{1}{2} \frac{1}{L' f'_{sw}} \delta'(p \frac{V_{DC}}{N} - V_o) = \frac{1}{2} \frac{V_{DC}}{L' f'_{sw}} \frac{(1 - \delta')\delta'}{N}$$

(1.70)

Again, in the convectional reference system the general formula (1.70) perfectly matches (1.60), and (1.65). Finally, replacing the new variable inside the (1.70) the general formula (1.71) is found.

$$\Delta i_M = \frac{1}{2} \frac{V_{DC}}{L f_{sw}} [1 - N(\delta - \frac{p-1}{N})] (\delta - \frac{p-1}{N})$$

(1.71)

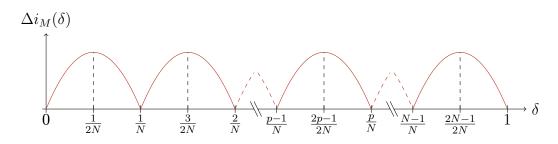

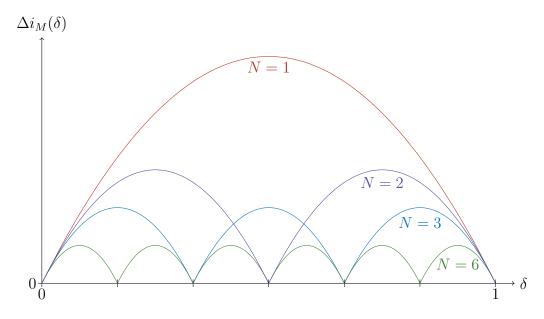

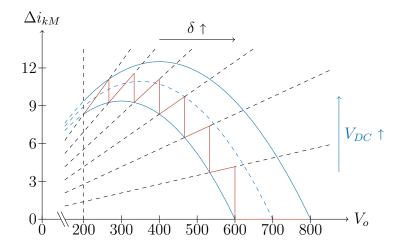

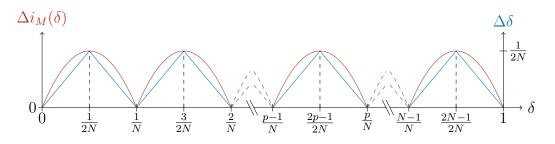

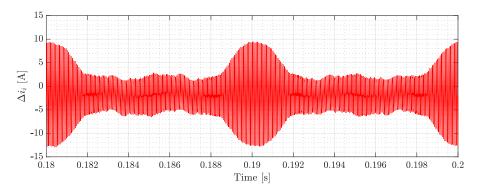

As stated in [55], [56] the current ripple is lower than what expected with a single leg and it has a repetitive simmetric parabolic behaviour among the whole  $\delta$  span, the number of lobes depends on the numbers of legs N (Figure 1.30).

Figure 1.30: Geometrical symmetry of  $\Delta i_M$  among the whole  $\delta$  span with a generic number N of legs

Figure 1.31: Geometrical symmetry of  $\Delta i_M$  among the whole  $\delta$  span for N = 1, 2, 3, and 6

As visible in (1.70), when  $\delta'$  is equal to 0.5,  $\Delta i_M$  reaches its maximum. Since the whole  $\delta$  span is constituted by N subsectors of  $\delta'$ , there are always N equal global maximums and they always occur in the middle of each lobe (Figures 1.30 and 1.31). Substituting in (1.70)  $\delta' = 0.5$ :

$$max\Delta i_M(\delta') = \Delta i_M(0.5) = \frac{1}{8} \frac{V_{DC}}{L' f'_{sw}} \frac{1}{N} \propto \frac{1}{N}$$

(1.72)

In order to quantitatively estimate the effectiveness of the output ripple reduction, the ratio r is introduced (1.73). It represents the ratio between the global maximum of output and inductors current ripples. Seeing the single leg k current as the output current of an improper interleaved with N = 1, it is easy state that r is inversely proportional to the number of legs N.

$$r = \frac{max\Delta i_M(\delta)}{max\Delta i_{kM}(\delta)} = \frac{1}{N}$$

(1.73)

Referring to Figure 1.31, it worth notice that every  $\delta/N$  the value of  $\Delta i_M(\delta)$  is equal to zero. In other terms, the general equation (1.71) has always N+1 roots and they represent the following operative conditions:

$$\delta = \frac{z}{N} \tag{1.74}$$

whereas z is an integer ranging between 0 and N.

Those operative conditions could theoretically guarantee a ripple null regardless from the switching frequency and inductors magnitude. In chapter 2 an original control strategy able to guarantee a ripple null at any working point is presented.

## Chapter 2

# **Ripple Free Strategy**

As anticipated in section 1.2, high frequency ripple may lead to an early aging in battery involved in high power charging operations [52], [53]. For this purpose a ripple cancellation strategy have been developed in this chapter. It is able to take advantage of inherent ripple minimization feature that interleaved topology introduces.

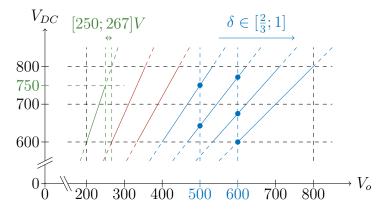

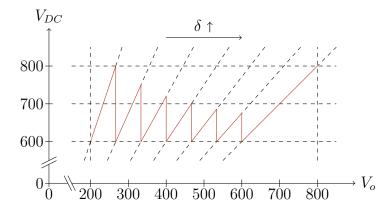

## 2.1 Ripple Free Strategy in the Proposed Case with 9 Legs

As visible in Figure 1.31 and cited in subsection 1.2.2, working points able to nullify  $\Delta i_M(\delta)$  are available. Equation (1.71) has always N + 1 roots and they represent the operative conditions visible in (1.74). Those working points could theoretically guarantee a ripple null regardless of the switching frequency and inductors magnitude.

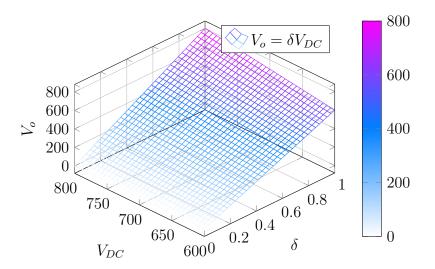

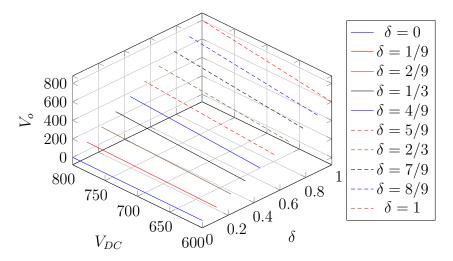

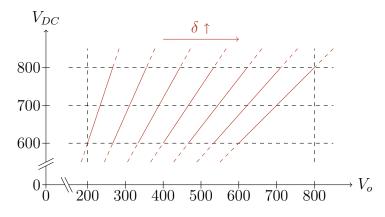

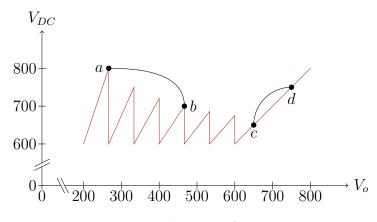

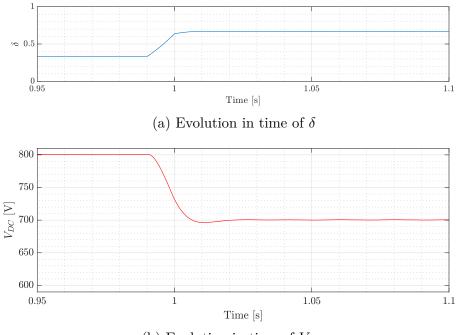

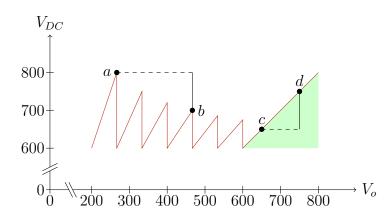

Equation (1.43) (rewritten in 2.1), is depicted in Figure 2.1. Meanwhile, in Figure 2.2 "no ripple" working points for the current case (N = 9) are highlighted.

$$V_o = \delta V_{DC} \tag{2.1}$$

In Figure 2.3, working points locus shown in equation 2.1 are depicted. Moreover, it is visible that design parameters shown in Table 1.2 limit the suitable working area between  $V_{DC} = [600; 800V]$  and  $V_o = [200; 800]V$ . It is therefore immediate see how not all the available discrete duty cycles are suitable. Since the maximum value of the DC link  $V_{DCM}$  is 800V and the minimum expected output value  $V_{om}$  is 200V the smallest duty cycle  $\delta_m$  is:

$$\delta_m = \frac{V_{om}}{V_{DCM}} = 0.25 \rightarrow 25\% \tag{2.2}$$

Meanwhile the maximum duty cycle is  $\delta_M = 1$  when  $V_o = V_{oM} = 800V$  and  $V_{DC} = V_{DCM} = 800V$ .

In the proposed DC/DC topology the number of legs N is equal to nine. Recalling the theory explained in part 1.2.2, the maximum ripple in the output current is N times lower than the single maximum ripple in each leg, indeed r = 1/9.

Figure 2.1:  $V_o$  as a function of  $\delta$  and  $V_{DC}$

Figure 2.2:  $V_o$  as a function of "no-ripple" discrete  $\delta$  and  $V_{DC}$

The possible discrete duty cycles are the one able to fulfill the (1.74), considering over mentioned boundary conditions:

$$\delta_m \le \frac{z}{N} \le \delta_M \tag{2.3}$$

therefore the integer z spans between 3 and 9.

#### 2.1.1 DC Link Voltage Variation Range

In previous paragraphs,  $V_{DC}$  range has been taken as given. However, it is not a freely settable parameter, it depends on the previous AC/DC stage capability, on the desired output voltage and the number of legs. As described in section 1.1.1, the interleaved active rectifier is tied up to the low voltage grid, and it is driven maximizing the DC BUS utilization using Interleaved Centered Pulse Width Modulation (ICPWM) (also known has Interleaved Space Vector Pulse Width Modulation (ISVPWM)) scheme. Analyzing the AC/DC stage with a positive power flow (G2V operations) it can be seen as a boost converter, and therefore the minimum DC voltage value cannot be lower than the double of the maximum value in the AC side

Figure 2.3: Projection of (2.1) on the plane  $V_o \times V_{DC}$  with reference to the studied case

$(V_{DCm}$  calculation discussed more in detail in part 1.1.1). Being each phase connected to the industrial voltage level (as visible in Table 1.2, European distribution grid has been considered) the line to line voltage  $V_g$  is set as 400V. The maximum phase to ground voltage is then:

$$V_{kM} = V_g \frac{\sqrt{2}}{\sqrt{3}} \approx 327V \tag{2.4}$$

taking into account the improvement of about 15% on DC link utilization garantee by the modulation scheme. The  $V_{DCm}$  must be:

$$V_{DCm} \ge 2\frac{V_{kM}}{\frac{2}{\sqrt{3}}} = 400\sqrt{2} \approx 566V$$

(2.5)

as visible the chosen value  $V_{DCm} = 600V$  fully respects the condition (2.5).

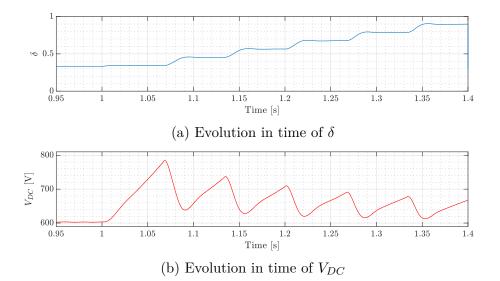

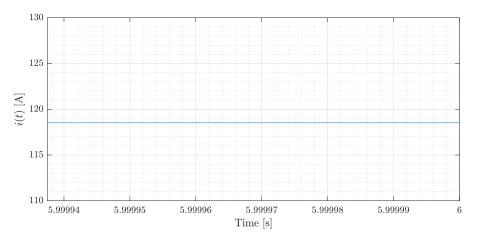

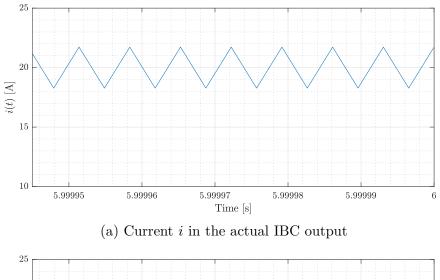

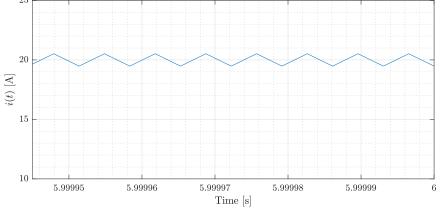

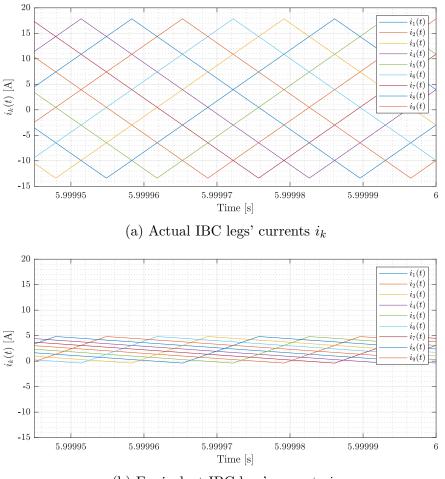

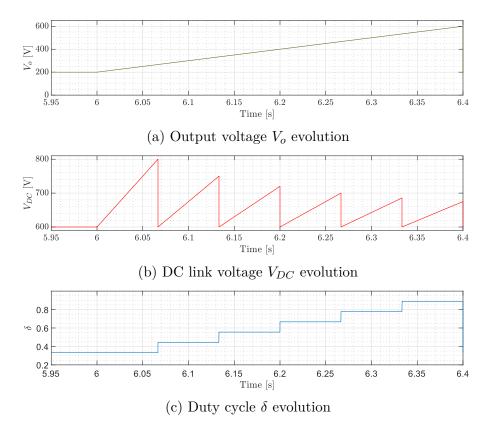

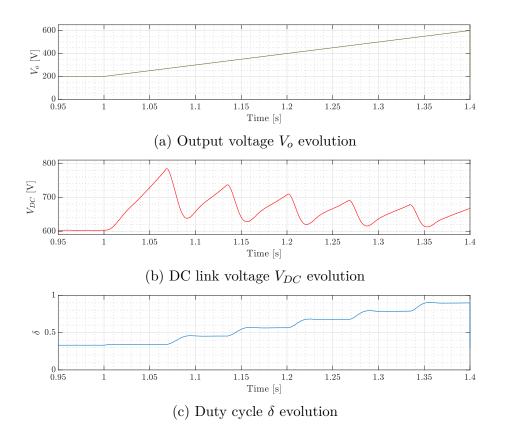

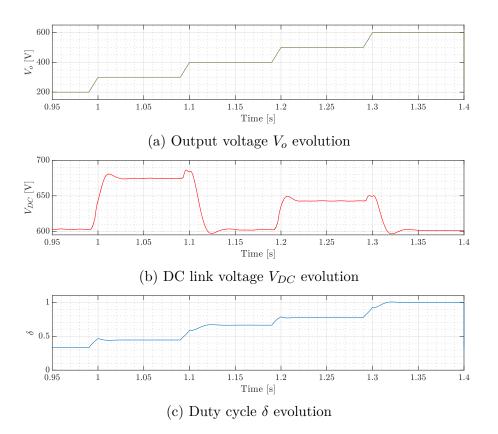

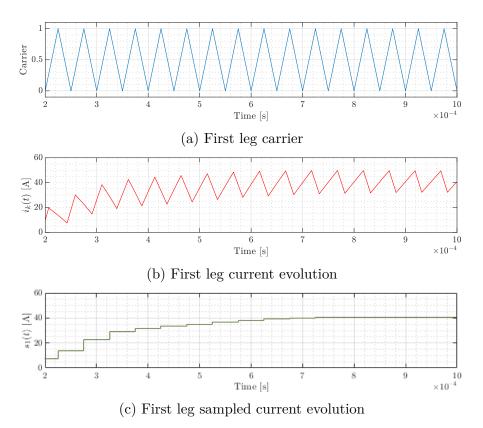

As can be seen in Figure 2.3, for every duty cycle  $\delta$  a range of working points can be found. They are limited between a minimum value when  $V_{DC} = V_{DCm}$  and a maximum value when  $V_{DC} = V_{DCM}$ .