## ALMA MATER STUDIORUM - UNIVERSITÀ DI BOLOGNA

#### SCUOLA DI INGEGNERIA E ARCHITETTURA

#### CORSO DI LAUREA MAGISTRALE IN INGEGNERIA ELETTRICA

Dipartimento di Ingegneria dell'Energia Elettrica e dell'Informazione "Guglielmo Marconi" - DEI

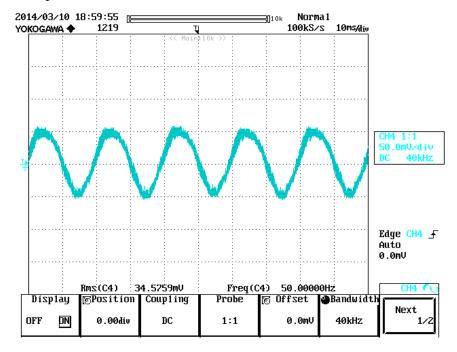

#### TESI DI LAUREA MAGISTRALE

in

Circuiti Elettronici di Potenza e Conversione Fotovoltaica dell'Energia M

# STUDIO E REALIZZAZIONE DI UN INVERTER TRIFASE A TRE LIVELLI

CANDIDATO RELATORE

Simone Nipoti Chiar.mo Prof. Gabriele Grandi

**CORRELATORI**

Dott. Jelena Loncarski Prof. Claudio Rossi

Anno Accademico 2012/2013

Sessione III

# **Indice**

| Inti | roduzione                                                     | 3  |

|------|---------------------------------------------------------------|----|

| Cap  | pitolo 1 – Tipologie di Inverter                              | 5  |

| 1.1  | Introduzione                                                  | 5  |

| 1.2  | Inverter a due livelli                                        | 7  |

|      | 1.2.1 Half Bridge                                             | 7  |

|      | 1.2.2 Full Bridge                                             | 9  |

|      | 1.2.3 Inverter trifase                                        | 11 |

| 1.3  | Inverter Multilivello                                         | 18 |

|      | 1.3.1 Generalità                                              | 18 |

|      | 1.3.2 Topologie circuitali                                    | 19 |

|      | 1.3.3 Applicazioni                                            | 33 |

| Cap  | pitolo 2 – Tecniche di Modulazione Multilivello               | 37 |

| 2.1  | Introduzione                                                  | 37 |

| 2.2  | PWM Multiportante                                             | 38 |

| 2.3  | Space Vector Modulation                                       | 43 |

| 2.4  | Centered PWM                                                  | 46 |

|      |                                                               |    |

| Cap  | pitolo 3 – Realizzazione di un Inverter Trifase a Tre Livelli | 55 |

| 3.1  | Introduzione                                                  | 55 |

| 3.2  | Moduli dell'inverter                                          | 56 |

|      | 3.2.1 Il progetto                                             | 56 |

|      | 3.2.2 Bus DC                               | 58  |

|------|--------------------------------------------|-----|

|      | 3.2.3 Gestione dei segnali di controllo    | 59  |

|      | 3.2.4 Modulo di potenza H-Bridge integrato | 61  |

| 3.3  | Alimentazione di potenza                   | 62  |

| 3.4  | Microcontrollore                           | 67  |

|      | 3.4.1 Architettura                         | 67  |

|      | 3.4.2 Controllo e codice                   | 69  |

| 3.5  | Scheda di trasmissione dei segnali ottici  | 73  |

| Cap  | oitolo 4 – Prove Sperimentali              | 75  |

| 4.1  | Introduzione                               | 75  |

| 4.2  | Sistema di prova                           | 76  |

| 4.3  | PWM Multiportante PD                       | 80  |

|      | 4.3.1 Programma del microcontrollore       | 80  |

|      | 4.3.2 Simulazione Simulink                 | 84  |

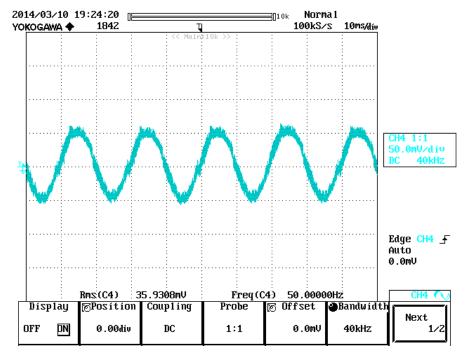

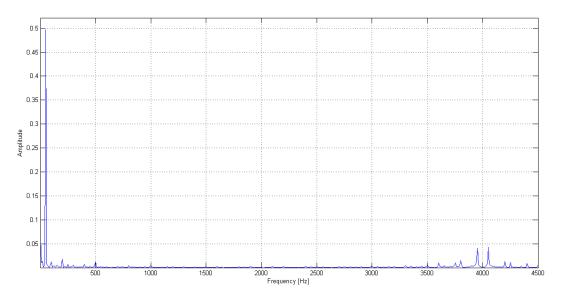

|      | 4.3.3 Risultati sperimentali               | 87  |

| 4.4  | PWM Multiportante PD Centered              | 89  |

|      | 4.4.1 Programma del microcontrollore       | 89  |

|      | 4.4.2 Simulazione Simulink                 | 92  |

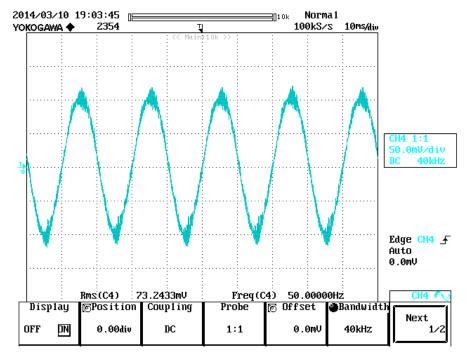

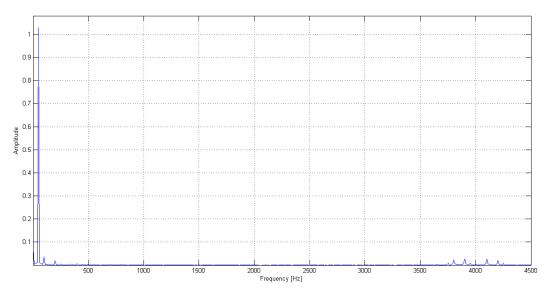

|      | 4.4.3 Risultati sperimentali               | 96  |

| 4.5  | Confronto THD correnti                     | 98  |

| Con  | nclusioni                                  | 107 |

| Alle | egato                                      | 109 |

| Bib  | liografia                                  | 111 |

## Introduzione

I convertitori elettronici di potenza sono utilizzati attualmente in numerose applicazioni. Queste possono spaziare a tutti i settori dell'industria moderna, dell'informatica, ma anche ad applicazioni domestiche, mediche, ecc.

"La nascita dell'elettronica di potenza viene fatta risalire all'invenzione dell'SCR (Silicon controlled rectifier) nel 1956. Da allora il settore è in rapida e continua evoluzione grazie allo sviluppo di dispositivi e tecniche in grado di soddisfare economicamente ed efficientemente ogni esigenza di mercato, sia in termini di potenza controllabile sia di velocità di attuazione, nel rispetto di obblighi normativi sempre più rigorosi e complessi." (cit. *Enciclopedia Treccani*)

La qualità dell'energia elettrica e l'efficienza energetica sono "must" che tutti i soggetti coinvolti (utilities, clienti finali, ...) devono raggiungere con soddisfacenti prestazioni, al fine rispettare le esigenze dei carichi e delle sorgenti di alimentazione.

Oltre a prescrizioni sull'efficienza energetica, la necessità di un elevato rendimento è legata anche al fatto che la potenza dissipata deve essere smaltita tramite idonei sistemi di raffreddamento, che risultano di norma ingombranti e costosi, e influenzano pertanto l'economicità e la compattezza dell'apparecchiatura.

L'ampio campo di potenze in gioco nelle applicazioni (da alcuni microwatt fino a molti megawatt), le differenziate caratteristiche delle sorgenti (tensioni da alcuni volt fino a centinaia di kilovolt, correnti tra alcuni nanoampere e centinaia di kiloampere)

e la varietà di esigenze specifiche dei carichi fanno sì che le tecnologie realizzative dei convertitori di potenza risultino assai differenziate anche nell'ambito di una stessa classe di convertitori.

E' all'interno di questo panorama che si colloca l'*inverter*. Esso nasce dall'esigenza di modificare la forma d'onda della tensione in tutte le sue caratteristiche (profilo dell'onda, ampiezza, frequenza) al fine di soddisfare le specifiche di alimentazione del circuito elettrico al quale l'inverter è collegato.

Esistono varie tipologie di inverter, che si differenziano per correnti e tensioni in gioco, topologie circuitali e tecniche di controllo. Ciascuna tipologia consente prestazioni più o meno adeguate a seconda delle specifiche sull'output, dei livelli di efficienza richiesti e del budget economico a disposizione.

Lo scopo di questa tesi è lo studio e la realizzazione di una specifica tipologia di inverter, l'inverter trifase a tre livelli di tipo Cascaded. Il primo capitolo descrive l'inverter a due livelli e quello multilivello, evidenziandone gli aspetti peculiari e le possibili applicazioni. Il secondo capitolo affronta nello specifico l'inverter a trifase a tre livelli, per il quale, nel terzo capitolo, ne è descritta una realizzazione pratica, costruita presso i laboratori del Dipartimento di Ingegneria Elettrica dell'Università di Bologna. Nel quarto capitolo vengono presentate alcune prove sperimentali effettuate sul sistema reale.

## Capitolo 1

## Tipologie di inverter

### 1.1 Introduzione

In questo capitolo si analizzano le principali tipologie di inverter, con particolare attenzione a una specifica architettura di tali convertitori: gli inverter multilivello.

Prima di elencare e descrivere le varie tipologie di inverter è necessario introdurre, per un inverter, il concetto di *livello di tensione*. Per livello di tensione si intende il valore della tensione in uscita da ciascun ramo: è noto infatti che questa non può assumere qualsiasi valore, ma solo valori discretizzati.

Gli inverter a tensione impressa tradizionali vengono comunemente denominati *a due livelli*, poiché tale è il numero di livelli di tensione disponibile in ogni ramo.

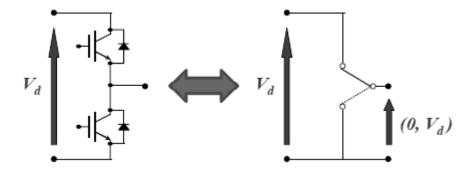

Figura 1.1 – inverter a due livelli

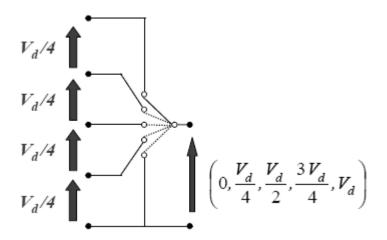

Quando invece il numero di livelli di tensione disponibile è maggiore di due, ecco che l'inverter prende il nome di *inverter multilivello*.

Figura 1.2 – inverter multilivello a cinque livelli

E' proprio per la natura discreta della tensione in uscita da ciascun ramo, che ciascuna tipologia di inverter dev'essere opportunamente controllata con specifiche tecniche di modulazione, al fine di ottenere sul carico la tensione voluta. Tali tecniche sono presentate in questo capitolo per gli inverter a due livelli, mentre per quelli multilivello è dedicato un capitolo a parte.

## 1.2 Inverter a due livelli

### 1.2.1 Half-Bridge

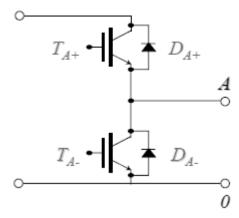

La struttura più semplice per un inverter a due livelli è costituita dall'inverter *Half-Bridge*, il cui circuito è realizzato come in figura seguente:

Figura 1.3 – inverter a due livelli Half-Bridge

Gli switch del convertitore sono realizzati tramite un IGBT con un diodo in antiparallelo, utile a creare una via alternativa per la corrente quando il carico è di tipo induttivo, prevenendo così la formazione di picchi di tensione che potrebbero danneggiare il transistor.

In generale, il comportamento del ramo dipende dal valore delle due tensioni di controllo (tensioni di gate) che vengono applicate ai due IGBT (in tutto 4 possibili combinazioni) e dal verso della corrente di carico. In realtà le combinazioni per le tensioni di gate che vengono utilizzate sono solo due, ovvero quelle che rendono indipendente il verso della tensione di carico (in figura 1.3,  $v_{A0}$ ) dal verso della corrente di carico. In questo modo la tensione di carico  $v_{A0}$  può assumere due valori:  $v_{A0}$ 0, dove  $v_{A0}$ 1 del valore della tensione continua disponibile sul bus di ingresso.

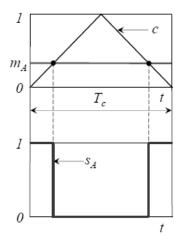

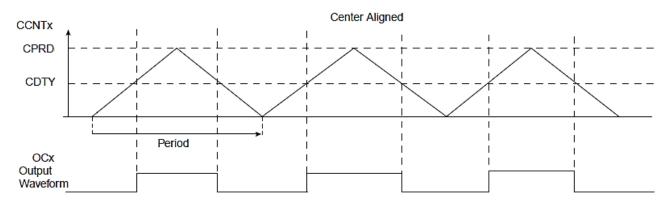

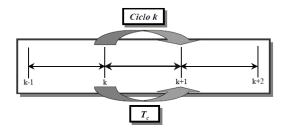

Il ramo di inverter può essere controllato utilizzando la tecnica di modulazione denominata PWM ( $Pulse\ Width\ Modulation$ ). Lo scopo della tecnica PWM è controllare il valore medio della tensione in uscita in un breve intervallo di tempo  $T_c$ , definito periodo di commutazione (approccio digitale).

Come si è visto il ramo può assumere solo due stati (stato On e stato Off) e quindi il suo comportamento può essere completamente descritto mediante una funzione binaria, la cosiddetta funzione di commutazione  $s_A$ .

La tensione istantanea d'uscita  $v_{A0}$  può essere facilmente correlata al valore istantaneo della funzione di commutazione mediante la seguente relazione:

$$v_{A0} = V_{dc} \cdot s_A \tag{1.1}$$

Lo scopo della tecnica PWM è, in ogni periodo di commutazione  $T_c$ , definire l'andamento nel tempo della funzione di commutazione  $s_A$  necessario per ottenere il desiderato valor medio della tensione d'uscita  $V_{A0,ref}$ .

Chiamando con  $v_{A0,m}$  il valor medio della tensione di uscita ( $v_{A0}$ ) e con  $m_A$  il valor medio della funzione di commutazione ( $s_A$ ), si ha la validità della seguente relazione:

$$v_{A0,m} = V_{dc} \cdot m_A \tag{1.2}$$

Pertanto, ponendo  $v_{A0,m}$  uguale a  $V_{A0,ref}$ , si ricava il valore del segnale modulante  $m_A$ , detto anche duty-cycle, compreso tra 0 e 1:

$$m_A = \frac{v_{A0,ref}}{V_{dc}} \tag{1.3}$$

La funzione di commutazione  $s_A$  è ricostruita intersecando il segnale modulante con un segnale portante c (triangolare) di ampiezza unitaria e periodo  $T_c$ .

Figura 1.4 – intersezione portante modulante

## 1.2.2 Full-Bridge

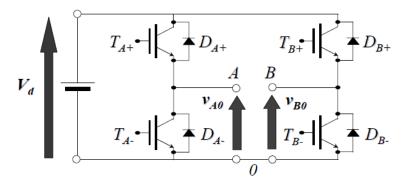

Un'evoluzione della configurazione Half-Bridge è il *Full-Bridge*, che, come si può notare dalla figura seguente, vede un raddoppio dei componenti, ovvero è costituito da due rami collegati in parallelo.

Figura 1.5 – inverter a due livelli Full-Bridge

Il carico è collegato tra i morsetti A e B di figura 1.5. Le tensioni di ramo, ovvero la tensione  $v_{A0}$  e  $v_{B0}$ , possono assumere, come precedentemente descritto per la configurazione Half-Bridge, solo due valori  $(0, V_{dc})$ . Pertanto si ha che la tensione sul carico  $(v_{AB} = v_{A0} - v_{B0})$  vale:  $0, V_{dc}, -V_{dc}$ .

Per questo motivo tale convertitore è chiamato anche *inverter monofase*, in quanto consente di trasformare energia elettrica di tipo continuo in energia elettrica di tipo alternato.

Anche in questo caso può essere applicata la modulazione PWM: lo scopo è determinare le funzioni di commutazione  $s_A$  ed  $s_B$  affinché il valore medio della tensione di carico  $v_{AB}$ , nell'intervallo di commutazione  $T_c$ , coincida con il valore di riferimento  $v_{AB,ref}$ . Vale che:

$$v_{AB,ref} = V_{dc} \cdot (m_A - m_B) \tag{1.4}$$

Imponendo  $m_A + m_B = 1$ , si ottengono i valori delle due modulanti:

$$m_A = \frac{1}{2} + \frac{v_{AB,ref}}{2*V_{dc}} \tag{1.5}$$

$$m_B = \frac{1}{2} - \frac{v_{AB,ref}}{2*V_{dc}} \tag{1.6}$$

Le funzioni di commutazione si ottengono sempre con l'intersezione portante modulante:

Figura 1.6 – intersezione portante modulante [1]

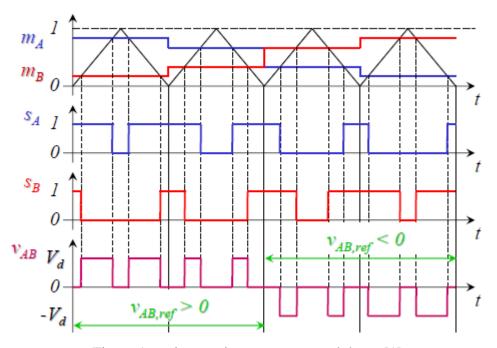

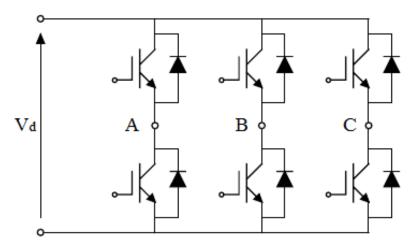

#### 1.2.3 Inverter trifase

La configurazione trifase a due livelli di tensione è ottenibile con il parallelo di tre rami. Tale configurazione merita una più attenta analisi in quanto può essere gestita con varie tecniche di modulazione, che verranno confrontate con quelle della configurazione trifase multilivello descritta nel Capitolo 2.

Figura 1.7 – inverter trifase a due livelli

Le tre tensioni di polo  $v_{A0}$ ,  $v_{B0}$ ,  $v_{C0}$  possono essere descritte utilizzando le funzioni di commutazione:

$$v_{A0} = s_A \cdot V_{dc} \tag{1.7}$$

$$v_{B0} = s_B \cdot V_{dc} \tag{1.8}$$

$$v_{C0} = s_C \cdot V_{dc} \tag{1.9}$$

A questo punto è opportuno introdurre i *vettori di spazio*, ovvero una diversa rappresentazione di tre grandezze indipendenti, omogenee e variabili nel tempo come possono essere tre generiche grandezze afferenti a un sistema trifase  $(x_1, x_2, x_3)$ .

Di seguito sono date le definizioni di *componente omopolare*  $(y_0)$  e di *vettore di spazio*  $(\underline{y})$ , necessarie per effettuare il passaggio al dominio dei vettori di spazio.

$$y_0 = \frac{2}{3} \cdot x_1 + x_2 + x_3 \tag{1.10}$$

$$y = \frac{2}{3} \cdot x_1 + x_2 \cdot \alpha + x_3 \cdot \alpha^2 \tag{1.11}$$

dove  $\alpha = e^{j2/3\pi}$

Applicando la (1.11) alle (1.7), (1.8), (1.9), si ottiene il vettore di spazio delle tensioni di polo:

$$v_p = \frac{2}{3}V_{dc} \cdot s_A + s_B \cdot \alpha + s_C \cdot \alpha^2 \tag{1.12}$$

Considerando un carico a stella applicato all'inverter e chiamando con N il suo centro stella, si dimostra che il vettore di spazio delle tensioni di polo  $(v_p)$  e quello delle tensioni di carico  $(v_c)$  sono uguali, ovvero vale  $v_c = v_p$ .

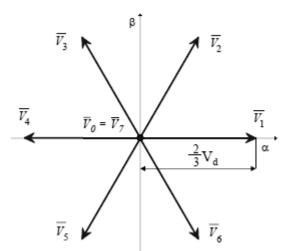

Pertanto, siccome le funzioni di commutazione  $s_A$ ,  $s_B$ ,  $s_C$  possono assumere solo i valori 0, 1, si ha che sono possibili  $2^3 = 8$  configurazioni degli interruttori dell'inverter.

Le due configurazioni (000), (111) vengono dette configurazioni *nulle*, le altre sei invece vengono dette *attive*. La figura seguente rappresenta in termini grafici le 8 possibili configurazioni:

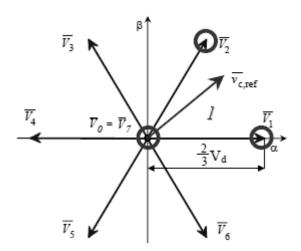

Figura 1.8 – vettori di spazio delle tensioni di carico

Attraverso le funzioni di antitrasformazione, si ricava che i possibili i livelli della tensione stellata di carico sono cinque:

$$-\frac{2}{3}V_{dc}$$

,  $-\frac{1}{3}V_{dc}$ , 0,  $\frac{1}{3}V_{dc}$ ,  $\frac{2}{3}V_{dc}$

Sulla base di quanto detto, è possibile definire una tecnica di modulazione che sfrutta il concetto di vettore di spazio. Tale tecnica è detta *SVM* (*Space Vector Modulation*).

#### **Space Vector Modulation**

Per implementare questa tecnica si fa riferimento al piano  $\alpha$ - $\beta$  dei vettori di spazio, nel quale viene individuato il vettore di spazio di riferimento delle tensioni di carico  $v_{c,ref}$ . Tale vettore assume un nuovo valore ad ogni periodo di commutazione  $T_c$ , che può essere visto pertanto come un periodo di campionamento. Lo scopo della tecnica SVM è quello di ottenere un vettore di spazio della tensione di carico il cui valor medio, nel periodo di commutazione  $T_c$ , coincida con il vettore di riferimento.

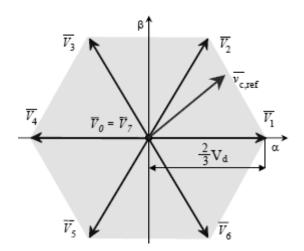

Per fare questo si divide il piano  $\alpha$ - $\beta$  in sei settori, delimitati dai vettori attivi, e il vettore di spazio della tensione di carico è ottenuto, ad ogni periodo di commutazione, combinando due vettori attivi adiacenti ed uno o due vettori nulli.

Figura 1.9 – tecnica SVM

E' possibile ricavare i tempi di applicazione di ciascun vettore a partire dalla seguente relazione:

$$v_{c,ref}T_c = V_x T_x + V_y T_y + V_z T_z (1.13)$$

Il rapporto tra il tempo di applicazione di ciascun vettore e il periodo di commutazione è detto *duty-cycle*. Vincoli di positività sui duty-cycle, impongono alcuni vincoli geometrici sul vettore di spazio delle tensioni di carico ottenibile. In particolare, se si vuole che il vettore di riferimento venga rispettato, questo deve rimanere all'interno dell'esagono delimitato dai vettori delle configurazioni attive.

Figura 1.10 – regione di validità per il vettore di riferimento

Pertanto, se il vettore di spazio di riferimento corrisponde, nel dominio del tempo, a un sistema di tre grandezze sinusoidali simmetriche, si dimostra che la loro ampiezza deve essere minore o uguale del raggio del cerchio inscritto nell'esagono di figura 1.10, che vale  $V_{dc}/\sqrt{3}$ .

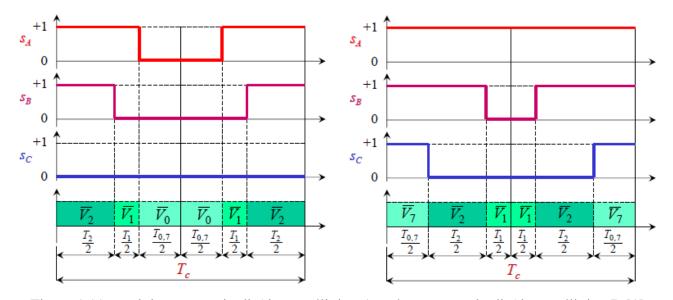

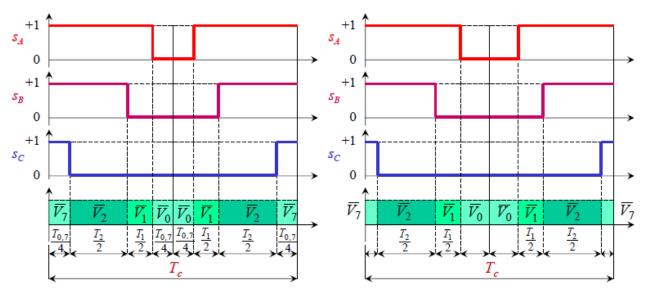

Esistono varie sequenze di applicazione dei vettori coinvolti nella modulazione. Qualsiasi siano queste sequenze, ci sono due vincoli da rispettare:

- la sequenza di commutazione deve prevedere solo una commutazione di ramo per ogni cambio di configurazione;

- la sequenza di commutazione deve essere speculare rispetto alla mezzeria del periodo di commutazione.

Il primo vincolo consente di limitare la frequenza di commutazione, che, come è noto, produce perdite; il secondo vincolo consente di ottenere un miglior spettro della tensione di uscita.

#### Le sequenze di commutazioni più usate sono:

- la 5 intervalli tipo A, che parte con una configurazione attiva, passa all'altra configurazione attiva e poi alla nulla di tipo 0 (0,0,0), infine ritorna indietro;

- la 5 intervalli tipo B, che parte dalla configurazione nulla 7 (1,1,1), passa alla configurazione attiva più vicina e poi all'altra attiva, infine ritorna indietro;

- la 7 intervalli simmetrica, che utilizza entrambe le configurazioni nulle e associa a esse il medesimo duty-cycle;

- la 7 intervalli generale, che utilizza entrambe le configurazioni nulle ma associa a esse un diverso duty-cycle.

Figura 1.11 – a sinistra esempio di 5 invervalli tipo A, a destra esempio di 5 intervalli tipo B [1]

Figura 1.12 – a sinistra esempio di 7 intervalli simmetrica, a destra esempio di 7 intervalli generale

#### PWM generalizzata

E' possibile estendere la tecnica PWM, presentata al paragrafo 1.2.2, all'inverter trifase. Pertanto questa tecnica, che prende ora il nome di PWM generalizzata, è basata sempre sul confronto portante modulante ed è in grado di consentire l'alimentazione del carico trifase con un vettore di spazio di tensione, il cui valor medio, nel periodo di commutazione, coincida con quello desiderato.

Considerando le relazioni di antitrasformazione e che ciascuna modulante è ottenuta come in formula (1.3), si ottengono le espressioni delle modulanti:

$$m_A = m_0 + \frac{1}{V_{dc}} v_{c,ref} \cdot 1 \tag{1.14}$$

$$m_B = m_0 + \frac{1}{V_{dc}} v_{c,ref} \cdot \alpha \tag{1.15}$$

$$m_C = m_0 + \frac{1}{V_{dc}} v_{c,ref} \cdot \alpha^2$$

(1.16)

dove m<sub>0</sub> rappresenta un grado di libertà.

Scegliendo in modo opportuno il valore di m<sub>0</sub>, si ottengono le stesse sequenze di commutazione viste nel paragrafo precedente. Pertanto è possibile dimostrare che la

PWM generalizzata porta agli stessi risultati della tecnica SVM, semplicemente impostando a ogni periodo di commutazione un valore opportuno di m<sub>0</sub>.

Per esempio, se si vuole ottenere la sequenza a 5 intervalli di tipo A, è necessario imporre un valore di  $m_0$  tale che la minore delle tre modulanti assuma valore nullo. In tal caso  $m_0$  vale:

$$m_0 = -\min\left[\frac{1}{V_{dc}}v_{c,ref} \cdot 1, \frac{1}{V_{dc}}v_{c,ref} \cdot \alpha, \frac{1}{V_{dc}}v_{c,ref} \cdot \alpha^2\right]$$

(1.17)

Se si vuole ottenere la sequenza a 5 intervalli di tipo B, è necessario imporre un valore di m<sub>0</sub> tale che la maggiore delle tre modulanti assuma valore unitario:

$$m_0 = 1 - \max[\frac{1}{V_{dc}} v_{c,ref} \cdot 1, \frac{1}{V_{dc}} v_{c,ref} \cdot \alpha, \frac{1}{V_{dc}} v_{c,ref} \cdot \alpha^2]$$

(1.18)

Se si vuole ottenere la modulazione a 7 intervalli simmetrica, è necessario imporre un valore di  $m_0$  tale che le modulanti risultino centrate nell'intervallo [0,1]:

$$m_0 = \frac{1}{2} [1 - \max \frac{1}{V_{dc}} v_{c,ref} \cdot 1, \dots - \min \frac{1}{V_{dc}} v_{c,ref} \cdot 1, \dots]$$

(1.19)

La traslazione rigida delle tre modulanti ha la proprietà di non modificare i tempi di applicazione delle configurazioni attive, ma va semplicemente a modificare la ripartizione del tempo di applicazione tra le configurazioni nulle.

## 1.3 Inverter multilivello

#### 1.3.1 Generalità

Come accennato nell'introduzione di questo capitolo, l'inverter multilivello consente di ottenere in uscita da ciascun ramo più livelli di tensione. Questo permette di ottenere una forma d'onda di tensione sul carico più simile alla forma d'onda di riferimento di quanto non si riesca a ottenere con un inverter a due livelli. Si hanno in uscita tensioni, e di conseguenza correnti, molto più simili alla forma d'onda sinusoidale, con livelli di distorsione armonica piuttosto bassi. Ciò offre due importanti vantaggi: la frequenza di commutazione può essere inferiore a quella di un inverter a due livelli, consentendo quindi di ridurre le perdite nel silicio, e la riduzione dei filtri d'uscita produce una diminuzione globale di dimensioni e costi. Inoltre non è da trascurare il vantaggio in termini di riduzione della sollecitazione dielettrica sul sistema carico: infatti, avendo a disposizione più livelli di tensione, si riduce il dv/dt, ovvero il "salto" di tensione tra una commutazione e l'altra. Questo porta a una minor sollecitazione sugli isolanti del carico e alla riduzione di problemi di compatibilità elettromagnetica (EMC).

Le configurazioni topologiche tipiche del multilivello portano inoltre a ottenere una tensione di uscita superiore, in termini di ampiezza, di quella che si otterrebbe con un inverter a due livelli alimentato con lo stesso bus in continua. O ugualmente, a parità di ampiezza della tensione sul carico, gli interruttori di potenza risultano sottoposti a una tensione minore, pertanto possono essere ridimensionati.

"Gli inverter multilivello appartengono alla famiglia dei convertitori per medie tensioni e grandi potenze, considerando che per i convertitori industriali la media tensione va da 2.3 a 6.6 kV e le grandi potenze da 1 a 50 MW". [2]

Riassumendo, i principali vantaggi dell'inverter multilivello sono:

- minore distorsione della tensione sul carico;

- frequenze di commutazioni più basse;

- minori costi derivanti da filtri passivi/attivi;

- minore sollecitazione sugli isolanti del carico;

- minori problemi di EMC;

- ampiezza della tensione di uscita superiore/interruttori meno costosi.

L'uso di inverter multilivello rappresenta quindi un modo di migliorare l'efficienza e la qualità di conversione dell'energia.

Per contro gli inverter multilivello presentano anche degli svantaggi. Il primo di tutti è il raddoppio dei componenti: questo può causare un costo e un ingombro del sistema maggiore rispetto a un due livelli. Un altro svantaggio è rappresentato dalle tecniche di modulazione che risultano più complicate e più onerose in termini computazionali per un processore.

## 1.3.2 Topologie circuitali

Negli ultimi due decenni sono state proposte molte tipologie circuitali per gli inverter multilivello. Quelle che si sono maggiormente affermate sono:

- Diode-clamped Inverter (o Neutral-Point-Clamped, NPC)

- Capacitor-clamped Inverter (o Flying-Capacitor)

- Cascaded H-Bridge Inverter

La tecnologia multilivello è nata, alla fine degli anni '60, con il concetto di forma d'onda multilivello a gradini di un convertitore cascaded H-Bridge, a cui ha fatto

seguito, nel corso degli anni '70, lo sviluppo della tecnologia Capacitor-clamped e Diode-clamped. Quest'ultima è considerata la prima tipologia di inverter multilivello realizzata per applicazioni di media tensione.

#### **Diode-clamped Inverter**

Questa tipologia di convertitore multilivello si distingue per l'impiego dei diodi di *clamping*, che hanno l'importante compito di bloccare la tensione inversa ai capi delle capacità del bus dc. Il punto neutro (da cui il nome alternativo *Neutral Point Clamped*) al quale si fa riferimento per le d.d.p. (differenze di potenziale) è il nodo comune centrale dei condensatori del bus-dc.

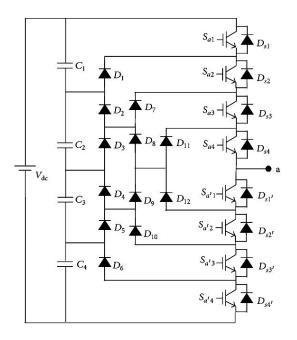

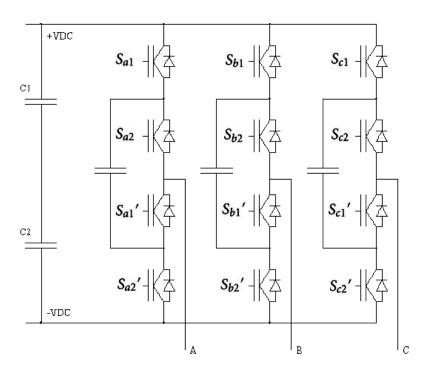

Figura 1.13 – Diode Clamped Inverter a 5 livelli

Indicando con m il numero di livelli di tensione desiderati, per realizzare il convertitore sarà necessario un bus de composto da m-1 condensatori, 2·(m-1) dispositivi di commutazione e (m-1)·(m-2) diodi di clamping. Incrementando il numero dei livelli di tensione, la qualità della tensione di uscita aumenta e la forma d'onda di tensione diventa più simile a quella sinusoidale.

Per un inverter a 5 livelli, la tensione di uscita e i corrispondenti stati degli switch sono riportati nella seguente tabella:

| Output V               | Switch state |          |          |          |           |           |           |           |

|------------------------|--------------|----------|----------|----------|-----------|-----------|-----------|-----------|

| Output V <sub>ao</sub> | $S_{a1}$     | $S_{a2}$ | $S_{a3}$ | $S_{a4}$ | $S_{a'1}$ | $S_{a'2}$ | $S_{a'3}$ | $S_{a'4}$ |

| $V_5 = V_{\rm dc}/2$   | 1            | 1        | 1        | 1        | 0         | 0         | 0         | 0         |

| $V_4 = V_{\rm dc}/4$   | 0            | 1        | 1        | 1        | 1         | 0         | 0         | 0         |

| $V_3 = 0$              | 0            | 0        | 1        | 1        | 1         | 1         | 0         | 0         |

| $V_2 = -V_{\rm dc}/4$  | 0            | 0        | 0        | 1        | 1         | 1         | 1         | 0         |

| $V_1 = -V_{dc}/2$      | 0            | 0        | 0        | 0        | 1         | 1         | 1         | 1         |

Tabella 1.1 – stato degli switch e corrispondenti tensioni per l'inverter di Fig. 1.13

E' molto importante dimensionare opportunamente i diodi di clamping, poiché sono chiamati a sopportare diversi valori di tensione a seconda di quanti condensatori del bus de sono collegati a essi.

Uno degli aspetti più delicati di questa configurazione circuitale è il bilanciamento delle tensioni sulle capacità del bus dc. Infatti vi è la presenza di una corrente che produce una variazione delle tensioni sui condensatori e quindi una variazione del potenziale del punto 0. Tale corrente è presente solo nello stato 0 e coincide con la corrente di carico.

Questo comportamento può rappresentare un problema se la corrente di carico è continua (unidirezionale); allora, per non incorrere nello scaricamento dei condensatori, è necessario evitare l'impiego dello stato 0 (perdita di un livello). Se la corrente di carico è invece alternata (bidirezionale), per simmetria si avrà una oscillazione delle tensioni sui condensatori d'ingresso, che sarà tanto più ampia, quanto più piccolo sarà il valore della frequenza ed il valore della capacità.

Di seguito una illustrazione dei collegamenti circuitali utili al fine di ottenere una configurazione Diode-clamped trifase a tre livelli:

Figura 1.14 – Diode Clamped Inverter trifase a 3 livelli

Si vede dalla figura 1.14 che è possibile ottenere la configurazione trifase semplicemente collegando insieme il punto di neutro di tre strutture Diode-clamped monofase.

La configurazione trifase consente di sfruttare gli stati ridondanti che caratterizzano tale configurazione per migliorare il bilanciamento delle tensioni sui condensatori d'ingresso (vedi figura seguente).

Figura 1.15 – stati ridondanti utili al bilanciamento delle tensioni sul bus de [1]

Concludendo, questa tipologia di inverter, sebbene sia abbastanza semplice da controllare, presenta alcuni svantaggi, di seguito elencati:

- un elevato numero di diodi di clamping che incrementa con l'aumentare del numero dei livelli, in quanto sono necessari tanti più diodi quanto più elevata è la tensione che devono interdire;

- un impiego diseguale degli switch: come si può notare in tabella 1.1,  $S_{a1}$  conduce solo quando  $V_{a0}=V_{dc}/2$ , mentre  $S_{a4}$  conduce per l'intero ciclo, con la sola eccezione della fase in cui  $V_{a0}=-V_{dc}/2$ . Tale diversa durata della fase di conduzione richiede livelli di impiego in corrente diversi, e quindi un differente dimensionamento degli switch;

- uno sbilanciamento delle tensioni ai capi dei condensatori del bus dc, che può essere compensato solo attraverso strategie di controllo dedicate.

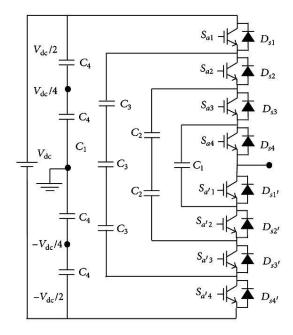

### **Capacitor-clamped Inverter**

La tipologia di convertitore Capacitor-clamped (o *Flying Capacitor*) deriva da una semplificazione della struttura Diode-clamped, e prevede l'impiego di capacità supplementari (capacità di clamping) in aggiunta a quelle già presenti sul bus dc, al fine di sintetizzare i differenti livelli di tensione desiderati in uscita. Queste capacità sostituiscono i diodi di clamping della precedente configurazione.

Figura 1.16 – Capacitor Clamped Inverter a 5 livelli

Per produrre in uscita m livelli di tensione è necessario un bus de composto da m-1 condensatori, 2·(m-1) switch e (m-1)·(m-2)/2 capacità di clamping.

Per un inverter a 5 livelli, la tensione di uscita e i corrispondenti stati degli switch sono riportati nella seguente tabella:

| Output voltage  | $S_{a1}$ | $S_{a2}$ | $S_{a3}$ | $S_{a4}$ | $S_{a^{'}1}$ | $S_{a^{'}2}$ | $S_{a^{'}3}$ | $S_{a'4}$ |

|-----------------|----------|----------|----------|----------|--------------|--------------|--------------|-----------|

| $V_{\rm dc}/2$  | 1        | 1        | 1        | 1        | 0            | 0            | 0            | 0         |

| $V_{\rm dc}/4$  | 1        | 1        | 1        | 0        |              | 0            | 0            | 0         |

| 0               | 1        | 1        | 0        | 0        | 1            | 1            | 0            | 0         |

| $-V_{\rm dc}/4$ | 1        | 0        | 0        | 0        | 1            | 1            | 1            | 0         |

| $-V_{\rm dc}/2$ | 0        | 0        | 0        | 0        | 1            | 1            | 1            | 1         |

Tabella 1.2 – stato degli switch e corrispondenti tensioni per l'inverter di Fig. 1.16

Le capacità non bloccano le tensione inverse; come conseguenza di questo il numero dei possibili stati degli interruttori aumenta (rispetto al Diode-clamped) ed è possibile generare lo stesso livello di tensione con più stati ridondanti (in tabella 1.2 è indicata solo una configurazione degli interruttori per ciascun livello di tensione).

Grazie a questa importante proprietà, è possibile bilanciare le tensioni ai capi delle capacità di clamping unicamente scegliendo un'opportuna strategia di commutazione che alterni le fasi di carica e scarica, rendendo così superflui circuiti addizionali di compensazione.

La tensione applicata su ciascun componente, a eccezione dei condensatori di clamping, è la stessa ed è uguale a  $V_{dc}/(m-1)$ , dove m è, al solito, il numero di livelli. I condensatori di clamping sono caricati a valori diversi di tensione: per produrre la forma d'onda in uscita, gli switch vengono fatti commutare in modo da combinare le varie tensioni di carica dei condensatori.

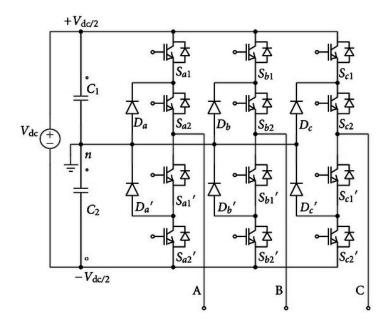

Di seguito un'illustrazione dei collegamenti circuitali utili al fine di ottenere una configurazione Capacitor-clamped trifase a tre livelli:

Figura 1.17 – Capacitor Clamped Inverter trifase a 3 livelli

Questa tipologia di inverter, sebbene conservi tutti i vantaggi propri dei convertitori multilivello, presenta anche alcuni problemi:

- un elevato numero di condensatori, poiché in aggiunta agli m-1 condensatori del bus de sono presenti (m-1)·(m-2)/2 capacità di clamping, che incrementano notevolmente il costo e la complessità del packaging del convertitore;

- una complicata strategia di controllo, soprattutto quando è necessaria l'implementazione di tecniche di Pulse Width Modulation. Infatti prima che i gate degli IGBT possano essere comandati per effettuare delle commutazioni, le cariche sui condensatori devono essere settate ai valori di tensione richiesti.

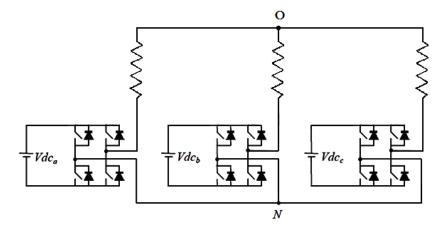

#### **Cascaded H-Bridge Inverter**

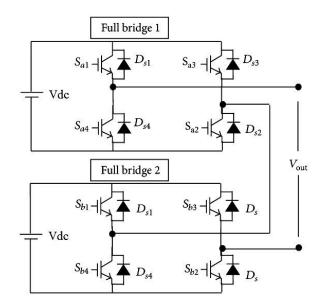

In questo lavoro di tesi, come già anticipato, si fa riferimento alla tipologia di inverter multilivello di tipo *Cascaded*, che pertanto verrà maggiormente approfondita.

Il principio di funzionamento di questo inverter è basato sulla connessione in serie di inverter a 2 livelli di tipo Full Bridge, presentati al paragrafo 1.2.2. La tensione di uscita è la somma delle tensioni prodotte da ciascuna unità Full Bridge, che, come noto, può assumere tre valori  $+V_{dc}$ , 0,  $-V_{dc}$ . Lo stato zero è comune a tutti i moduli in serie, quindi tale livello di tensione è contato solo una volta. Il numero di livelli totale m della tensione di fase risulta pertanto 2n+1, dove n è il numero delle unità in serie.

Figura 1.18 – Cascaded Inverter a 5 livelli

In sostanza, questa soluzione è tale da garantire modularità nella topologia. Infatti, per aumentare i livelli di tensione non serve modificare la struttura precedente: basta aggiungere altre unità full-bridge in serie tra loro. Per realizzare, ad esempio, un ramo di una struttura a tre livelli occorre un unico blocco, mentre per un ramo a cinque livelli due blocchi, per uno a sette livelli tre blocchi, ecc. Dunque ogni incremento di due livelli necessita di un blocco supplementare.

In caso di guasto in uno dei moduli, è possibile sostituirlo velocemente e con facilità. Inoltre, con una strategia di modulazione appropriata, è possibile bypassare il modulo guasto senza disalimentare il carico, portando a una disponibilità complessiva quasi continua.

Il numero totale di componenti per la configurazione monofase è facilmente deducibile moltiplicando il numero degli interruttori e dei condensatori presenti in un singolo ponte ad H per il numero di livelli richiesti. Pertanto il numero degli interruttori statici è 4·m, mentre il numero di condensatori è m.

Uno dei vantaggi principali di questa configurazione circuitale è che, a parità di livelli di tensione (*m*), necessita di un numero minore di componenti rispetto alle due configurazioni precedentemente esposte: peso e costo di questo inverter risultano, in genere, inferiori [3].

| Inverter Configuration | Diode<br>Clamped | Capacitor clamped | Cascade inverter |  |

|------------------------|------------------|-------------------|------------------|--|

| Main switching devices | 2(m-1)           | 2(m-1)            | 2(m-1)           |  |

| Main diodes            | 2(m-1)           | 2(m-1)            | 2(m-1)           |  |

| Clamping diodes        | (m-1)(m-2)       | 0                 | 0                |  |

| DC bus capacitors      | (m-1)            | (m-1)             | (m-1)/2          |  |

| Clamping capacitors    | 0                | (m-1)(m-2)/2      | 0                |  |

Figura 1.3 – numero di componenti richiesti per ciascuna tipologia di inverter multilivello monofase

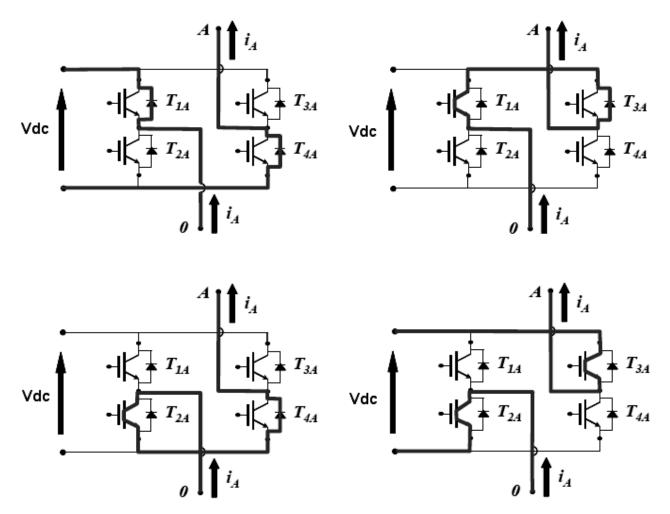

Vediamo ora di caratterizzare il comportamento di ciascun modulo.

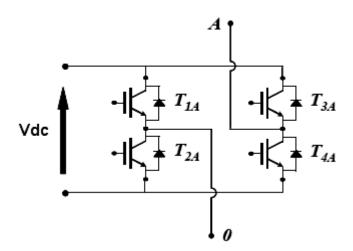

Figura 1.19 – singolo modulo Full-Bridge

La condizione di stato "1" significa che l'interruttore è chiuso (posizione di ON), mentre lo stato "0" significa che l'interruttore è aperto (posizione di OFF). In riferimento alla figura 1.19, comandando opportunamente gli interruttori, è possibile ottenere in uscita le tensioni riportate in tabella 1.4:

| $T_{1A}$ | $T_{2A}$ | $T_{3A}$ | $T_{4A}$ | $\mathbf{V_{A0}}$ |

|----------|----------|----------|----------|-------------------|

| 1        | 0        | 0        | 1        | $-V_{ m dc}$      |

| 1        | 0        | 1        | 0        | 0                 |

| 0        | 1        | 0        | 1        | 0                 |

| 0        | 1        | 1        | 0        | $+V_{dc}$         |

Tabella 1.4 – stato degli interruttori e tensione di uscita dal modulo

Nella seguente figura è mostrato il percorso della corrente per ciascuno stato degli interruttori:

Figura 1.20 – percorso della corrente [1] per i casi (in ordine) di tabella 1.4

#### Topologia Trifase

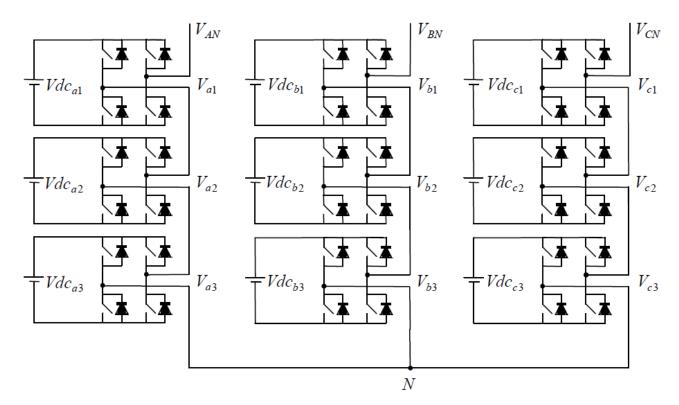

Di seguito un'illustrazione dei collegamenti circuitali utili al fine di ottenere una configurazione Cascaded H-Bride trifase a 7 livelli:

Figura 1.21 - Cascaded H-Bridge trifase a 7 livelli

Per un sistema trifase a m-livelli, la tensione di linea, cioè la tensione concatenata, è sintetizzata con  $m_{LL}$  livelli, dove

$$m_{LL} = 2m - 1 \tag{1.20}$$

infatti la tensione di linea in uscita verso il carico, detta  $V_{AB}$ , è data dalla differenza delle tensioni di uscita prodotte da due rami d'inverter ( $V_{AN}$ - $V_{BN}$ ).

Per quanto riguarda, invece, la tensione di fase del carico (rappresentata dalla differenza delle  $m_{LL}$  tensioni di linea) sono presenti  $m_E$  livelli di tensione, dove

$$m_E = 2m_{LL} - 1 (1.21)$$

Utilizzando quindi una struttura trifase a sette livelli (m=7) come quella di figura 1.21, si ha che  $m_{LL} = 13$ ,  $m_E = 25$ .

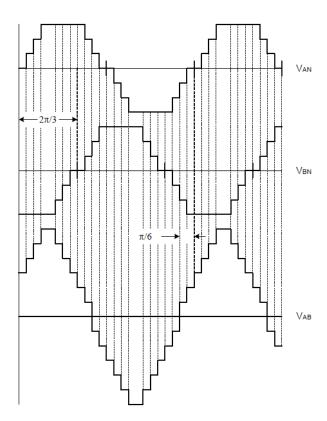

Figura 1.22 – forme d'onda delle tensioni di ramo e tensione di linea per l'inverter di fig. 1.21

#### Alimentazioni isolate

Una particolarità di questa tipologia di inverter multilivello è che le sorgenti di tensione de di ogni ponte ad H devono essere separate ed isolate tra loro. Di fatto questa specifica può essere soddisfatta attraverso la predisposizione di ponti raddrizzatori trifase o monofase e opportuni stadi di livellamento della tensione. Questo porta a un'ulteriore complicazione della configurazione complessiva e può rappresentare un limite all'applicazione dell'inverter cascaded H-bridge. Tuttavia diventa il convertitore ideale nel caso in cui le sorgenti di tensione de siano, per loro natura, separate, come nel caso dei moduli fotovoltaici, delle celle a combustibile, delle batterie, ecc.

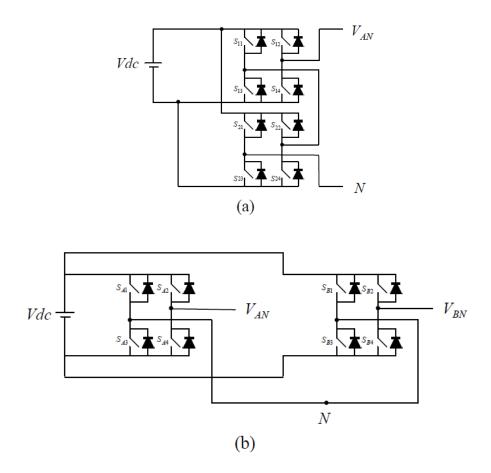

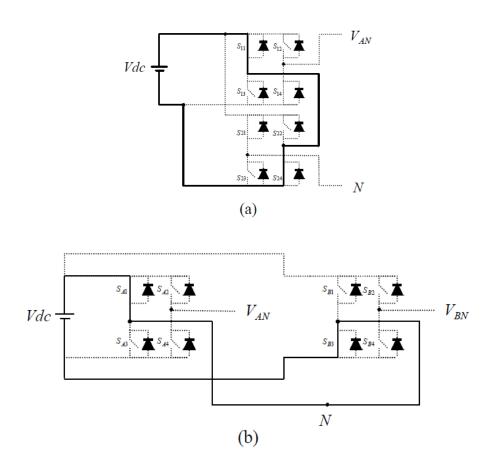

La separazione delle sorgenti non riguarda solo le varie fasi, ma interessa anche i singoli livelli. Se questa specifica non fosse rispettata, si incorrerebbe in cortocircuiti delle sorgenti di alimentazione. Si riportano di seguito due casi che dimostrano la necessità di alimentazioni separate.

Nel primo caso tutti i ponti ad H della stessa fase condividono la stessa sorgente di alimentazione in continua. Nel secondo caso lo stesso livello di ciascuna fase condivide la stessa sorgente di alimentazione. La figura 1.23 illustra il primo e il secondo caso per un inverter cascaded a cinque livelli.

Figura 1.23 – (a) primo caso, (b) secondo caso

Tuttavia, oltre a quelle illustrate in fig. 1.23, ci sono altre combinazioni che possono portare a cortocircuiti: qui si riporta solo una condizione per ogni caso.

Il primo caso di cortocircuito della sorgente di alimentazione, illustrato in fig. 1.24 (a), si verifica quando gli interruttori S11 e S24 sono contemporaneamente chiusi; il secondo caso, illustrato in fig. 1.24 (b), si verifica invece quando sono contemporaneamente chiusi gli interruttori SA1 e SB3.

Figura 1.24 – cortocircuito della sorgente di alimentazione (a) primo caso, (b) secondo caso

### 1.3.3 Applicazioni

Gli inverter multilivello offrono una soluzione conveniente nella gestione dell'energia per le applicazioni di media tensione. Questi convertitori sono stati ampliamente utilizzati negli impianti chimici, nelle stazioni di estrazione di petrolio e gas naturale, negli impianti industriali, nel pompaggio dell'acqua, nella propulsione sottomarina, nella generazione di energia, nei dispositivi elettronici di potenza, ecc.

In questa sezione sono presentate reali applicazioni dell'inverter multilivello, con particolare riferimento alla topologia Cascaded.

#### Pompe e ventole

Pompe e ventole sono utilizzate in molti settori dell'industria, le cui applicazioni richiedono alte tensioni, grandi potenze e funzionano tipicamente a velocità e a carico variabili. L'uso di valvole di chiusura o di strozzamento può essere sostituito con un sistema di controllo della velocità del flusso, il quale porta a un significativo aumento dell'efficienza: tale controllo può essere ottenuto con l'impiego degli inverter multilivello cascaded, che, oltre a presentare tutti i vantaggi in termini di efficienza precedentemente esposti, sono caratterizzati da forme d'onda di tensione con un contenuto armonico ridotto rispetto a un inverter tradizionale. Questo va a beneficio del dimensionamento dei filtri [4].

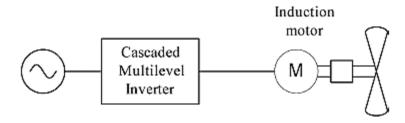

Figura 1.25 – inverter multilivello cascaded applicato a una ventola [4]

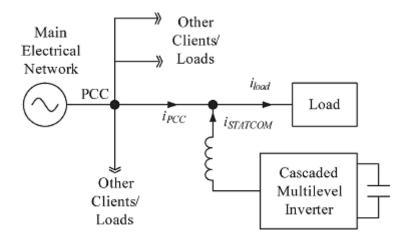

#### STATCOM e Filtri Attivi

Questi dispositivi vengono connessi direttamente alla rete di media tensione e il loro compito è quello di agire su di essa in modo da migliorare la trasmissione dell'energia: effettuano operazioni di scambio di potenza reattiva, rifasamento, riduzione del contenuto armonico, ecc. L'utilizzo di inverter cascaded consente di raggiungere il livello di tensione richiesto dalla rete senza l'utilizzo di trasformatori, inoltre la struttura complessiva dell'inverter può essere semplificata in quanto non necessita di ponti raddrizzatori per realizzare lo stadio in continua.

Figura 1.26 – inverter multilivello connesso direttamente alla rete come filtro attivo [4]

#### Sistemi di trazione

I sistemi di trazione richiedono uno stadio di alimentazione ad alta tensione in bassa frequenza e la possibilità di uno stadio che consenta l'inversione il flusso di potenza, per recuperare l'energia della fase di frenata. Gli inverter multilivello consentono di ridurre, in questa applicazione, il contenuto armonico, la potenza reattiva assorbita e le grandezze di sequenza inversa. Sono stati proposti, a tal fine, convertitori back-to-back multilivello di tipo cascaded per applicazioni di tipo automotive.

# Capitolo 2

# Tecniche di modulazione multilivello

#### 2.1 Introduzione

In questo capitolo si analizzano le principali tecniche di modulazione per gli inverter multilivello, le quali risultano, in linea generale, un'estensione delle tecniche di modulazione per gli inverter a due livelli presentate nel Capitolo 1.

I componenti di potenza che svolgono il ruolo di interruttori sono in numero maggiore rispetto ai due componenti per ramo che si presentavano nel due livelli, pertanto, per un multilivello, la complessità di modulazione aumenta.

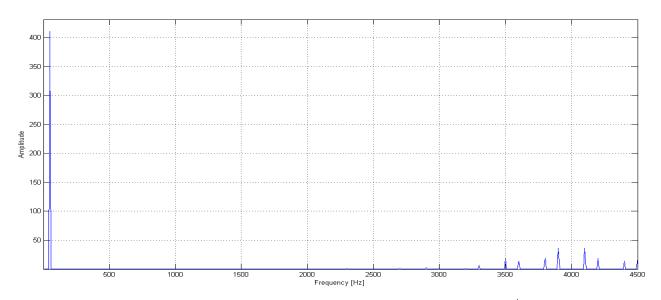

Esistono molte tecniche di modulazione, ognuna delle quali consente di ottenere migliori prestazioni a seconda del tipo di carico connesso all'inverter e del risultato che si vuole ottenere. Infatti si potrebbe decidere di adottare una tecnica di modulazione che riduca il più possibile l'indice THD (*Total Harmonic Distortion*)

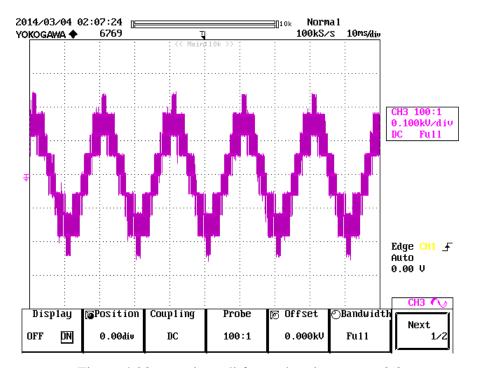

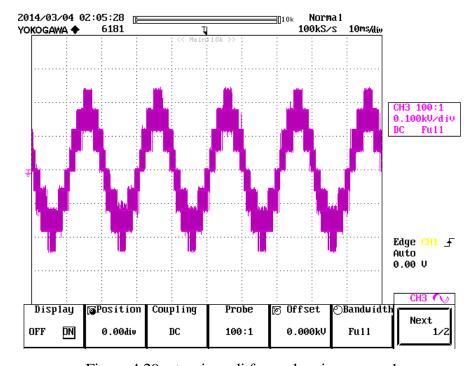

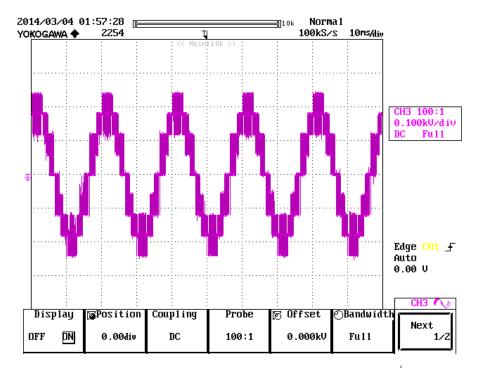

della tensione sul carico; oppure la specifica potrebbe venire dal ripple, che si vuole minimizzare, della corrente di carico. Volta per volta saranno presentati vantaggi e limiti di ciascuna tecnica di modulazione con particolare riferimento alla configurazione trifase a tre livelli, topologia di riferimento in questa tesi.

# 2.2 PWM Multiportante

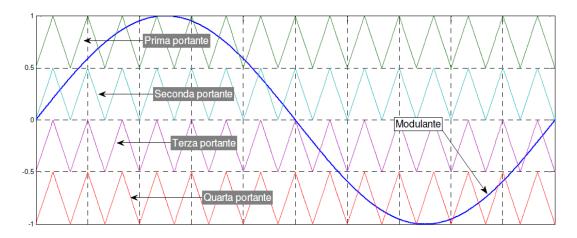

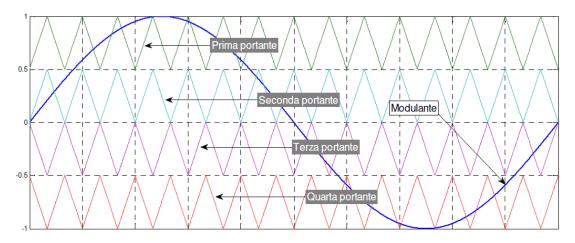

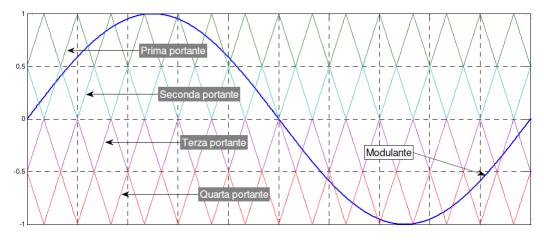

E' possibile estendere la modulazione PWM al caso multilivello, definendola col nome di Multi-Carrier PWM (MC-PWM). Questa tecnica prevede l'adozione di n-1 portanti, dove n è il numero di livelli del convertitore, e si basa sempre sul concetto di intersezione di uno o più segnali modulanti, a seconda che il sistema sia monofase o trifase, con le n-1 portanti.

Per un'applicazione a tre livelli pertanto sono necessarie due portanti, per una a cinque, invece, si utilizzano quattro portanti, e così via. Le interazioni tra le portanti e le modulanti sono fondamentali per generare i segnali di controllo che pilotano coppie di interruttori complementari nei vari livelli dell'inverter.

La posizione reciproca delle portanti determina varie tecniche di modulazione:

- PD (Phase Disposition)

- POD (Phase Opposite Disposition)

- APOD (Alternative Phase Opposition Disposition)

La prima di queste strategie è quella più utilizzata, in quanto produce una minore distorsione armonica delle tensione di uscita, e prevede tutte le portanti in fase tra di loro. La seconda strategia prevede che le portanti negative (quelle al di sotto del riferimento 0) siano sfasate di 180° rispetto a quelle positive. La terza strategia prevede che le portanti adiacenti siano tra loro sfasate di 180°.

Di seguito sono riportate alcune illustrazioni che mostrano il significato delle rispettive posizioni delle portanti per un inverter a cinque livelli, a cui corrispondono quindi quattro portanti.

Figura 2.1 – PWM Multiportante PD [5]

Figura 2.2 – PWM Multiportante POD [5]

Figura 2.3 – PWM Multiportante APOD [5]

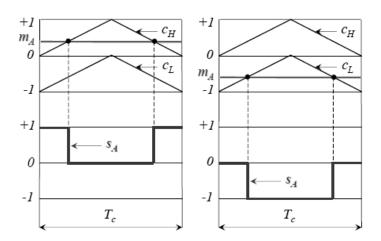

Con riferimento a un inverter a tre livelli monofase, si esprime il valore della modulante con la stessa convenzione adottata nel Capitolo 1, cioè con l'ausilio della funzione di commutazione s. Ora però la tensione di ramo spazia su tre livelli (Vdc, 0, -Vdc), pertanto anche la funzione di commutazione assume tre valori: 1, 0, -1. Il valore della modulante può essere quindi calcolato con la formula (1.14).

Per quanto riguarda le due portanti, la prima  $c_L$  varia tra -1 e 0, la seconda  $c_H$  tra 0 e +1. I criteri per determinare i valori istantanei della funzione di commutazione sono:

$$se m_A > c_H allora s_A = +1$$

$$se c_L < m_A < c_H allora s_A = 0$$

$$se c_L > m_A allora s_A = -1$$

Figura 2.4 – intersezione portante-modulante con modulante positiva (sinistra) e negativa (destra) [1]

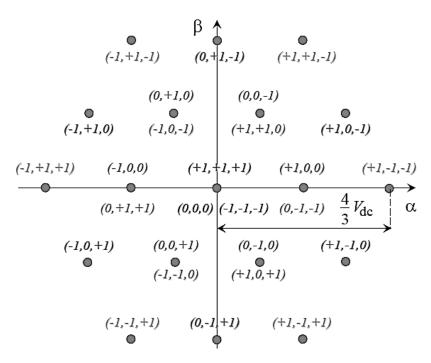

Per quanto riguarda la configurazione trifase è opportuno, come nel caso di inverter a due livelli, utilizzare i vettori di spazio al fine di descrivere le tensioni applicate al carico. Pertanto risultano valide tutte le relazioni presentate al paragrafo 1.2.3, in particolare la 1.12, espressione fondamentale che lega le funzioni di commutazione alle tensioni sul carico. Tenendo conto che le funzioni di commutazione possono assumere tre valori, si ha che il numero delle possibili configurazioni è  $3^3 = 27$ , contro le 8 configurazioni disponibili con un inverter trifase a due livelli. In particolare, dei 27 vettori di spazio delle tensioni stellate di carico, 3 sono

configurazioni nulle e 24 sono configurazioni attive con diverse molteplicità. Si può verificare dalla figura seguente che il numero di livelli presenti nella tensione stellata è 9.

Figura 2.5 – possibili stati del vettore di spazio delle tensioni stellate di carico

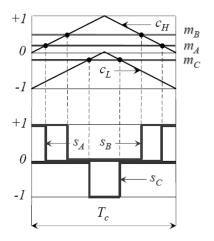

E' possibile ottenere i valori delle tre modulanti con le stesse relazioni viste al paragrafo 1.2.3, pertanto si fa' riferimento alle espressioni (1.14), (1.15), (1.16). Il valore  $m_0$  rappresenta ancora un grado di libertà: la sua modifica permette una traslazione rigida delle tre modulanti.

Figura 2.6 – intersezione portante-modulante per il caso trifase [1]

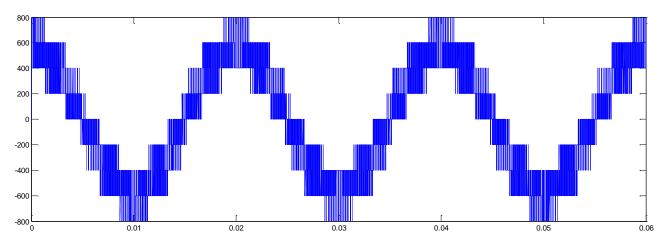

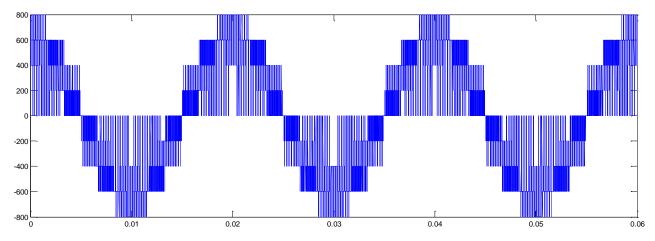

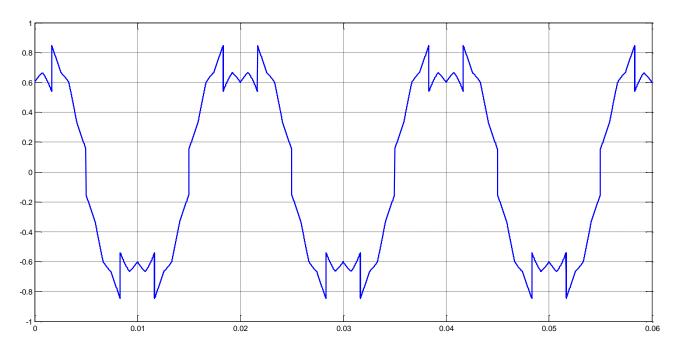

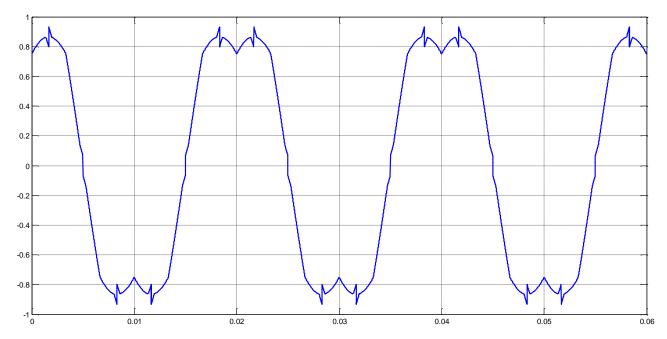

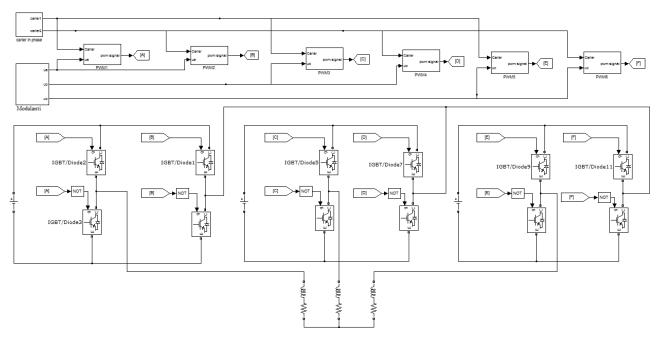

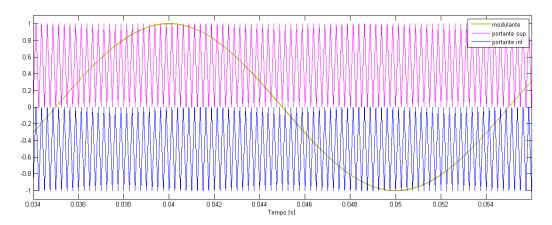

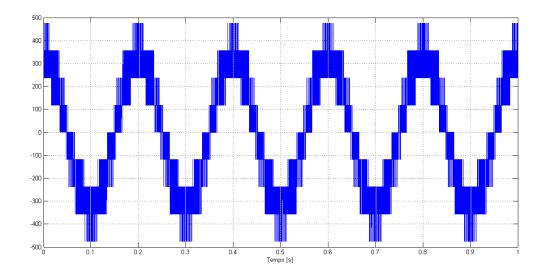

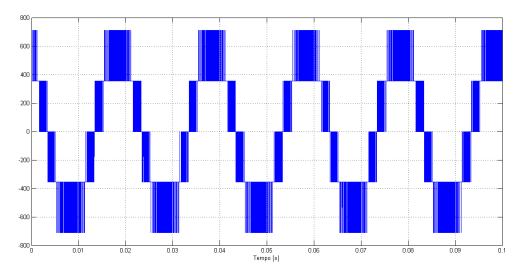

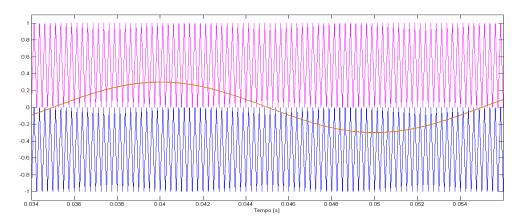

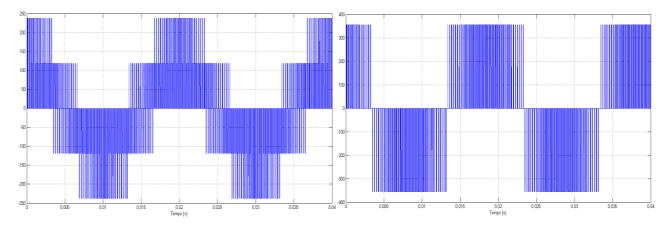

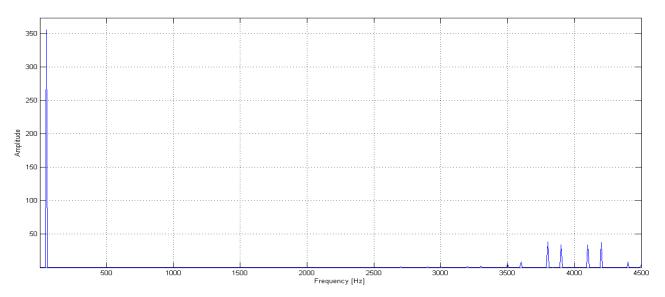

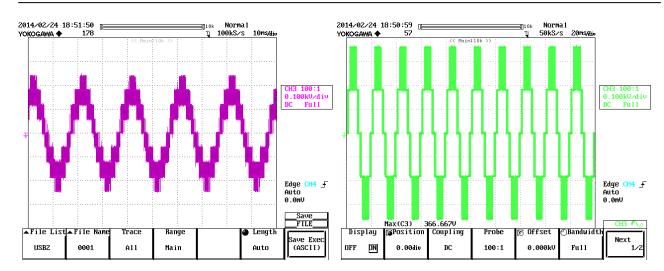

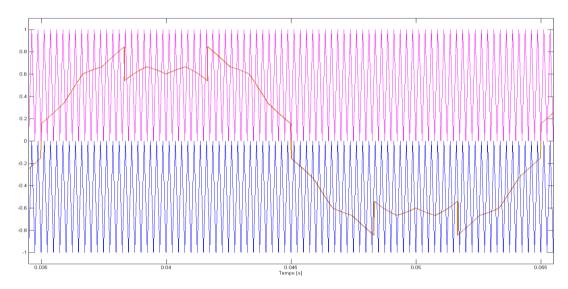

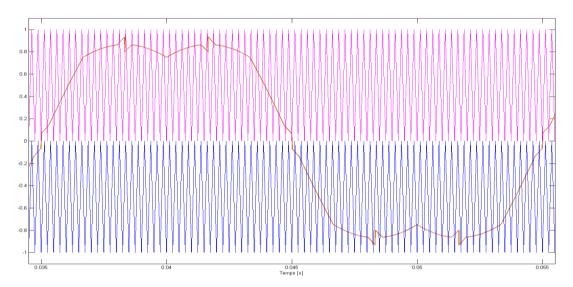

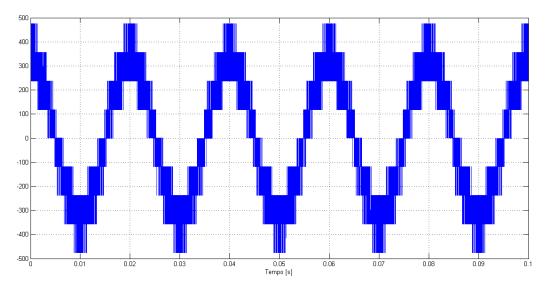

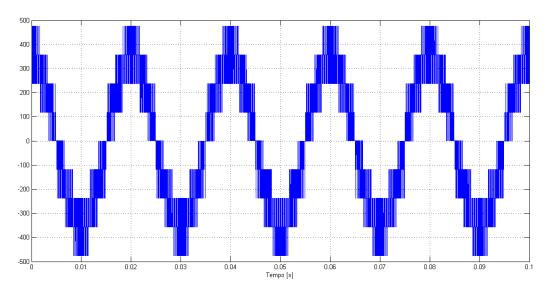

Attraverso alcune simulazioni eseguite con l'utility Simulink del software Matlab, è possibile capire in che modo la posizione reciproca delle portanti influenzi la forma d'onda della tensione di uscita. A tal proposito si fa riferimento a un inverter a tre livelli trifase di tipo Cascaded controllato via via con tutte le disposizioni di portante precedentemente esposte. La tensione continua di alimentazione considerata è 600 V e l'indice di modulazione è 1.

Figura 2.7 – tensione di fase con modulazione PWM PD

Figura 2.8 – tensione di fase con modulazione PWM POD

La modulazione PWM APOD non è stata riportata in figura in quanto, per un inverter a tre livelli, l'andamento della forma d'onda di uscita è il medesimo di quello della modulazione PWM POD.

Si vede subito, confrontando la figura 2.7 con la figura 2.8, che la prima di queste si avvicina di più a una sinusoide. Infatti, il THD del primo caso risulta 34%, mentre nel secondo caso risulta 40%.

Le tecniche di modulazione basate sull'utilizzo di portanti (CB-PWM, *Carrier Based PWM*) sono ampiamente diffuse data la loro semplicità e il ridotto sforzo computazionale, rispetto alla tecnica SVM presentata di seguito. Questo permette la loro implementazione su DSP industriali, senza il bisogno di ulteriori sistemi di calcolo, tipo FPGA.

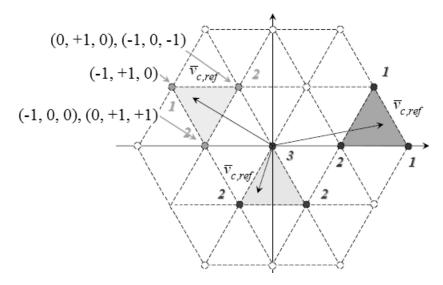

# 2.3 Space Vector Modulation

La tecnica SVM è già stata introdotta nel Capitolo 1 a proposito dell'inverter trifase a due livelli. La sua implementazione per un inverter multilivello si basa sullo stesso concetto: il generico vettore di tensione di riferimento è ottenuto mediamente, in un periodo di commutazione T<sub>c</sub>, utilizzando i tre vettori di spazio più vicini (NTV, *Nearest Three Vectors*).

Tuttavia ciò che differenzia principalmente il caso a due livelli da quello multilivello, è la presenza di un numero considerevolmente maggiore di possibili stati del vettore di spazio della tensione sul carico. Infatti, come visto nel paragrafo precedente, un inverter trifase a tre livelli presenta 27 possibili stati (vedi fig. 2.5), contro gli 8 stati di un inverter trifase a due livelli. Il numero dei possibili stati aumenta con il numero di livelli: per un inverter trifase a 5 livelli esistono 125 possibili configurazioni.

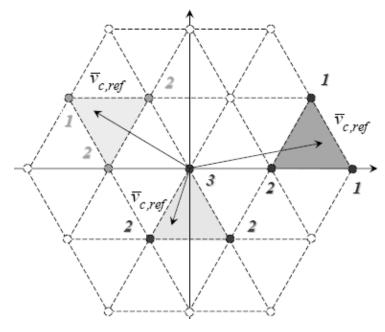

Con riferimento a un inverter trifase a tre livelli, il piano  $\alpha$ - $\beta$  dei vettori di spazio è diviso in 24 triangoli, i cui vertici sono i possibili stati delle tensioni di carico: 12 triangoli più esterni, caratterizzati da un solo vettore con molteplicità due; 6 triangoli internedi, caratterizzati da due vettori con molteplicità due; 6 triangoli interni con

due vettori con molteplicità due e un vettore (configurazione nulla) con molteplicità tre.

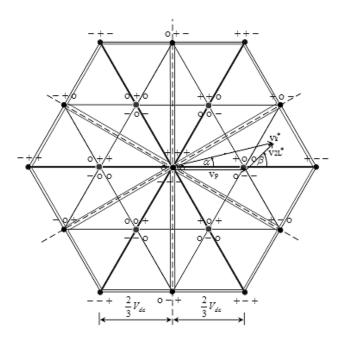

Figura 2.9 – divisione del piano α-β in 24 triangoli con relative molteplicità dei vettori [1]

Il piano può ulteriormente essere diviso in sei settori a forma di diamante ( $S_x$ , in figura 2.10): ognuno di essi fa riferimento a un particolare vettore, detto *vettore pivot*. In un inverter trifase a tre livelli, sono vettori pivot tutti quei possibili vettori di spazio della tensione di carico che hanno ampiezza 2/3  $V_{dc}$  ( $V_1$ - $V_6$ , in figura 2.10).

Figura 2.10 – divisione del piano in sei settori e corrispondenti vettori pivot

Il ruolo dei vettori pivot nella tecnica SVM multilivello è simile a quello del vettore nullo per l'inverter a due livelli. Infatti, in quest'ultimo, la ripartizione del tempo di applicazione della configurazione nulla tra i due stati ridondanti, come visto nel Capitolo 1, determina una particolare tecnica di modulazione (5 intervalli tipo A, tipo B, 7 intervalli simmetrica, generalizzata).

Anche nell'inverter trifase a tre livelli si possono ottenere modulazioni analoghe, ma anziché riferirsi al vettore nullo, ci si riferisce al vettore pivot. Ogni sequenza di commutazione comincia e termina con l'applicazione del vettore pivot, e la ripartizione del tempo tra le sue due molteplicità determina due tipi di modulazione: *Continuous* SVM e *Discontinuous* SVM.

Considerando metà periodo di commutazione, la tecnica Continuous SVM consiste nell'applicare all'inizio della sequenza di commutazione una molteplicità del vettore pivot, per poi concludere la sequenza con l'altra molteplicità. Il tempo di applicazione delle due molteplicità è casuale, questo fa corrispondere questa strategia alla tecnica PWM PD (Phase Disposition), già trattata per la modulazione PWM multiportante [6]. Quando è applicata solo una molteplicità del vettore pivot, allora si parla di Discontinuous SVM.

Il vettore pivot è applicato in tutte le possibili sequenze, mentre il vettore nullo è applicato solo a bassi indici di modulazione. Se si applicasse il vettore nullo ad alti indici di modulazione, si otterrebbe la modulazione POD (Phase Opposite Disposition), già trattata per la tecnica PWM multiportante [6].

La tecnica SVM permette di conseguire un miglior sfruttamento della tensione del bus de rispetto a una modulazione PWM Sinusoidale. Infatti il valor massimo di un sistema sinusoidale e simmetrico di tensioni coincide, come già detto nel Capitolo 1, con il raggio del cerchio inscritto nell'esagono. Tale valore, per un inverter trifase a tre livelli, è pari a  $2/\sqrt{3}~V_{dc}$ .

Tra gli svantaggi di questa tecnica è opportuno segnalare lo sforzo computazionale che essa richiede. Il controllo che genera i segnali di pilotaggio degli inverter deve calcolare, tramite specifici algoritmi, sia quali sono i vettori adiacenti al vettore di riferimento, considerando anche quali combinazioni di vettori permettono il minor numero di commutazioni (migliore sequenza), sia i tempi di applicazione degli stessi. Aumentando il numero di livelli, il numero di possibili stati aumenta esponenzialmente, così come la loro ridondanza, la complessità del sistema di controllo e i tempi necessari per il calcolo dei segnali di pilotaggio degli interruttori. Questo pone un limite inferiore al tempo di commutazione T<sub>c</sub>, limite sempre più restrittivo con l'aumentare del numero dei livelli.

#### 2.4 Centered PWM

Con il concetto di Centered PWM (CPWM) non si intende un'altra tecnica di modulazione diversa dalla MC-PWM e dalla SVM, ma ci si riferisce a una strategia di ottimizzazione degli output a esse applicabile. L'obiettivo, infatti, è quello di minimizzare la distorsione armonica delle correnti sul carico e di sfruttare a pieno la tensione sul bus DC. Tale strategia è applicabile sia all'inverter a due livelli che a quello multilivello, per il quale ne viene fornita la trattazione del caso a tre livelli.

#### **CPWM 2 livelli**

Nel Capitolo 1 sono state affrontate le tecniche di modulazione più comuni per un inverter a due livelli. In particolare si è visto che, nella modulazione PWM Generalizzata, esiste un coefficiente m<sub>0</sub> di valore arbitrario che è in grado di traslare verticalmente le modulanti. Il valore di interesse di tale coefficiente è quello per cui le modulanti risultano centrate rispetto all'intervallo [0,1] (vedi espressione 1.19), il che equivale a sommare alle modulanti un offset che aggiunge a esse una componente

di terza armonica. Tale valore determina la sequenza di commutazione 7 intervalli simmetrica, ovvero quella sequenza che ripartisce equamente i tempi di applicazione delle configurazioni nulle nella modulazione SVM.

Si dimostra che con tale offset, in riferimento a un sistema di tensioni simmetrico sinusoidale, l'indice di modulazione massimo non è più 1 (figura 2.11) ma è  $2/\sqrt{3}$  (figura 2.12), ovvero 15.5% superiore. Quindi si ha un miglior sfruttamento della tensione del bus DC e si ha inoltre una minore distorsione armonica delle correnti sul carico.

Figura 2.11 – modulante di una fase con indice di modulazione m=1 e  $m_0$ =0.5 costante

Figura 2.12 – modulante di una fase con indice di modulazione m= $2/\sqrt{3}$  e m $_0$  calcolato con l'espressione (1.19)

Si vede dalla figura 2.12 che il centraggio delle modulanti consente di impostare un valore dell'indice di modulazione *m* maggiore senza sforare nella sovramodulazione (modulante ancora compresa nell'intervallo [0,1]) e che la forma d'onda delle modulanti non è più sinusoidale ma presenta la suddetta componente di terza armonica.

#### **CPWM 3 livelli**

Per quanto riguarda il caso di inverter a tre livelli il concetto è lo stesso: il centraggio delle modulanti può avvenire con il semplice contributo del suddetto offset. Tuttavia la minimizzazione del ripple e del THD delle correnti sul carico necessita di una particolare iniezione: in questo caso infatti l'espressione di m<sub>0</sub> si complica e, a tal proposito, sono state definite in letteratura varie procedure di calcolo di tale offset, che verranno brevemente presentate di seguito. Infine è proposta una procedura semplificata, sviluppata, parallelamente a questo lavoro di tesi, presso il Dipartimento di Ingegneria Elettrica dell'Università di Bologna.

Il primo metodo, introdotto da F. Wang nell'articolo dell'IEEE "Sine-Triangle versus Space-Vector Modulation for Three-Level PWM Voltage-Source Inverters" (2002) [7], consiste nella determinazione dell'espressione dell'offset sulla base dell'identificazione della modulante massima (Max), di quella intermedia (Mid) e di quella più piccola (Min). Il valore dell'offset è dato dalla tabella [2.1].

| Condizioni sulle modulanti | Valori degli offset |

|----------------------------|---------------------|

| Mid < 0 & (Max - Min) > 1  | Min/2               |

| Mid > 0 & (Max - Min) < 1  | Max/2               |

| Mid < 0 & (Max - Min) > 1  | -(1 - Max)/2        |

| & $(1 - Max) > - Mid$      |                     |

| Mid > 0 & (Max - Min) > 1  | (1 + Min)/2         |

| & $(1 + Min) > Mid$        |                     |

| Others                     | -(Max + Min)/2      |

Tabella 2.1 – valori degli offset al variare della posizione reciproca delle modulanti

Il secondo metodo, introdotto da B.P. McGrath, D.G. Holmes, T. Lipo nell'articolo dell'IEEE "Optimized Space Vector Switching Sequences for Multilevel Inverters" (2003) [8], utilizza la funzione "modulus" (mod) per traslare le modulanti, già centrate rispetto alle due portanti, nella regione di un'unica portante, in modo da ottenere le stesse condizioni che si presentano nell'inverter due livelli. Dopodiché le modulanti vengono nuovamente centrate. Utilizzando i segnali di riferimento della tensione, anziché le modulanti, le espressioni per determinare l'offset ( $v_{cm}$ ) risultano:

$$v_{offset} = -\frac{1}{2} [\max(v_k^*) + \min v_k^*]$$

(2.1)

$$v_k' = v_k^* + v_{offset} + V_{dc} \ mod(V_{dc})$$

(2.2)

$$v'_{offset} = \frac{v_{dc}}{2} - \frac{1}{2} [\max(v'_k) + \min v'_k]$$

(2.3)

$$v_{cm} = v_{offset} + v'_{offset} (2.4)$$

Infine, il metodo sviluppato parallelamente a questa tesi, si basa sulla corrispondenza dei vettori di spazio tra il caso a due livelli e quello a tre livelli.

Si è detto, nei paragrafi precedenti, che il piano  $\alpha$ - $\beta$  dei vettori di spazio può essere diviso in 6 settori, ognuno afferente a un proprio vettore pivot. Il vettore di spazio di riferimento  $v_k^*$  può essere ottenuto come somma del vettore pivot  $v_p$ , corrispondente al suo settore di appartenenza, e del vettore residuo  $v_{2L}^*$ , corrispondente al vettore di riferimento per l'inverter a due livelli.

$$v_k^* = v_p + v_{2L}^* (2.5)$$

Infatti è possibile identificare nel piano  $\alpha$ - $\beta$  dei vettori di spazio sei sotto-esagoni, ognuno dei quali è centrato sul vertice di un vettore pivot (vettori di ampiezza 2/3  $V_{dc}$  in figura 2.13): ciascuno di essi rappresenta l'equivalente del caso di inverter a due livelli.

Figura 2.13 – scomposizione del vettore di spazio di riferimento e punti centrali dei sotto-esagoni

All'interno di ciascun sotto-esagono è possibile applicare tutte le tecniche di modulazione viste per l'inverter a due livelli.

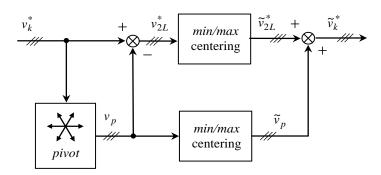

Questa possibilità è sfruttata per ottenere la modulazione centrata con la sola iniezione di un segnale di offset, il cui valore è calcolato secondo il seguente schema logico (figura 2.14).

Figura 2.14 – schema a blocchi per il calcolo del segnale di offset [9]

Si sottrae al vettore di riferimento il vettore pivot corrispondente, dopodiché tale residuo è centrato secondo la tecnica min/max. Anche il vettore pivot viene centrato secondo tale tecnica e, infine, entrambe i segnali risultanti vengono sommati.

I valori del vettore pivot antitrasformato per le tre fasi possono essere ottenuti sulla base del segno della rispettiva tensione di riferimento [9]:

$$v_{p_k} = \frac{V_{dc}}{2} \left[ sign(v_k^*) - \frac{1}{3} \sum_{k=1}^{3} sign(v_k^*) \right]$$

(2.6)

Il segnale di modo comune da aggiungere alle tensioni di riferimento si calcola come [9]:

$$v_{cm} = \frac{V_{dc}}{6} \sum sign(v_k^*) - \frac{1}{2} \left[ max(v_k^* - v_p) + min(v_k^* - v_p) \right]$$

(2.7)

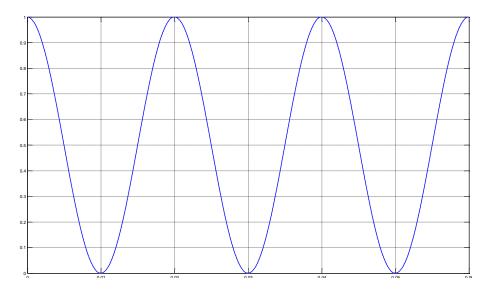

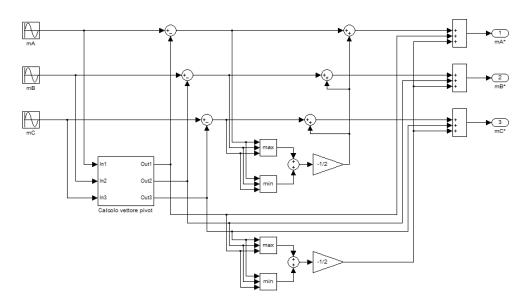

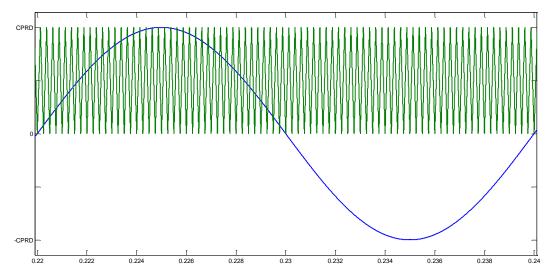

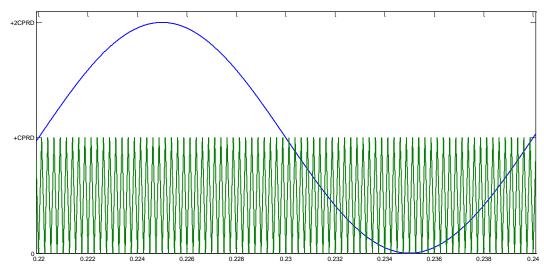

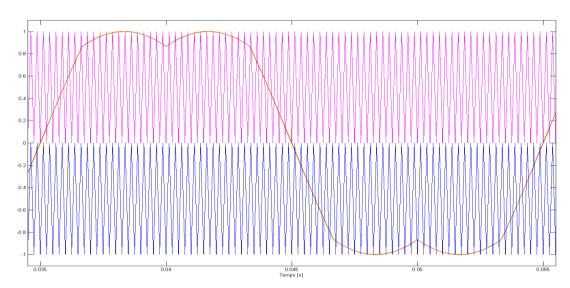

Questa procedura può essere verificata attraverso simulazioni con il software Simulink, nelle quali tre modulanti sinusoidali sono modificate con la suddetta tecnica in modo tale da ottenere la CPWM (vedi figura 2.15).

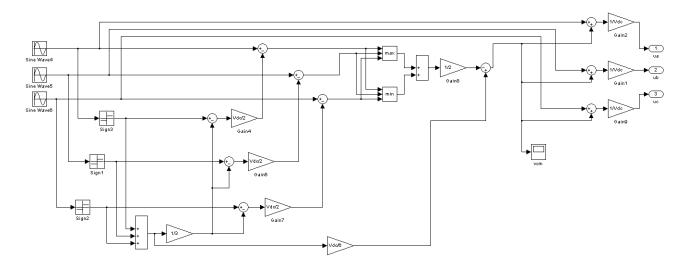

Figura 2.15 – schema a blocchi Simulink per la CPWM

Il blocco "Calcolo vettore pivot" in figura 2.15 ha il compito di calcolare il giusto vettore pivot a seconda della posizione reciproca delle modulanti.

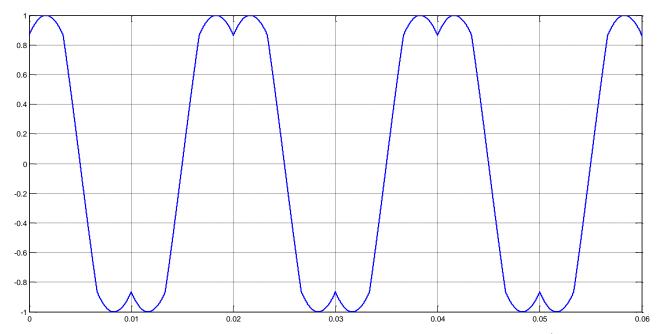

Variando l'indice di modulazione, è possibile ottenere le seguenti forme d'onda per tre modulanti modificate.

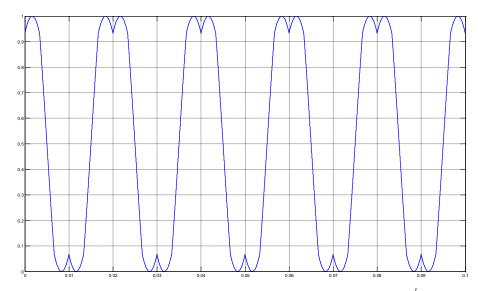

Figura 2.16 – modulante di una fase con indice di modulazione m=0.8

Figura 2.17 – modulante di una fase con indice di modulazione m=1

Figura 2.18 – modulante di una fase con indice di modulazione m= $2/\sqrt{3}$

Come si può notare, le modulanti hanno una forma d'onda diversa a seconda dell'indice di modulazione e tale andamento differisce da quello dell'inverter a due livelli. Quindi, come nel caso a due livelli, è possibile raggiungere un indice di modulazione superiore a uno e, con questo particolare offset, la corrente sul carico risulta meno distorta.

Le stesse forme d'onda si ottengono anche con i primi due metodi, tuttavia questa procedura risulta essere più intuitiva e di più facile implementazione sui moderni DSP, nonché per via analogica.

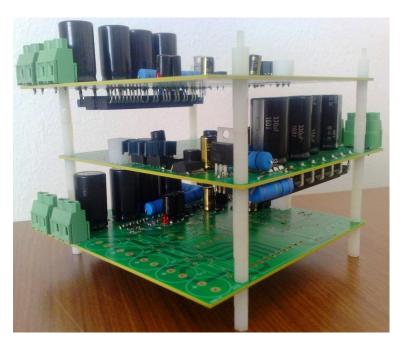

# Capitolo 3

# Realizzazione di un inverter trifase a tre livelli

#### 3.1 Introduzione

In questo capitolo si presenta l'attività centrale di questa tesi, ovvero la realizzazione di un inverter trifase a tre livelli, sviluppata presso il Dipartimento di Ingegneria Elettrica e dell'Informazione dell'Università di Bologna. La topologia circuitale scelta per il multilivello è quella Cascaded, in quanto, come si vedrà, si adatta perfettamente al progetto preesistente dei moduli H-Bridge e, a differenza delle altre configurazioni, non prevede un bilanciamento della tensione sul bus DC, rendendo quindi più semplice la strategia di modulazione.

### 3.2 Moduli dell'inverter

#### 3.2.1 Il progetto

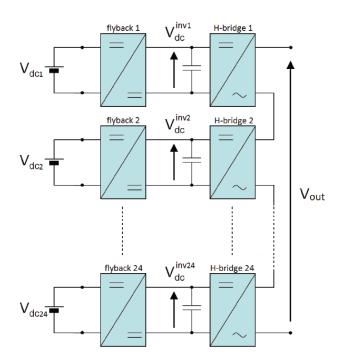

Come accennato nell'introduzione, i moduli che costituiscono l'inverter derivano da un progetto preesistente, sviluppato all'interno dello stesso dipartimento. Tale progetto consisteva nella realizzazione di un convertitore in grado di alimentare la scarica di un plasma.

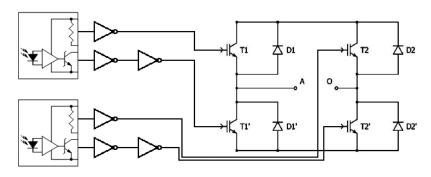

Per generare plasma è necessario scaldare un gas fino a che le molecole che lo compongono non si ionizzano, trasformando il gas, appunto, in plasma. Per fare questo, è possibile far fluire una certa corrente attraverso il gas in questione: la tensione di alimentazione deve tuttavia essere di alcuni kV e necessariamente alternata, al fine di mantenere il gas nello stato di plasma. Per questo è stato progettato tale convertitore, ovvero un inverter monofase cascaded a 24 livelli: ogni stadio è alimentato da una batteria ed è costituito dalla cascata di un convertitore flyback e di un H-Bridge (figura 3.1), entrambe posti sulla stessa scheda.

Figura 3.1 – inverter monofase cascaded a 24 livelli per la scarica di un plasma

Ora gli stessi moduli vengono utilizzati per il lavoro di questa tesi. Tuttavia si è deciso di non installare su di essi il convertitore flyback, ma di provvedere alla tensione del bus DC con una sorgente esterna ai moduli.

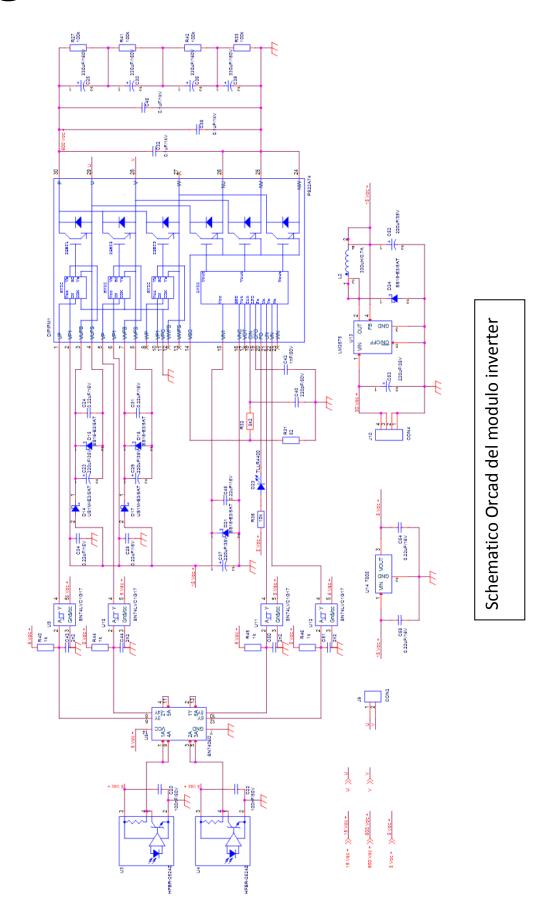

Lo schematico e il layout di tale scheda sono realizzati in ambiente Orcad, un software per la progettazione di circuiti stampati (PCB). La scheda PCB, come da progetto, ha una dimensione di 141x142 mm e si presenta come in figura seguente (figura 3.2).

Figura 3.2 – scheda PCB di ciascun modulo

Tuttavia viene sfruttata circa metà di questa scheda, in quanto, come detto prima, il convertitore flyback è sostituito con una sorgente di tensione esterna al modulo. Si riporta nell'Allegato lo schematico della parte inverter. Installando sulla scheda solo i componenti necessari al funzionamento dell'H-Bridge, il modulo presenta il seguente aspetto (figura 3.3).

Figura 3.3 – modulo H-Bridge

In figura 3.3 sono stati evidenziati i componenti fondamentali che costituiscono il modulo. Si andranno ora ad analizzare gli aspetti principali legati al suo funzionamento.

#### 3.2.2 **Bus DC**

Il bus DC del modulo (in viola in figura 3.3) è realizzato attraverso una morsettiera e quattro condensatori posti in serie. Ognuno di essi è caratterizzato da una capacità di  $330~\mu F$  e una tensione nominale di 160~V, pertanto la serie determina una capacità totale di circa  $80~\mu F$  e una tensione massima nominale di 640~V.

Il dimensionamento della capacità del bus DC andrebbe effettuato attraverso la seguente espressione:

$$C_{dc} = \frac{I_{dc}}{2\pi f \cdot \Delta V_{dc}} \tag{3.1}$$

La (3.1) tiene conto della corrente assorbita ( $I_{dc}$ ), della frequenza della tensione di alimentazione (f) e del ripple massimo di tensione consentito ( $\Delta V_{dc}$ ). Ipotizzando, come si dirà nei paragrafi successivi, che il modulo sia alimentato da un ponte raddrizzatore trifase, si ha una frequenza della tensione di alimentazione di 300 Hz. Inoltre si consideri una corrente massima di 1,5 A e un ripple massimo della tensione di alimentazione del 5%. La capacità totale a disposizione sul modulo, con queste specifiche, risulta accettabile.

#### 3.2.3 Gestione dei segnali di controllo

I segnali di controllo per il pilotaggio degli switch dell'H-Bridge vengono generati da un microcontrollore e sono acquisiti tramite due ricevitori di fibra ottica (in giallo in figura 3.3). Nella struttura di un H-Bridge, come visto nel Capitolo 1, sono presenti quattro switch: due superiori e due inferiori. Tuttavia gli switch inferiori sono comandati con un segnale logico che è il negato di quello che arriva agli switch superiori. Pertanto, quello che viene fatto in questo modulo, è utilizzare gli stessi segnali destinati agli switch superiori per quelli inferiori, previa inversione del loro valore logico. Tale inversione è effettuata tramite un componente integrato, ovvero un buffer invertente SN7406D (in rosso in figura 3.3), il quale è collegato ai ricevitori di fibra ottica in modo tale da negare una volta i segnali diretti agli switch superiori e negare due volte i segnali diretti a quelli inferiori (vedi figura 3.4).

Figura 3.4 – logica invertente dei segnali di controllo

Si adotta questa logica negata per via di come sono realizzati i ricevitori di fibra ottica: infatti, se venisse a mancare il segnale sui ricevitori, la loro uscita sarebbe alta. Questo causerebbe la chiusura degli interruttori alti, ma, per ragioni di sicurezza, si preferisce che tali interruttori siano aperti durante questa situazione.

Ciascun segnale in uscita dal buffer invertente viene poi inviato a un proprio trigger di Schmitt, preceduto da una resistenza di pull-up e una capacità: la capacità consente di introdurre un ritardo sul segnale, che poi viene "digitalizzato" grazie al trigger di Schmitt. Questo insieme (in verde in figura 3.3) ritarda il fronte di salita dei segnali (la discesa è più veloce per via delle soglie del trigger) e permette così di gestire la questione dei tempi morti direttamente via hardware, altrimenti sarebbe stato necessario un controllo degli stessi tramite microprocessore, con conseguente raddoppio dei ricevitori di fibra ottica (da due a quattro, cioè uno per switch).

Tutti questi circuiti di gestione del segnale appena elencati necessitano di una alimentazione stabile a 5 V continua. Tale alimentazione è fornita da un regolatore DC-DC (in blu in figura 3.3) del tipo 7805, che necessita a sua volta di un'alimentazione compresa nel range 10-35 V. Quest'ultima è fornita da un altro regolatore DC-DC (in azzurro in figura 3.3) del tipo LM2575, il quale, alimentato da una sorgente esterna al modulo, fornisce in uscita una tensione stabile a 15 V continua. La suddetta sorgente di tensione esterna, che quindi ha il compito di alimentare tutti i servizi ausiliari del modulo, è rappresentata da un alimentatore DC che viene collegato alla scheda tramite un apposito connettore (in rosa in figura 3.3). E' importante segnalare che tale alimentatore deve essere isolato rispetto a terra al fine di evitare la circolazione di correnti capacitive che si richiudono appunto tramite la terra degli alimentatori.

### 3.2.4 Modulo di potenza H-Bridge integrato

Il vero e proprio cuore dell'intero modulo è il circuito integrato PS22A76 della Mitsubishi Electric. Questo, come è possibile osservare in figura 3.5, è saldato sul retro del modulo.

Figura 3.5 – retro del modulo, in arancio il circuito integrato PS22A76

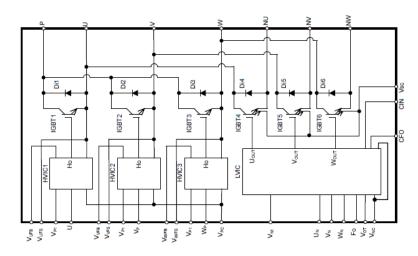

Tale componente dispone al suo interno di sei interruttori di potenza IGBT e dei circuiti di alimentazione/gestione dei loro gate (figura 3.6).

Figura 3.6 – struttura interna dell'integrato PS22A76

Quindi questo, avendo a disposizione tre rami, con due interruttori di potenza ciascuno, nasce come circuito integrato per la realizzazione di un inverter trifase. Tuttavia, in questo progetto, si sfruttano solo due rami, cioè quelli necessari alla realizzazione dell'H-Bridge, i quali rendono disponibile la loro tensione di output tramite una morsettiera.

Esistono varie versioni di questa tipologia di integrato, con vari limiti di tensione e varie taglie di corrente. Il PS22A76 accetta una tensione massima di ingresso di 800 V, mentre quella minima, per il corretto funzionamento, è di 350 V. Il massimo valore efficace della corrente che può essere continuativamente erogata è 25 A.

Questa serie della Mitsubishi Electric possiede inoltre una protezione contro la sottoalimentazione dei circuiti interni, una protezione contro i cortocircuiti e una contro le sovratemperature.

Nel datasheet sono presenti tutti i collegamenti e i componenti necessari al funzionamento dell'integrato, i quali sono stati fedelmente rispettati nel progetto del modulo. In particolare i suoi circuiti necessitano di una alimentazione in continua a 15 V, che, come si può notare dallo schematico (vedi Allegato), è fornita dal regolatore LM2575 descritto prima.

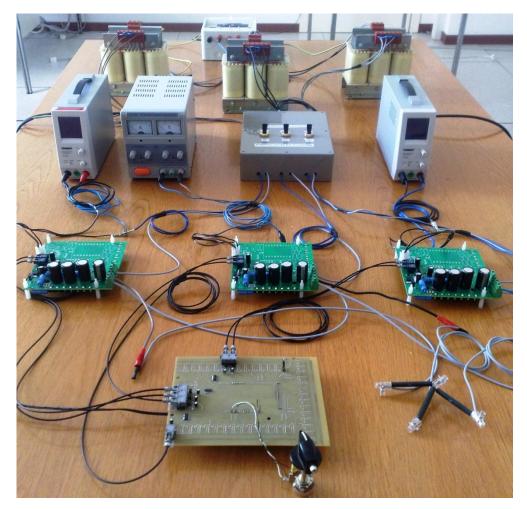

# 3.3 Alimentazione di potenza

In una configurazione di inverter multilivello Cascaded, i moduli H-Bridge, come detto nel Capitolo 1, necessitano di alimentazioni isolate. Pertanto, per la realizzazione di un inverter trifase a tre livelli, sono necessarie tre alimentazioni indipendenti e isolate. Si è deciso di realizzare tali alimentazioni attraverso tre trasformatori trifase di isolamento e tre ponti raddrizzatori trifase.

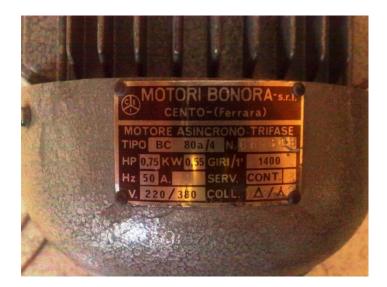

I trasformatori, appositamente acquistati presso un'azienda esterna, presentano i seguenti dati di targa:

Figura 3.7 – dati di targa dei trasformatori

Il rapporto di trasformazione è pressoché unitario (V<sub>2</sub>/V<sub>1</sub>=1.05 dai dati di targa, V<sub>2</sub>/V<sub>1</sub>=1.09 misurato), a meno di una piccola maggiorazione della tensione al secondario che compensa la caduta da vuoto a carico. Il collegamento a triangolo del primario consente di rendere indipendenti le fasi in caso di carico squilibrato. Il secondario invece è lasciato con i morsetti aperti, cioè è possibile, utilizzando l'apposita morsettiera, decidere liberamente tra il collegamento a stella o a triangolo. Il primo consente, con un'alimentazione concatenata di 400 V a primario, di ottenere una tensione a vuoto raddrizzata di circa 600 V, il secondo invece determina una tensione a vuoto raddrizzata di circa 350 V.

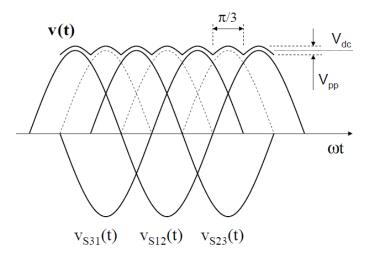

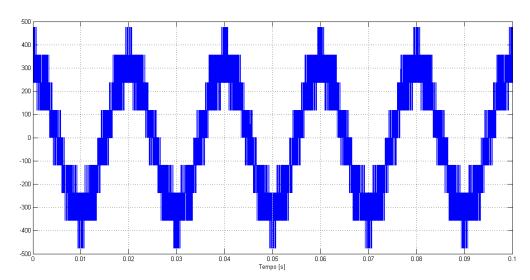

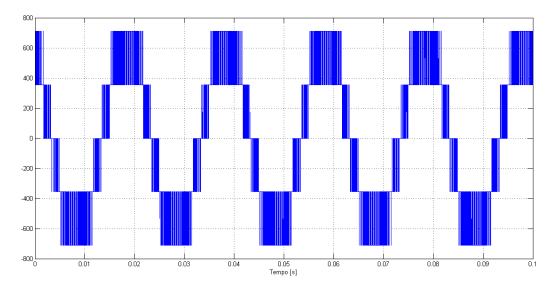

Le tre fasi in uscita da ciascun trasformatore vengono connesse a un rispettivo ponte raddrizzatore trifase da 25 A con attacco rapido. La tensione di output di ciascun ponte è rappresentata dall'inviluppo delle forme d'onda delle tensioni concatenate delle tre fasi (figura 3.8).

Figura 3.8 – tensioni concatenate e relativo inviluppo

Pertanto, se il sistema trifase di alimentazione dei ponti raddrizzatori è simmetrico con frequenza 50 Hz e di valore efficace  $V_S$ , si ottiene in uscita una tensione raddrizzata pulsante con 300 Hz di frequenza dell'armonica fondamentale e con valore massimo di tensione continua pari a  $\sqrt{2} \cdot V_S$ .

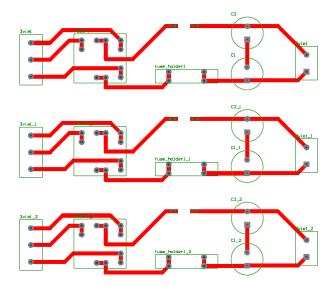

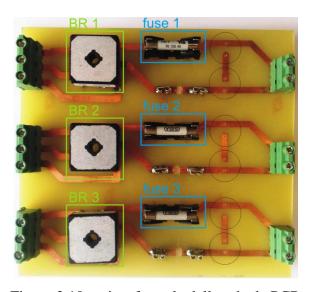

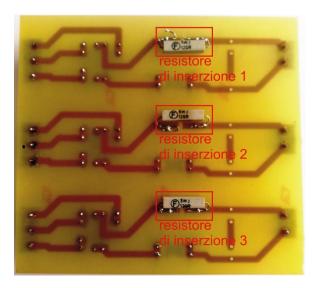

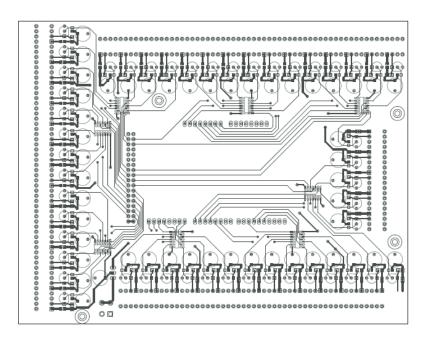

Il sistema dei tre ponti raddrizzatori indipendenti è realizzato su una scheda PCB progettata e realizzata nell'ambito di questo lavoro di tesi. Il progetto è stato eseguito attraverso il software di progettazione per circuiti stampati Altium (figura 3.9). Si è scelto di installare i ponti raddrizzatori su una scheda PCB in modo da poter aggiungere altri componenti in serie a essi, senza dover ricorrere a ingombranti collegamenti esterni.

Figura 3.9 – progetto della PCB per i ponti raddrizzatori

Il progetto prevede l'inserimento di un portafusibili in modo da proteggere i ponti raddrizzatori, le sottili piste di rame della PCB e i trasformatori a monte da eventuali sovracorrenti dovute a cortocircuiti o ad assorbimenti eccessivi da parte del carico. Il fusibile installato sulla scheda è un fusibile a intervento rapido di taglia 2 A, in modo da poter garantire un piccolo sovraccarico dei trasformatori e una maggiore tolleranza relativamente alle correnti di inserzione dei condensatori del bus DC. A tal proposito, per evitare che il fusibile salti durante l'alimentazione del bus DC, sarebbe necessario alimentare il sistema attraverso un trasformatore a rapporto variabile (VARIAC). Tuttavia tale soluzione risulta ingombrante e costosa. Pertanto il progetto prevede un resistore di inserzione che ha la funzione, durante la fase di carica dei condensatori, di limitare il conseguente picco di corrente. Tale resistore ha un valore di resistenza di 120  $\Omega$  e viene disinserito, una volta terminata la fase di carica, tramite degli interruttori che lo cortocircuitano. La scheda prevede inoltre la predisposizione per un'eventuale aggiunta di condensatori sul bus DC: sono presenti quattro reofori che consentono l'installazione di due condensatori in serie al fine di aumentare la capacità totale del bus DC.

Una volta terminato il progetto, è stato eseguito il processo di trasferimento a ultravioletti delle piste su una scheda fotoresistiva. Poi, attraverso soluzioni acide, si sono separate le piste di rame dalla superficie isolante, sono stati realizzati i reofori e si sono saldati tutti i componenti. Il risultato, è visibile nelle seguenti figure.

Figura 3.10 – vista frontale della scheda PCB

Figura 3.11 – retro della scheda PCB

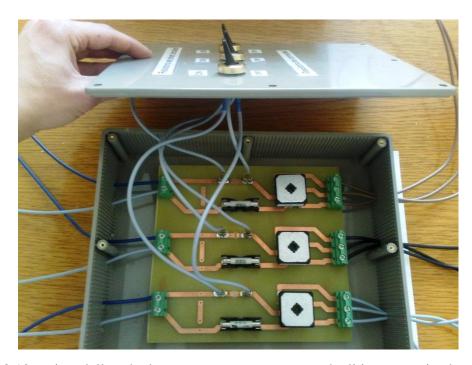

Tale scheda è stata alloggiata in un contenitore chiuso di materiale plastico, sul quale sono stati apportati dei fori per il passaggio dei cavi in modo da preservare la sicurezza degli operatori durante le operazioni di prova. Sul coperchio di tale contenitore sono stati installati tre interruttori (figura 3.12) che consentono di cortocircuitare la resistenza di inserzione una volta terminata la fase di carica.

Figura 3.12 – vista della scheda esternamente connessa e degli interruttori sul coperchio

### 3.4 Microcontrollore

#### 3.4.1 Architettura

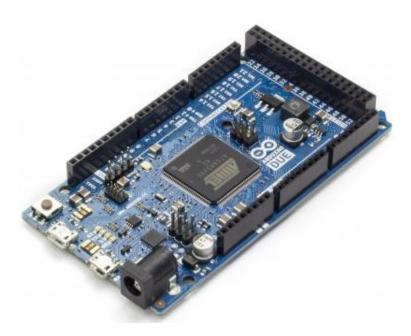

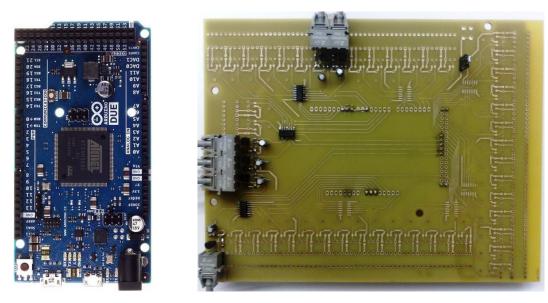

Per generare i segnali di controllo degli switch di ciascun modulo, si ricorre all'utilizzo di un microcontrollore. La scelta è ricaduta sulla Arduino DUE (vedi figura 3.13), una piattaforma open-source basata su un microcontrollore di tipo ARM a 32bit, il SAM3X8E ARM Cortex-M3 di Atmel.

Figura 3.13 – vista della scheda Arduino DUE

La scheda offre 54 input/output digitali, 12 input analogici con 12bit di risoluzione, 4 UARTs (porte seriali hardware), 2 output DAC (convertitori da analogico a digitale), 84 MHz di velocità di clock, 2 connettori USB, un connettore per l'alimentazione, un connettore ICSP, un connettore JTAG e un tasto di reset. Dei due attacchi USB quello con connessione micro-USB è quello nativo ed è in grado di funzionare come una periferica USB host, il che significa che è possibile connettere alla scheda altre periferiche USB come mouse, tastiera e smartphone. L'altra porta USB, quella con connettore di tipo B, è pensata invece a scopo di debug.

L'alimentazione può essere fornita attraverso:

- la connessione USB

- un alimentatore AC-DC connesso all'apposito DC-plug

- un pin di ingresso che accetta tensione nel range 7-12 V

Vi è la possibilità inoltre di utilizzare i due livelli di tensione presenti (3.3 V, 5 V) per alimentare un dispositivo esterno, connettendolo direttamente alla piattaforma tramite i due rispettivi pin e il pin di massa.

I principali vantaggi della Arduino DUE, rispetto alla sua versione precedente (Arduino Mega 2560), sono il processore più veloce (da 16 MHz a 84 MHz) e una maggiore risoluzione per i convertitori ADC-DAC (da 8 bit a 12 bit). Aumentano poi la memoria Flash per il codice del programma (da 256 KB a 512 KB) e la memoria RAM (da 8 KB a 96 KB).

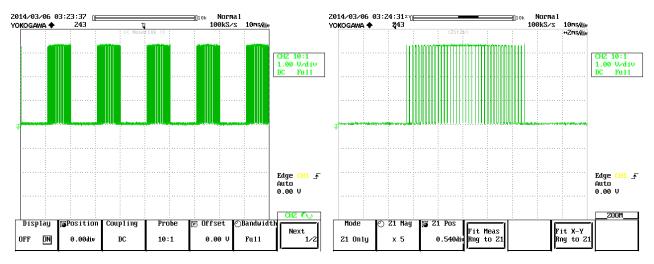

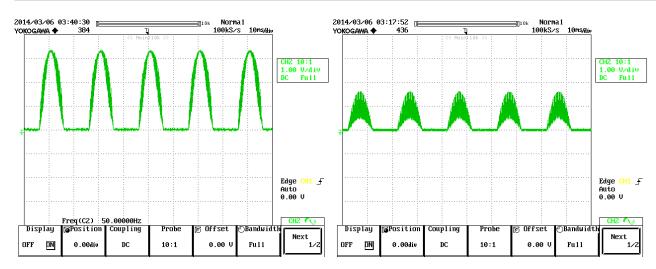

L'aspetto di maggiore interesse di questa piattaforma è che il processore possiede 9 canali a 32 bit per la PWM e 8 canali a 16 bit per la PWM con uscite complementari. Tuttavia solo una parte di questi canali vengono effettivamente sfruttati dalla scheda Arduino DUE: in riferimento alla PWM con uscite complementari, sono presenti 6 canali assegnabili a 12 pin fisici (6 PWMHx per le uscite alte e 6 PWMLx per le uscite basse). Proprio questi canali vengono sfruttati per il controllo dei moduli H-Bridge. Come detto al paragrafo 3.2, ciascun modulo possiede due ricevitori di fibra ottica, uno per ciascun ramo dell'H-Bridge. Quindi è necessario generare due segnali per ciascun modulo. Dovendo controllare separatamente tre moduli, il numero totale di segnali che il microcontrollore dovrà generare è sei. Si ricorda infatti che, nonostante il numero totale degli switch sia dodici, è necessario controllare solo la metà di essi, poiché gli interruttori bassi sono controllati con un segnale complementare a quello degli interruttori alti e tutto questo è gestito direttamente via hardware, senza dover ricorrere ad ulteriori pin o segnali di fibra ottica. Pertanto sono necessari sei pin fisici, corrispondenti a sei canali logici.

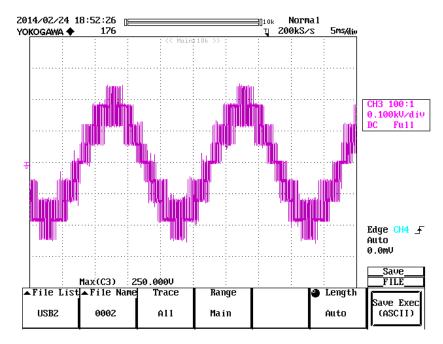

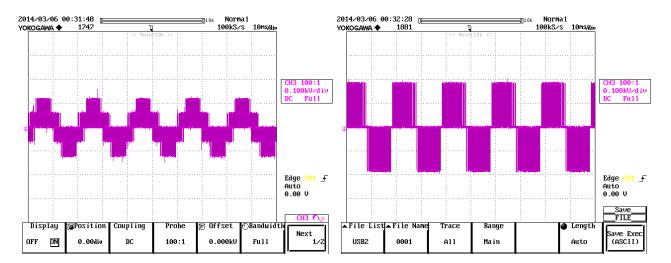

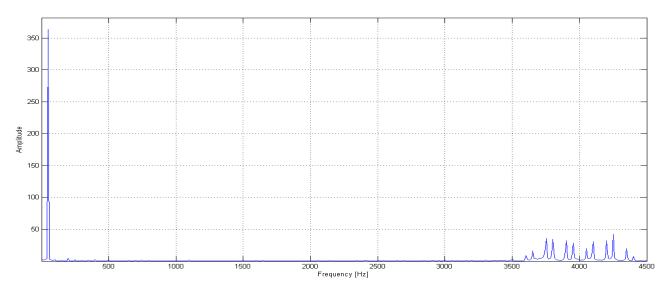

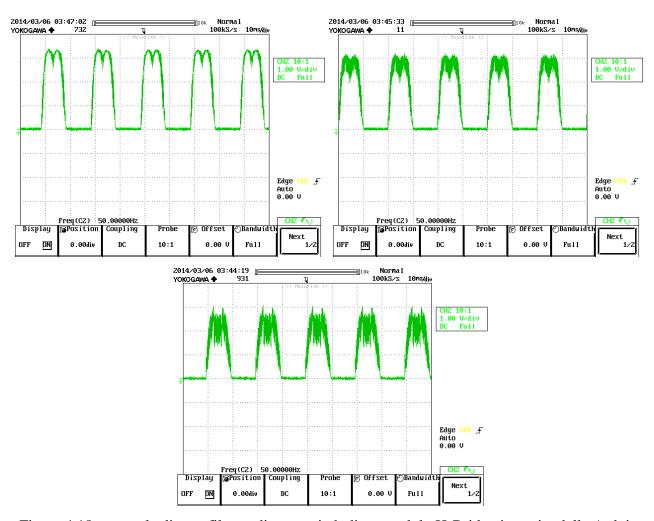

#### 3.4.2 Controllo e codice