# ALMA MATER STUDIORUM UNIVERSITA' DI BOLOGNA SECONDA FACOLTA DI INGEGNERIA CON SEDE A CESENA

CORSO DI LAUREA IN INGEGNERIA ELETTRONICA E DELLE TELECOMUNICAZIONI PER LO SVILUPPO SOSTENIBILE

## PROGETTO E REALIZZAZIONE DI RIFERIMENTI IN TENSIONE SIMMETRICI IN TECNOLOGIA CMOS

Elaborato in:

SENSORI E ATTUATORI LM

II Sessione A.A. 2011/2012

**Relatore:** Marco Tartagni

**Candidato:** Fiorini Paolo

Correlatori:

Federico Thei Marco Crescentini Marco Bennati

## Indice

| Capitolo 1 : Introduzione                                 | pag. | 5  |

|-----------------------------------------------------------|------|----|

| Capitolo 2 : Analisi della letteratura                    | pag. | 9  |

| Capitolo 3 : Possibili implementazioni                    | pag. | 11 |

| Capitolo 4 : Analisi dei circuiti implementativi          | pag. | 15 |

| 4.1 IPTAT Current generator                               | pag. | 16 |

| 4.2 ICTAT Current generator                               | pag. | 26 |

| 4.3 Bandgap voltage reference                             | pag. | 34 |

| Capitolo 5 : Implementazione CMOS delle architetture      |      |    |

| proposte                                                  | pag. | 39 |

| 5.1 Voltage reference current                             |      |    |

| generation based                                          | pag. | 40 |

| 5.2 Voltage reference bandgap based                       | pag. | 49 |

| Capitolo 6 : Simulazioni                                  | pag. | 55 |

| Capitolo 7 : Implementazione del layout                   | pag. | 69 |

| Capitolo 8 : Misure, possibili improvements e conclusioni | pag. | 77 |

| 8.1 Misure                                                | pag. | 77 |

| 8.2 Possibili miglioramenti                               | pag. | 80 |

| 8.3 Conclusioni                                           | pag. | 88 |

| Bibliografia                                              | pag. | 89 |

| Ringraziamenti                                            | pag. | 90 |

## Capitolo 1

#### Introduzione

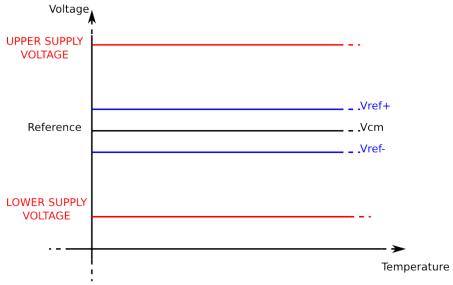

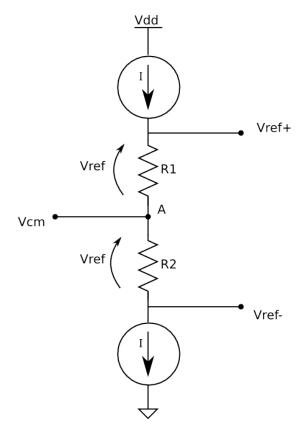

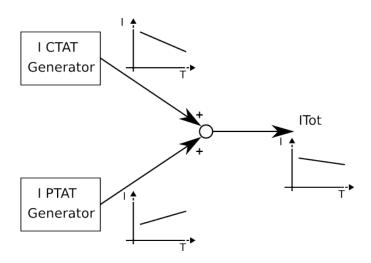

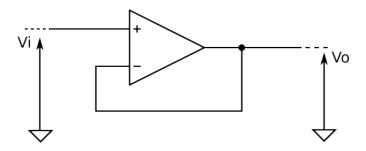

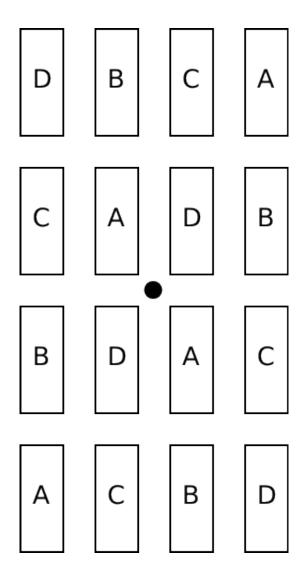

L'obiettivo della tesi e' lo studio, il progetto e la realizzazione su silicio di un riferimento in tensione simmetrico stabile e in temperatura. Cio' che si vuole ottenere e' schematicamente rappresentato in fig.1.1

Figura 1.1: Rappresentazione grafica dei riferimenti in tensione simmetrici

Le due tensioni Vref+ e Vref- devone essere il piu possibile stabili in temperatura e mantenere un elevato livello di simmetria.

La tesi tratta in particolare del progetto e del confronto fra due architetture di tipo diverso per scegliere la migliore da realizzare su silicio; verranno affrontati gli argomenti dell'analisi in temperatura delle tensioni e dei metodi migliori per la realizzazione su silicio.

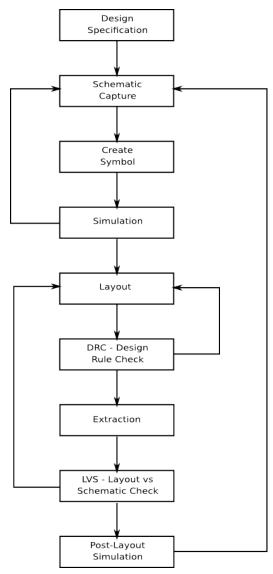

Il flusso di progetto adottato in questa tesi e' mostrato in fig1.2

Figura 1.2: Flusso di progetto di un circuito su silicio

Partendo dalle specifiche viene creato lo schematico e successivamente simulato.

Le simulazioni possono essere di due tipi: simulazioni funzionali, che permettono la verifica del corretto comportamento del circuito, e simulazioni montecarlo utili per comprendere la sensibilita del circuito alla intrinseca stocasticita' del processo di realizzazione.

Infatti i componenti su silicio vengono realizzati con delle incertezze descrivibili attraverso variabili aleatorie.

Una volta simulato si passa alla realizzazione del layout su silicio andando a disporre i singoli componenti e effettuando i collegamenti corretti.

Termianata la realizzazione del layout vengono forniti dal cad strumenti per la verifica del rispetto delle regole di disegno, quali per esempio la dimensione minima delle interconnessioni metalliche o la distanza minima dei componenti.

Il secondo strumento fornito dal cad verifica che i collegamenti effettuati sul layout corrispondano ai collegamenti nello schematico.

Se i due controlli vanno a buon fine si puo passare all'estrazione del circuito.

Il cad puo infatti andare a calcolare tutti gli elementi parassiti del circuito, basandosi sul layout, permettendo cosi di verificare come questi inlfuenzino la rete inizialmente simulata.

La prima parte, dell'attivita' di tesi, descritta nel capitolo successivo, e' stata svolta ricercando pubblicazioni sul sito della IEEE per analizzare le soluzioni disponibili e ottenere le basi teoriche per il progetto.

## Capitolo 2

#### Analisi della letteratura

Analizzando la letteratura presente sul sito della IEEE e' risultato evidente come il problema dei riferimenti in tensione e in corrente stabili in temperatura sia un problema ampiamente discusso.

Per quanto riguarda i riferimenti in tensione, il tipo di circuito maggiormente trattato risulta essere il bandgap voltage reference capace di fornire in uscita una tensione con bassa variabilita' in temperatura.

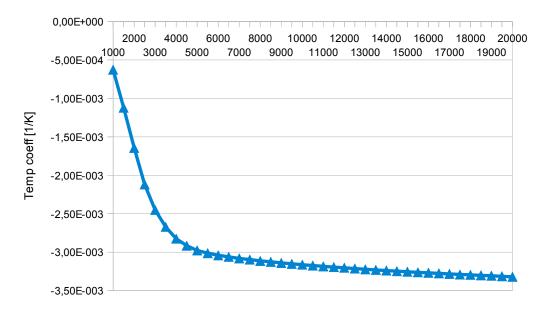

Il bandagap funziona effettuando la somma della tensione ai capi di un diodo, che presenta un coefficiente di temperatura negativo, con una tensione multipla tella tensione termica, che ha un coefficiente di temperatura positivo, in modo da ottenere così una tensione con coefficiente di temperatura quasi nullo.

Tale circuito e', pero', in grado di generare solamente un livello di tensione stabile, tipicamente del valore di 1.2V, ma non permette la generazione di due tensioni simmetriche.

Anche per quanto riguarda i riferimenti in corrente stabili in

temperatura si trovano molti riferimenti nella letteratura. La stabilita' della corrente viene ottenuta, in modo analogo al bandgap, sommando due correnti: una con coefficiente di temperatura positivo rispetto alla temperatura assoluta (PTAT) e uno con coefficente negativo rispetto alla temperatura assoluta (CTAT).

Tale somma permette di ottenere una corrente con coefficiente di temperatura nullo.

Analizzando le pubblicazioni presenti comunque non é stato trovato alcun circuito in grado di generare due tensioni simmetriche rispetto a un riferimento fissato garantendone la simmetria e la stabilita' in temperatura.

Le nozioni apprese hanno pero' permesso lo sviluppo di due tipi di architetture che sono poi state confrontate.

La prima architettura basa il proprio funzionamento su un riferimento generato tramite bandgap; la seconda architettura basa il suo funzionamento sui circuiti in grado di generare le correnti con coefficiente di temperatura positivo e negativo.

Le due diverse architetture sono poi state confrontate basandosi su quei parametri che, durante la lettura delle pubblicazioni, sono risultati importanti per valutare le prestazioni dei riferimenti in tensione.

Tali parametri e le due architetture sviluppate saranno poi descritte successivaente nel capitolo 3.

#### Capitolo 3

### Possibili implementazioni

Nel capitolo vengono proposti due diversi approcci implementativi; il primo si basa su un bandgap voltage reference mentre il secondo si basa su un circuito in grado di generare una corrente con caratteristica in temperatura nota.

I due circuiti sono poi stati simulati e confrontati su parametri importanti per i riferimenti in tensione al fine di decidere quale approccio fosse il migliore da implementare su silicio.

Il primo parametro di confronto e' stata la potenza dissipata dai due circuiti. Tale parametro prende importanza in tutti quei sistemi in cui la potenza dissipabile e' una risorsa scarsa per via della presenza di fonti di alimentazione esauribili nel tempo; ecco quindi che la potenza dissipata dal riferimento in tensione deve essere il piu basso possibile.

Il secondo parametro preso in considerazione e' il PSRR (Power Supply Rejection Ratio) definito come:

$$PSRR = \frac{REFERENCE\ RIPPLE}{SUPPLY\ RIPPLE}$$

(3.1)

o in dB:

$$PSRR_{dB} = 20 \cdot \log \left( \frac{REFERENCE\ RIPPLE}{SUPPLY\ RIPPLE} \right)$$

(3.2)

parametro che indica l'insensibilita' del riferimento in tensione rispetta a disturbi presenti sull'alimentazione del circuito.

Il terzo parametro e' il livello di simmetria delle tensioni ottenute. Al fine di valutare tale grandezza, se si considera il grafico di fig 1.1, e' stata individuata la grandezza:

$$\Delta V_{ref} = (V_{ref} + V_{cm}) - (V_{cm} - V_{ref})$$

(3.3)

indice appunto di quanto vale la dissimmetria delle due tensioni  $V_{\text{ref+}}$  e  $V_{\text{ref-}}$ .

Come ultimo parametro di confronto fra i due circuiti, visto che l'obiettivo e' decidere quale sia l'architettura migliore da implementare su silicio, sono state valutatate, tramite simulazioni MonteCarlo, le fluttuazioni delle due tensioni dovute ai parametri statistici legati alle incertezze del processo di realizzazione.

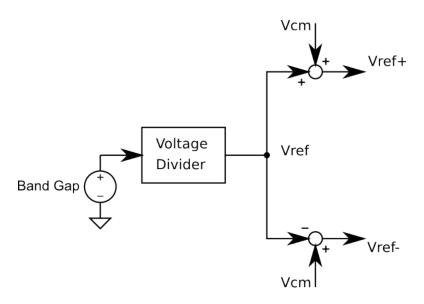

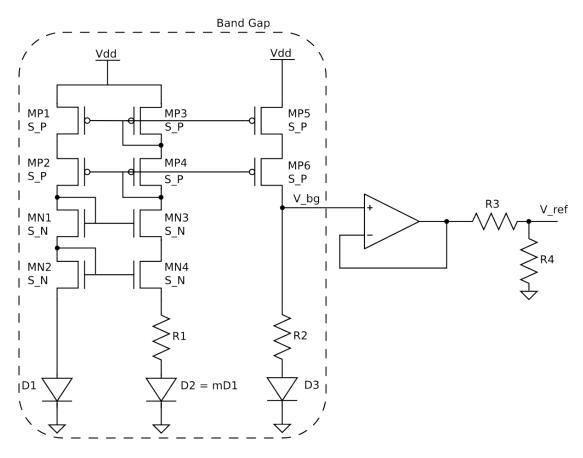

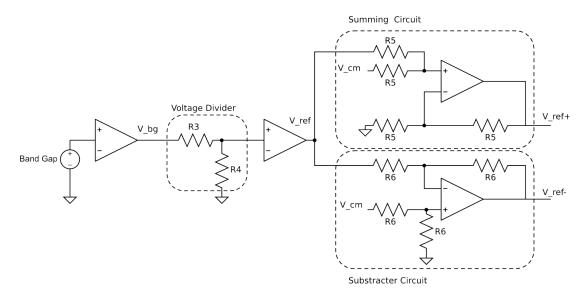

Vediamo quali sono le soluzioni proposte. La prima si basa su un bandgap voltage reference ,circuito in grado di generare una tensione stabile in temperatura.

Lo schema di principio viene mostrato in fig.3.1.

Figura 3.1: Principio di funzionamento del riferimento in tensione basato sul Band Gap

Come si puo notare la tensione generata dal bandgap (generalmente intorno a 1.2V) deve essere scalata al fine di ottenere una tensione  $V_{\rm ref}$  pari a  $450~{\rm mV}$  che va poi sommata e sottratta alla  $V_{\rm cm}$  per ottenere i due riferimenti simmetrici.

Nel capitolo 4 verra' spiegato come implementare un Band Gap e nel capitolo 5 verra' mostrato l'effettivo schematico del riferimento.

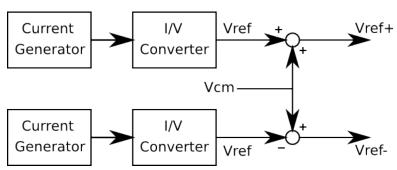

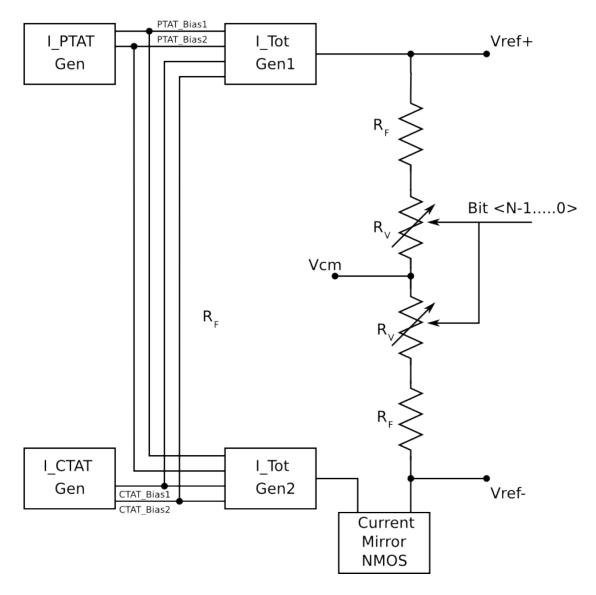

Passiamo ora a mostrare la seconda possibile implementazione: di seguito se ne riporta lo schema a blocchi (fig 3.2).

Figura 3.2: Schema di principio del riferimento in tensione basato sulle correnti

L'idea e' quella di generare una corrente in modo tale da

compensare la caratteristica in temperatura del convertitore I/V scelto e ottenere così due tensioni Vref , una positiva e una negativa, uguali in modulo, che siano stabili in temperatura.

Queste tensioni saranno poi sommate con la  $V_{\text{cm}}$  per ottenere la  $V_{\text{ref+}}$  e la  $V_{\text{ref-}}$ .

Successivamente verra' spiegato come ottenere le correnti e il tipo di convertitore I/V usato.

#### Capitolo 4

## Analisi dei circuiti implementativi

L'obiettivo del capitolo e' l'analisi teorica di quei circuiti che vanno a costruire il core delle soluzioni proposte nel capitolo 3.

Oltre alla trattazione teorica vengono anche presentate le simulazioni eseguite al fine di verificare le funzionalita' dei circuiti e ottenere maggiore conoscenza delle variazioni in funzione dei parametri.

In particolare si analizzera' un circuito in grado di ottenere una corrente con coefficiente di temperatura PTAT (*Positive To Absolute Temperature*) (cap 4.1), un circuito in grado di ottenre una corrente con coefficiente di temperatura CTAT (*Complementary To Absolute Temperature*) (cap 4.2) e un riferimento di tensione stabile in temperatura ottenuto attraverso un *bandgap voltage reference* (cap 4.3)

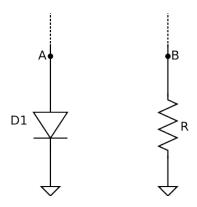

#### 4.1 IPTAT Current generator

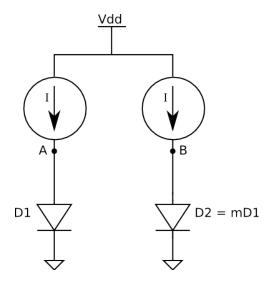

Al fine di generare una corrente PTAT (Positive To Absolute Temperature) vengono sfruttate le caratteristiche del generatore di tensione termica  $V_t$  mostrato in fig. 4.1.1.

Figura 4.1.1: Schema di principio di un generatore di Vt

Il circuito e' composto da due generatori di corrente ideali che impongono una corrente uguale in entrambi i rami e due diodi D1 e D2, dove D2 ha un fattore di forma m-volte piu' grande di D1. Da notare che per implementare il diodo D2 e' sufficente collegare m diodi delle dimensioni di D1 in parallelo.

Andiamo ora a calcolare la quantita'  $\Delta V_D$  definita come la differenza di tensione fra i punti A e B:

$$\Delta V_{D} = V_{A} - V_{B} = V_{DI} - V_{D2} \tag{4.1.1}$$

Avendo imposto una corrente costante e uguale in entrambi i rami, al fine di calcolare la tensioni ai capi dei diodi D1 e D2, e' sufficente invertire la legge esponenziale che lega tensione e corrente nel diodo ottennendo cosi:

$$V_{DI} = V_{t} \cdot \ln\left(\frac{I}{I_{S}}\right) \tag{4.1.2}$$

$$V_{D2} = V_t \cdot \ln\left(\frac{I}{m \cdot I_s}\right) \tag{4.1.3}$$

Andando a fare la differenza fra le due tensioni risulta che:

$$\Delta V_{D} = V_{t} \cdot \ln(m) \tag{4.1.4}$$

La  $\Delta V_D$  risulta quindi essere proporzionale alla tensione termica  $V_t$ . Sfruttando questo risultato e' possibile evolvere il circuito al fine di generare una corrente PTAT.

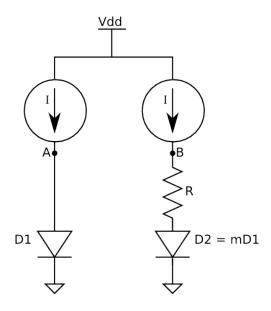

Innanzitutto si pone un resistore R in serie al diodo D2, ottenendo il circuito di fig.4.1.2

Figura 4.1.2: Evoluzione del circuito generatore di Vt mostrato in fig. I

Se si impone che la tensione ai punti A e B sia uguale possiamo dire che la caduta di tensione sulla resistenza R risulta essere:

$$V_R = V_t \cdot \ln(m) \tag{4.1.5}$$

infatti:

$$V_A = V_B = V_{DI}$$

(4.1.6)

e quindi:

$$V_R = V_B - V_{D2} = V_{DI} - V_{D2} = \Delta V_D$$

(4.1.7)

Al fine di ottenere l'ugualianza dei potenziali dei punti A e B e l'ugualianza delle correnti in entrambi i rami del circuito viene inserita, come generatore di corrente, una rete di polarizzazione realizzata con transistori mos.

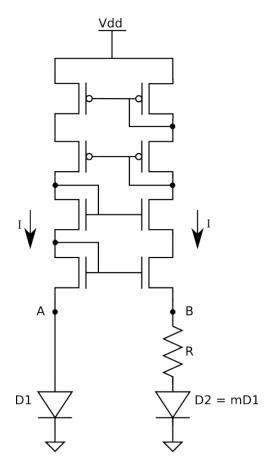

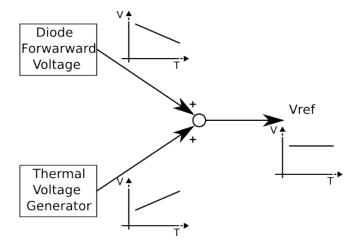

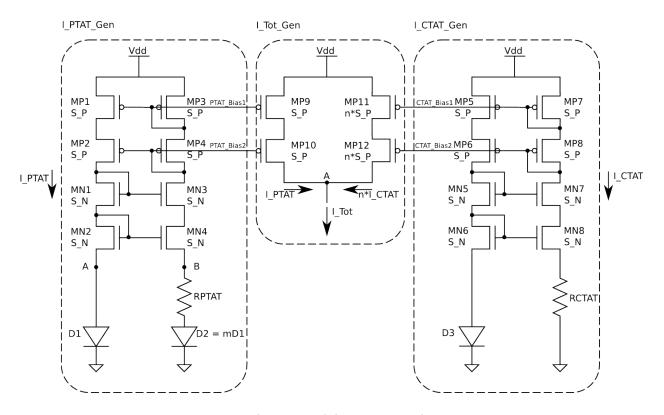

Tale rete risulta essere uno specchio di corrente in configurazione Wilson. In fig.4.1.3 viene mostrato il circuito finale utilizzato per la generazione della corrente PTAT.

Figura 4.1.3: Circuito per la generazione di una corrente PTAT

Lo specchio di corrente in configurazione Wilson impone l'ugualianza delle tensioni dei punti A e B e delle correnti che circolano nei due diodi; in questo modo sono state soddisfatte entrambe le ipotesi fondamenteli per il corretto funzionamento del circuito.

Come detto precedentemente, nella (4.1.5), la tensione ai capi della resistenza, in queste condizioni, risulta essere multipla di  $V_{\rm t}$ . La corrente che circola sui diodi puo' quindi essere calcolata facilmente, applicando la legge di Ohm, come:

$$I = V_t \cdot \frac{\ln(m)}{R} \tag{4.1.8}$$

Andiamo ora ad analizzare la dipendenza di questa corrente

dalla temperatura. Supponiamo quindi che tale andamento sia esprimibile, approssimando al primo ordine, dalla seguente formula:

$$I(T) = I_0 \cdot (1 + \alpha_I \cdot (T - T_0))$$

(4.1.9)

con  $\alpha_{I,}$  coefficiente di temperatura della corrente, definito come:

$$\alpha_I = \frac{1}{I_0} \cdot \frac{\partial I}{\partial T}_{T = T_0} \tag{4.1.10}$$

All'interno della (4.1.8), che esplicita la corrente, ci sono due grandezze che variano al variare della temperatura, la resistenza e la tensione termica. Approssimando al primo ordine la funzione che lega la resistenza alla temperatura possiamo dire che:

$$R(T) = R_0 \cdot (1 + \alpha_R \cdot (T - T_0)) \tag{4.1.11}$$

con  $\alpha_R$ , coefficiente di temperatura della resistenza, definito come:

$$\alpha_R = \frac{1}{R_0} \cdot \frac{\partial R}{\partial T}_{T=T_0} \tag{4.1.12}$$

In seguito la dipendenza della resistenza dalla temperatura non verra' piu' scritta in maniera esplicita.

Per quanto riguarda la tensione termica la sua dipendenza dalla temperatura e' espressa da :

$$V_t = \frac{K \cdot T}{q} \tag{4.1.13}$$

Dove K e' la costante di Boltzman, T è la temperatura espressa in gradi Kelvin e q è la carica dell'elettrone.

Il coefficiente di temperatura  $\alpha_I$  risulta essere facilmente

determinabile andando a calcolare la derivata della corrente in  $T_0$  e ,successivamente, dividendola per il valore di corrente che circola nel circuito a temperatura  $T_0$  cioe' a temperatura ambiente. Si ottiene che:

$$\frac{\partial I}{\partial T} = \frac{K}{a \cdot R^2} \cdot \ln(m) \cdot (R - \frac{\partial R}{\partial T} \cdot T) \qquad (4.1.14)$$

che calcolata in T<sub>0</sub> risulta essere:

$$\frac{\partial I}{\partial T}_{T=T_0} = \frac{I_0}{T_0} - I_0 \cdot \frac{1}{R_0} \cdot \frac{\partial R}{\partial T}_{T=T_0}$$

(4.1.15)

Il coefficiente di temperatura della corrente  $\alpha_I$  puo' essere espresso dalla seguente formula:

$$\alpha_I = \frac{1}{T_0} - \frac{1}{R_0} \cdot \frac{\partial R}{\partial T_{T=T_0}} = \frac{1}{T_0} - \alpha_R \qquad (4.1.16)$$

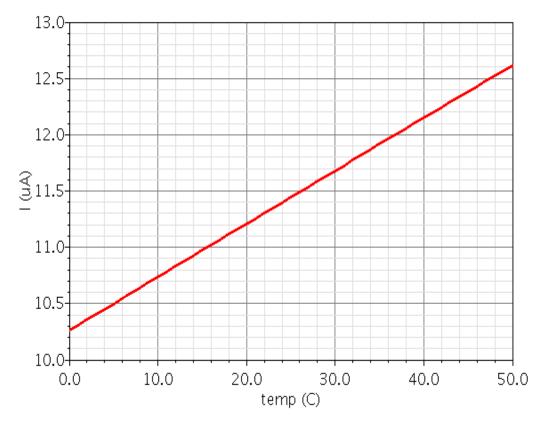

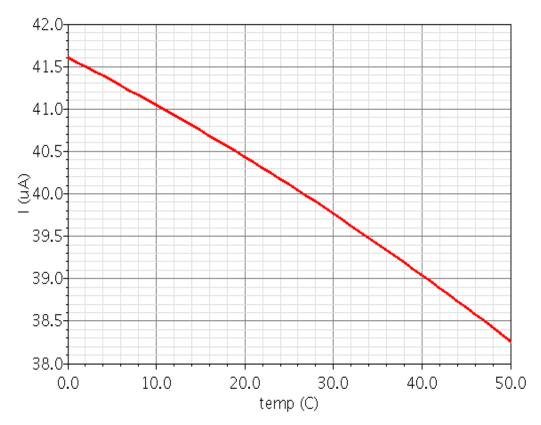

Il circuito di fig.4.1.3 e' stato simulato ed il risultato della simulazione e' riportato in fig.4.1.4.

Cosiderando una temperatura ambiente di  $27^{\circ}C$  (300K) e sapendo, attrverso i manuali di del software di simunlazione, che il coefficiente di temperatura della resistenza vale circa 900 ppm,  $\alpha_{\rm I}$  risulta essere positivo.

Figura 4.1.4: Andamento della corrente in funzione della temperatura

Le simulazioni ottenute sono perfettamente in accordo con quanto detto fino ad ora nella trattazione teorica; la corrente risulta avere un coefficiente di temperatura positivo e il valore di corrente alla temperatura ambiente di 27°C (300K) risulta calcolabile in modo preciso usando la (4.1.8).

Successivamente alla verifica delle funzionalita' del circuito e' seguita una caratterizzazione piu approfondita al fine di verificare le formule teoriche ed ottenere una maggiore conoscenza del comportamento del circuito stesso in funzione dei suoi parametri. In particolare sono stati analizzati:

- 1. Variazione della corrente nominale al variare del parametro m;

- 2. Variazione del valore della derivata della corrente rispetto alla temperatura (pendenza della retta) al variare del valore di resistenza;

3. Variazione del coefficiente di temperatura della corrente al variare della resistenza.

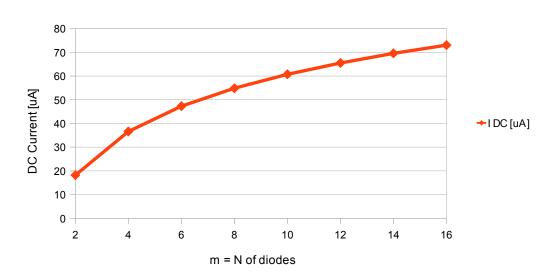

Per quanto riguarda il punto uno sono state effettuate simulazioni del circuito con m = 2,4,8,16 ed i risultati ottenuti sono riportati in fig.4.1.5

#### DC current vs N of diodes

Figura 4.1.5: Andamento del valore di corrente a temperatura ambiente in funzione del fattore m = numero di diodi.

In totale accordo con la (4.1.8) si nota come il valore di corrente a temperatura ambiente segua un andamento logaritmico all'aumentare delle dimensioni del diodo D2 (come gia detto ottenibile grazie a m diodi D1 in parallelo).

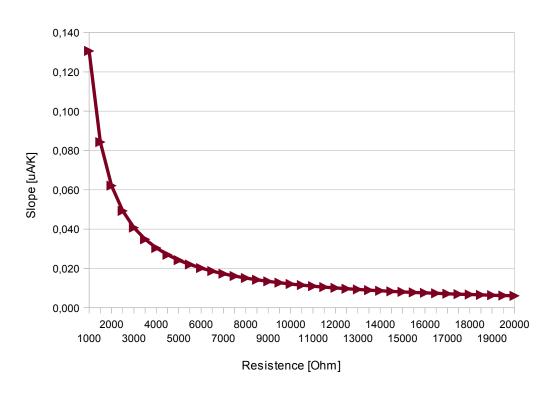

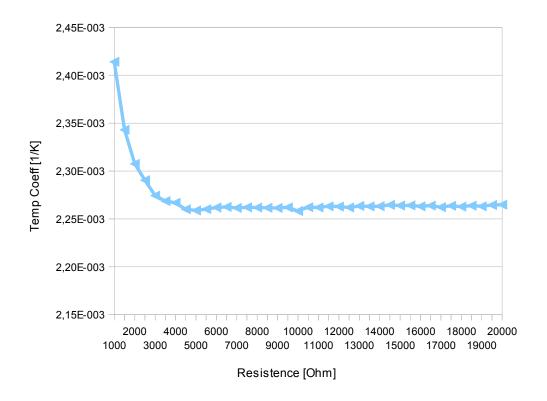

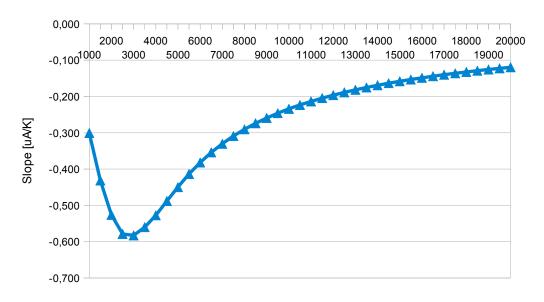

Cio' implica che non ha senso aumentare troppo il fattore m perche', oltre alla maggiore occupazione di area, arrivati a una certa soglia, i cambiamenti sul valore di corrente non sarebbero piu apprezzabili. Per quanto riguarda i punti 2 e 3 sono state effettuate simulazioni modificando il valore della resistenza R posta in serie a D2 nel circuito in fig.4.1.3 dal valore iniziale di  $1K\Omega$  al valore finale di  $20K\Omega$ .

#### Slope vs Resistence value

Figura 4.1.6: Andamento della pendenza della corrente IPTAT in funzione della resistenza

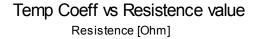

#### Temp. Coeff vs Resistence value

Figura 4.1.7: Andamento del coefficiente di temperatura in funzione della resistenza

Il grafico in fig.4.1.6 evidenzia il legame espresso nella (4.1.14) di proporzionalita' inversa fra valore della pendenza della retta cioe' della derivata della tensione rispetto alla corrente e valore di resitenza presente nel circuito.

Si noti come per valori di resistenza superiori a  $5K\Omega$ , eventuali incertezze sul valore nominale della resistenza, dovuti al processo di realizzazione su silicio del circuito, influenzino meno la pendenza della corrente ottenuta.

Il grafico in fig.4.1.7 mostra come, in accordo con la (4.1.16), il coefficiente di temperatura della corrente  $\alpha_I$  rimane pressoche' costante. Da notare come sia intuitivamente facile spiegare la dipendenza vista in fig.4.1.6; all'aumentare della resistenza

diminuisce la corrente a temperatura ambiente ma, visto che il coefficiente di temperatra della corrente altro non e' che la variazione relativa di corrente rispetto alla temperatura, affinche' esso rimanga costante anche la pendenza della retta deve diminuire con l'aumentare della resistenza.

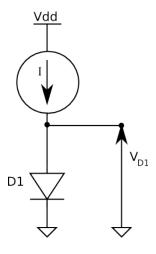

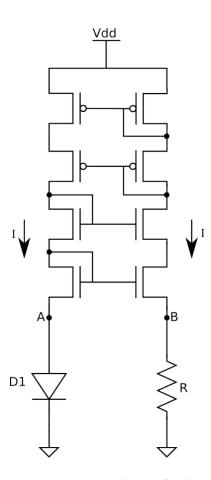

#### 4.2 ICTAT Current generator

Al fine di generare una corrente CTAT (Complementary To Absolute Temperature) vengono sfruttate le caratteristiche della tensione ai capi di un diodo polarizzato direttamente con una corrente costante. Dato il circuito di fig. 4.2.1:

Figura 4.2.1: Diodo polarizzato con una corrente costante

avendo imposto una corrente costante I la tensione ai capi del diodo D1 risulta essere:

$$V_{DI} = V_i \cdot \ln(\frac{I}{I_s}) \tag{4.2.1}$$

Sviluppando al primo ordine la dipendenza di tale tensione dalla temperatura si ottiene:

$$V_{DI}(T) = V_{DI}(T_0) \cdot (1 + \alpha_V \cdot (T - T_0)) \tag{4.2.2}$$

con  $\alpha_V$  coefficiente di temperatura della tensione definito come:

$$\alpha_V = \frac{1}{V_{DI}(T_0)} \cdot \frac{\partial I}{\partial T_{T=T_0}}$$

(4.2.3)

Per calcolare il coefficiente di temperatura della tensione ai capi del diodo bisogna quindi derivare la (4.2.1) rispetto alla temperatura. E' dunque necessario conoscere quali sono le grandeze che dipendono dalla temperatura al suo interno.

Tali grandezze sono la tensione termica  $V_t$  e la corrente  $I_s$ . Per quanto riguarda la tensione termica, la sua dipendenza dalla temperatura risulta essere espressa dalla formula:

$$V_t = \frac{K \cdot T}{q} \tag{4.2.4}$$

Per quanto riguarada la corrente  $I_s$ , la sua dipendenza dalla temperatura risulta essere piu' complicata; semplificando si assume che la corrente di saturazione inversa del diodo sia proporzionale alla mobilita degli elettroni  $\mu$ , alla temperatura T e alla concentrazione intrinseca di portatori  $n_i$ . Si puo' quindi scrivere che:

$$I_{S} \propto \mu \cdot K \cdot T \cdot n_{i}^{2} \tag{4.2.5}$$

A loro volta  $\mu$  e  $n_i$  dipendono dalla temperatura e la loro dipendenza puo essere cosi' esplicitata:

$$\mu = \mu_0 \cdot T^r \tag{4.2.6}$$

con r che tipicamente vale -3/2, e:

$$n_i^2 = T^3 \cdot e^{\frac{-Eg}{K \cdot T}} \tag{4.2.7}$$

E' possibile quindi scrivere la formula definitiva che esplicita la dipendenza di  $I_s$  dalla temperatura :

$$I_S \propto \mu_0 \cdot K \cdot T^{(4+r)} \cdot e^{\frac{-E_g}{K \cdot T}}$$

(4.2.8)

Esplicitata ogni dipendenza dalla temperatura all'interno della (4.2.1) e' possibile calcolare la sua derivata rispetto alla temperatura stessa:

$$\frac{\partial V_{DI}}{\partial T} = \frac{\partial V_t}{\partial T} \cdot \ln(\frac{I}{I_S}) - \frac{V_t}{I_S} \cdot \frac{\partial I_S}{\partial T}$$

(4.2.9)

con:

$$\frac{\partial I_s}{\partial T} = \mu_0 \cdot K \cdot e^{\frac{-Eg}{K \cdot T}} \cdot \left(\frac{4+r}{T} + \frac{Eg}{K \cdot T^2}\right) \tag{4.2.10}$$

ottenuta derivando la (4.2.8) rispetto alla temperatura.

Sostituendo la (4.2.10) nella (4.2.9) e svolgendo i calcoli e' possibile scrivere :

$$\frac{\partial V_{DI}}{\partial T} = \frac{V_{DI} - (4+r) \cdot V_t - \frac{Eg}{q}}{T} \tag{4.2.11}$$

Se si effettuano i calcoli con  $V_{\rm D1}=750{\rm mV},~r$  pari a -3/2 e temperatura T di 300K (temperatura ambiente) risultera' una derivata

della tensione rispetto alla temperatura negativa. Essendo  $\alpha_V$  definito dalla (4.2.3) risulta evidente che anche esso sara' negativo.

Vediamo ora come sfruttare questi risultati per generare una corrente con coefficiente di temperatura negativo. Supponiamo di avere il circuito di fig.4.2.2.

Figura 4.2.2: Schema per la generazione di ICTAT

Imponendo che la tensione nei punti A e B sia la stessa si ottine che:

$$V_A = V_B = V_{DI} = V_R$$

(4.2.12)

e di consegunza il valore di corrente sul resistore puo' essere calcolato come:

$$I_R = \frac{V_R}{R} = \frac{V_{DI}}{R}$$

(4.2.13).

Esplicitiamo la dipendenza di tale corrente dalla temperatura e supponendo che sia approssimabile al primo ordine, avremo che:

$$I(T) = I_0 \cdot (1 + \alpha_I \cdot (T - T_0))$$

(4.2.14)

con  $\alpha_I$  coefficiente di temperatura della corrente definito come:

$$\alpha_I = \frac{1}{I_0} \cdot \frac{\partial I}{\partial T}_{T = T_0} \tag{4.2.15}$$

Calcoliamo quindi la derivata della (4.2.13) dove sappiamo che sia la tensione  $V_{\rm D1}$  che la resistenza R dipendono dalla temperatura; in paticolare la tensione ai capi del diodo presenta un coefficiente di temperatura negativo come risulta dalla trattazione precedente e la resistenza ha una dipendenza dalla temperatura approssimabile al primo ordine come:

$$R(T) = R_0 \cdot (1 + \alpha_R \cdot (T - T_0)) \tag{4.2.16}$$

con  $\alpha_R$  coefficiente di temperatura della resistenza definito come:

$$\alpha_R = \frac{1}{R_0} \cdot \frac{\partial R}{\partial T}_{T = T_0} \tag{4.2.17}$$

otteniamo che:

$$\frac{\partial I}{\partial T} = \frac{1}{R^2} \cdot \left( R \cdot \frac{\partial V_{DI}}{\partial T} - V_{DI} \cdot \frac{\partial R}{\partial T} \right) \tag{4.2.18}$$

che calcolata per  $T = T_0$ :

$$\frac{\partial I}{\partial T}_{T=T_0} = \frac{1}{R_0^2} \cdot \left( R_0 \cdot \frac{\partial V_{DI}}{\partial T}_{T=T_0} - V_{DI} \cdot \frac{\partial R}{\partial T}_{T=T_0} \right) \tag{4.2.19}$$

Il coefficiente di temperatura della corrente puo quindi essere espresso dalla seguente formula:

$$\alpha_I = \frac{1}{V_{DI}} \cdot \frac{\partial V_{DI}}{\partial T} - \frac{1}{R_0} \cdot \frac{\partial R}{\partial T} = 0$$

(4.2.20)

Analizzando tale espressione risulta evidente che il coefficiente di temperatura della corrente risulta dalla differenza dei coefficenti di temperatura della tensione ai capi del diodo (negativo come visto in precedenza) e della resistenza (coefficiente di temperatura positivo). Il risultato totale e' che  $\alpha_I$  risultera' negativo.

Per ottenere l'ugualianza delle tensioni ai punti A e B viene utilizzato, come nel circuito generatore di IPTAT, uno specchio di corrente in configurazione Wilson. Si ottiene quindi il circuito di fig.4.2.3

Figura 4.2.3: Schema finale per la generazione della corrente ICTAT

Il circuito in figura e' stato simulato al fine di verificarne il

corretto funzinamento; il risultato e' mostrato in fig.4.2.4 in cui e' possibile vedere la variazione della corrente in funzione della temperatura che, in accordo a quanto detto fin qui, risulta avere un coefficiente di temperatura negativo.

Figura 4.2.4: Andamento in temperatura della corrente ICTAT ottenuto nelle simulazioni.

Successivamente e' stata effettuata una caratterizzazione del circuito andando ad analizzare come varia la corrente in funzione della temperatura e al variare della resistenza R.

In particolare sono state effettuate simulazioni con valori di resistenza R compresi fra  $1K\Omega$  e  $20K\Omega$ . I risultati sono riportati nelle fig.4.2.5 e fig.4.2.6.

#### Slope vs Resistence value

Resistence [Ohm]

Figura 4.2.5: Andamento della pendenza della corrente ICTAT in funzione della resistenza R

Figura 4.2.6: Andamento del coefficiente di temperatura al variare della resistenza R

Si noti come, al fine di ottenere una maggiore invarianza della

derivata e del coefficiente di temperatura della corrente ICTAT, convenga usare valori di resistenza maggiori di 6 K $\Omega$ .

#### 4.3 Bandgap Voltage Reference

Il bandgap voltage reference e' un circuito che genera una tensione di riferimento  $V_{\text{REF}}$  stabile in temperatura.

Al fine di ottenere tale riferimento vengono sfruttate le caratteristiche in temperatura dell'energy gap del silicio (che va a influenzare la tensione di polarizzazione diretta di un diodo) e della tensione termica.

Vediamo ora come ottenere tale circuito. Dal capitolo 4.2 sappiamo che la tensione ai capi di un diodo polarizzato con una corrente costante risulta avere un coefficiente di temperatura negativo, mentre la tensione termica risulta avere un coefficiente di temperatura positivo.

Dalla somma di queste due tensioni e' possibile ottenere una tensione stabile in temperatura. Il funzionamento del circuito e' mostrato in fig.4.3.1 e il relativo schema circuitale in fig.4.3.2.

Figura 4.3.1: Schema di principio di un Band Gap voltage reference

Figura 4.3.2: Schematico del circuito Bandgap voltage reference

Tale schema risulta essere composto da un generatore di corrente PTAT, gia' analizzato precedentemente nel capitolo 4.1, ed un ulteriore ramo formato dalla serie dei transistori MP1,MP2, dalla resistenza R2 e dal diodo D3. I transistori MP1 ed MP2 specchiano la corrente I, che circola nel generatore di corrente IPTAT, facendo si che anche sulla resistenza R2 e sul diodo D3 circoli tale corrente.

Tramite la (4.1.8) calcoliamo il valore di corrente che circola in R2 e di conseguenza la tensione ai sui capi, esprimibile come:

$$V_{R2} = V_t \cdot \frac{\ln(m)}{RI} \cdot R2 \tag{4.3.1}$$

Supponiamo ora che la resistenza R2 sia multipla di R1 quindi

esprimibile come:

$$R2 = L \cdot R1 \tag{4.3.2}$$

la tensione V<sub>R2</sub> puo essere scritta attraverso la seguente formula:

$$V_{R2} = V_t \cdot L \cdot \ln(m) \tag{4.3.3}$$

La tensione  $V_{ref}$  e' data dalla somma della tensione ai capi di R2,  $V_{R2}$ , e la tensione ai capi del diodo D3 pari a  $V_{D3}$ :

$$V_{ref} = V_{R2} + V_{D3} = V_t \cdot L \cdot \ln(m) + V_{D3}$$

(4.3.4).

Derivando la (4.3.4) rispetto alla temperatura otteniamo che:

$$\frac{\partial V_{ref}}{\partial T} = L \cdot \ln(m) \cdot \frac{\partial V_{t}}{\partial T} + \frac{\partial V_{D3}}{\partial T}$$

(4.3.5)

Il circuito implementa quanto mostrato nello schema di principio in fig.4.3.1 cioe' genera una tensione Vref data dalla somma di due tensioni con coefficiente di temperatura complementare.

E' quindi possibile ottenere la stabilita' in temperatura di tale tensione imponendo:

$$L \cdot \ln(m) \cdot \frac{\partial V_t}{\partial T} = -\frac{\partial V_{D3}}{\partial T}$$

(4.3.6)

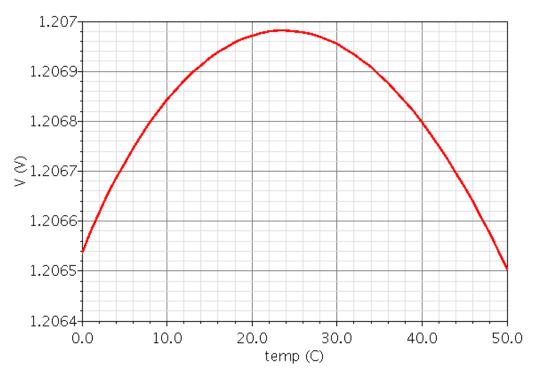

e andando a modificare i parametri L ed m al fine di ottenere tale ugualiznza. Il circuito e' stato simulato scegliendo una resistenza R1 pari a 6.2 K $\Omega$ , una resistenza R2 pari a 44.7 K $\Omega$  e un fattore m pari a 16. I risultati delle simulazioni sono riportati in fig.4.3.3

Figura 4.3.3: Risultato delle simulazioni del circuito Bandgap Voltage Reference

L'andamento ottenuto rappresenta una tensione  $V_{\rm ref}$  in cui il coefficiente di temperatura del primo ordine risulta nullo. L'andamento parabolico e' dovuto alla presenza di effetti del secondo ordine che, tuttavia, non comportano grandi variazioni in temperatura della tensione.

Il circuito e' stato progettato dimensionando i componenti in modo tale da avere il massimo della curva di fig.4.3.3 a temperatura ambiente, di modo che nell'intorno di tale valore le variazioni siano le piu' piccole possibili.

#### Capitolo 5

# Implementazione CMOS delle architetture proposte

Nel capitolo vengono descritti i dettagli implementativi delle due architetture proposte nel capitolo 3.

In entrambi i casi si analizza la costruzione del circuito con particolare attenzione al dimensionamento dei componenti per ottenere i risultati voluti. I due voltage reference si basano sui circuiti precedentemente illustrati nel capitolo 4.

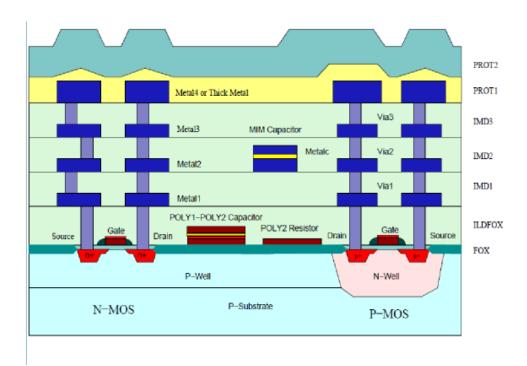

I due circuiti sono stati progettati per la realizzazione su silicio con tecnologia CMOS  $0.35~\mu m$ .

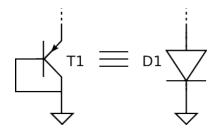

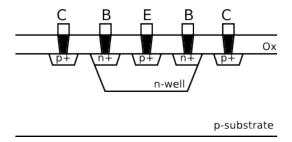

Tale tecnologia non prevede come componente il diodo. Per ottenerlo nei circuiti descritti nel capitolo 4 viene utilizzato un transistor PNP parassita connesso in cofigurazione diodo, qui riportato in fig.5.1.

Figura 5.1: transistor PNP in configurazione diodo

Di seguito in fig. 5.2 viene mstrato una sezione trasversale del transistor PNP parassita verticale utilizzabile in tecnologia CMOS  $0.35~\mu m$ . Tale soluzione introduce solo il vincolo che il collettore del transistor PNP, e quindi il catodo del diodo D1, sia forzatamente connesso alla tensione di substrato.

Questo però non influenza il funzionamento dei ciscuiti fino ad ora descritti.

Figura 5.2: PNP parassita in tecnologia CMOS 0.35 µm

### 5.1 Voltage Reference current generator based

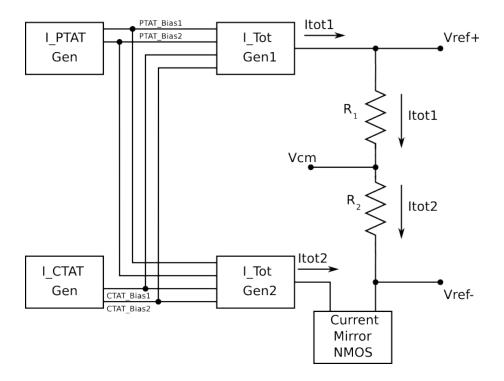

Come spiegato nel capitolo 3, il circuito si basa sulla compensazione delle caratteristiche in temperatura di una corrente e di un convertitore I/V al fine di generare una tensione costante in temperatura. Come convertitore tensione corrente e' stato scelto un resistore. Il circuito di riferimento viene quindi mostrato in fig. 5.1.1

Figura 5.1.1 Schema del circuito spiegato in fig.

L'obiettivo e' quello di imporre sui due resitori, scelti di uguale valore, due correnti identiche in modo da ottenere due cadute di tensione identiche, di valore Vref ai capi di entrambi.

Se la tensione del nodo A viene fissata a Vcm si ottiene esattamente:

$$V_{ref+} = V_{cm} + V_{ref}$$

(5.1.1)

$$V_{ref} = V_{cm} - V_{ref}$$

(5.1.2)

Supponendo che la Vcm sia indipendente dalla temperatura, visto che e' fornita da un generatore, cio' che ci preme capire ora e' la caratteristica in temperatura della Vref.

Andiamo quindi a vedere quali siano le caratteristiche della tensione ai capi di un resistore noto l'andamento in temperatura della corrente che circola in esso e il suo valore di resistenza.

Come gia' detto precedentemente gli andamenti in temperatura della corrente e della resistenza vengono espressi al primo ordine da:

$$I(T) = I_0 \cdot (1 + \alpha_I \cdot (T - T_0)) \tag{5.1.3}$$

$$R(T) = R_0 \cdot (1 + \alpha_R \cdot (T - T_0)) \tag{5.1.4}$$

Sapendo questo calcoliamo ora la tensione ai capi del resistore utilizzando la legge di Ohm:

$$V(T) = I(T) \cdot R(T) \tag{5.1.5}$$

sostituendo la (5.1.3) e la (5.1.4) che esplicitano I(T) e R(T) otterremo che:

$$V(T) = R_0 \cdot I_0 \cdot (1 + (\alpha_R + \alpha_I) \cdot (T - T_0) + \alpha_R \cdot \alpha_I \cdot (T - T_0)^2)$$

(5.1.6)

Supponendo trascurabile il termine del secondo ordine otteniamo il risultato finale:

$$V(T) = R_0 \cdot I_0 \cdot (1 + (\alpha_R + \alpha_I) \cdot (T - T_0))$$

(5.1.7)

con:

$$V_0 = R_0 \cdot I_0 \tag{5.1.8}$$

$$\alpha_V = \frac{1}{V_0} \cdot \frac{\partial V}{\partial T} = (\alpha_R + \alpha_I)$$

(5.1.9)

E' quindi possibile far si che il coefficente di temperatura della tensione ai capi di un resistere sia nullo andando a far si che i coefficenti di temperatura della corrente e della resistenza si annullino.

Sapendo che la resistenza aumenta con la temperatura, e quindi presenta un coefficente di temperatura positivo, l'obiettivo e' quello di generare una corrente con coefficente di temperatura negativo.

Per fare cio' vengono sfruttati i circuiti mostrati nei capitoli 3.1 e 3.2 .L'idea e' quella di sommare una corrente PTAT e una CTAT al fine di ottenere il coefficente di temperatura voluto come mostrato in fig.5.1.2. Questa scelta garantisce una maggiore stabilità del coefficiente di della corrente I<sub>tot</sub>.

Figura 5.1.2 Schema di principio del generatore di corrente

Abbiamo visto nei capitoli 3.1 e 3.2 che nei circuiti generatori di corrente PTAT e CTAT se viene scelta un valore di resistenza alto presentano coefficenti di temperatura costanti.

Nel nostro caso e' stato scelto un valore di 18  $K\Omega$  nel circuito che genera la corrente CTAT e 6,2  $K\Omega$  nel circuito che genera la corrente PTAT, con un fattore m=16.

Considerando quindi fissati i due coefficenti di temperatura andiamo a vedere come e' possibile ottenere una  $I_{tot}$  con coefficente di temperatura voluto.

La corrente  $I_{tot}$ , data dalla somma di due correnti che variano in temperatura, sara' anch'essa variabile in temperatura. Cerchiamo di esprimere Itot come:

$$I_{tot}(T) = I_{tot0} \cdot (1 + \alpha_{Itot} \cdot (T - T_0)) \tag{5.1.10}$$

con  $\alpha_{Itot}$  coefficente di temperatura della corrente totale definito come:

$$\alpha_{Itot} = \frac{1}{I_{tot0}} \cdot \frac{\partial I}{\partial T}_{T=T_0}$$

(5.1.11)

Consideriamo quindi che:

$$I_{tot}(T) = I_{PTAT}(T) + I_{CTAT}(T)$$

(5.1.12)

e considerando le approssimazioni al primo ordine delle due correnti PTAT e CTAT possiamo scrivere la (5.1.12) come:

$$I_{tot}(T) = (I_{PTAT0} + I_{CTAT0}) \cdot (\frac{I_{PTAT0}}{I_{PTAT0} + I_{CTAT0}} \cdot \alpha_{IPTAT} + \frac{I_{CTAT0}}{I_{PTAT0} + I_{CTAT0}} \cdot \alpha_{ICTAT}) \cdot (T - T_0) \quad (5.1.13)$$

Fissati i due coefficeenti di temperatura e' quindi possibile ottenere il coefficente di temperatura voluto per la Itot andando a fare una somma pesata delle due correnti.

Si e' quindi deciso di fissare il valore di corrente PTAT che puo essere calcolato sfruttando la (4.1.8) e, inserendo i parametri precedentemente detti, si ottiene  $11,56~\mu A$ .

A questo punto si e' imposto:

$$-\alpha_{R} = \frac{I_{PTAT0}}{I_{PTAT0} + I_{CTAT0}} \cdot \alpha_{IPTAT} + \frac{I_{CTAT0}}{I_{PTAT0} + I_{CTAT0}} \cdot \alpha_{ICTAT}$$

(5.1.13)

e si e' andati ad esplicitare il valore di ICTATO ottenendo:

$$I_{CTAT0} = \frac{I_{PTAT0} \cdot (\alpha_R + \alpha_{PTAT})}{(\alpha_R + \alpha_{CTAT})} = 61,89 \,\mu A$$

(5.1.14)

Vediamo ora come ottenere tale risultato circuitalmente. In fig.5.1.3 viene mostrato lo schema utilizzato.

Figura 5.1.3: Schematico del generatore di corrente ITot

Come si puo vedere dallo schematico I transistor MP9 e MP10 specchiano la corrente che circola nel circuito I\_PTAT\_Gen; i transistor MP11 e MP12 specchiano invece la corrente che circola nel circuito I\_CTAT\_Gen. Le due correnti si sommano poi nel nodo A generando così la Itot.

Al fine di ottenere il giusto coefficente di temperatura per la Itot, come spiegato precedentemente, la ICTAT e la IPTAT devono essere in un preciso rapporto fra di loro.

I transistor MP9 e MP10 hanno lo stesso fattore di forma dei

transistor MP1, MP2, MP3, MP4 quindi replicano fedelmente la corrente che circola nel circuito I PTAT Gen pari a 11,56 µA.

La corrente ICTAT, come espresso dalla (5.1.14), deve quindi valere  $61.89~\mu A$ .

La corrente che circola nel circuito I\_CTAT\_Gen, calcolata tramite la (4.2.13), risulta essere di  $39.97~\mu A$ . I transistor MP11 e MP12 devono specchiare la corrente che circola nel circuito I\_CTAT\_Gen e moltiplicarla per un fattore n calcolabile come:

$$n = \frac{I_{CTAT \ VOLUTA}}{I_{CTAT}} \simeq \frac{9}{5} \tag{5.1.14}$$

Per fare cio' occorre quindi che il fattore di forma dei transistor MP11 e MP12 che specchiano la corrente ICTAT sia n volte il fattore di forma dei transistor MP5, MP6, MP7, MP8.

Il passo successivo e' quello di ottenere una replica di tale corrente in modo da avere due correnti che scorrano nel verso opportuno. La soluzione proposta viene mostrata in fig.5.1.4

Figura 5.1.4: Schma finale per la generazione delle tensioni di riferimento

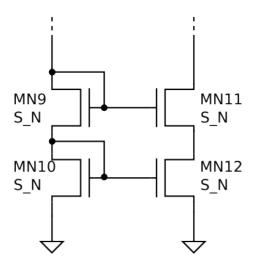

Come si puo notare il circuito e' formato da due I\_Tot\_Gen; il primo impone la corrente sul resistore R1, la corrente del secondo viene invece specchiata, con uno specchio di corrente composto da transistori NMOS così da fissare anche la corrente sul resistore R2 nel verso desiderato. Lo specchio di corrente utilizzato viene mostrato in fig 5.1.5.

Figura 5.1.5: Specchio di corrente utilizzato nel circuito

Per ottenere due tensioni simmetriche i resistori R1e R2 devono essere di uguale valore. Le due tensioni Vref+ e Vref-devono poi essere bufferizzate inserendo un operazionale in configuratore inseguitore mostrato in fig 5.1.6

Figura 5.1.6: Operazionale in configurazione inseguitore di tensione

Un operazionale in tale configurazione replica la tensione di ingresso in uscita (a meno della tensione di offset dell'operazionale) disaccoppiando pero' il circuito che si trova a monte dal circuito che si trova a valle. Il buffer utilizzato, già presente come componente di libreria del simulatore, non influenza, in modo significativo, le caratteristiche in temperatura della tensione generata. In futuro tale baffer potrà essere sostituito da un op-amp, progettato opportunamente, con un basso offset e una più elevata stabilità in temperatura.

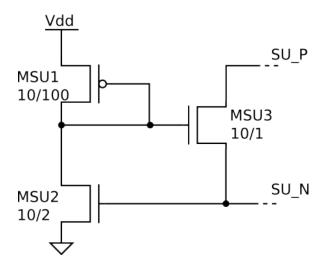

Come ultima considerazione va detto che i circuiti I\_PTAT\_Gen e I\_CTAT\_Gen sono reti autopolarizzate.

Tale tipo di rete ha due punti di lavoro stabili; uno in cui la corrente e' nulla, cioe' la rete rimane spenta e uno in cui la corrente che circola e' diversa da zero e in particolare valgono tutte le trattazioni dei capitoli 3.1 e 3.2.

Per far fronte a questo problema e' necessario inserire una rete di Start Up che permette ai due circuiti, all'accensione, di posizionarsi nel corretto punto di lavoro. Tale rete viene mostrata in fig. 5.1.7

Figura 5.1.6: Rete di Start Up. Il circuito neccessita una rete di questo tipo per ogni rete autopolarizzata.

Il funzionamento viene spiegato con riferimento anche alla fig. 5.1.3 e considerando il solo circuito I\_PTAT\_Gen. Naturalmente

il tutto rimane valido anche per la rete I\_CTAT\_Gen.

Il segnale SU\_P deve essere collegato al gate dei transistor MP\_2 e MP\_4, mentre il segnale SU\_N deve essere collegato al gate dei transistor MN 1,MN 3.

All'accensione il gate del transistor MSU1 si trova a un potenziale compreso fra VDD e VDD-V<sub>thp</sub> (tensione di soglia dei transistor PMOS); cio' fa si che il transistor MSU3 sia acceso.

Tale transistor ,che funziona come uno switch NMOS, collega i gate dei transistor MP\_2 e MP\_4 con i gate dei transistor MN\_1 e MN 3.

I gate dei transistor P si trovano pero' a un potenziale compreso fra VDD e  $VDD-V_{thp}$  quindi la connessione dei loro gate con quelli dei transistor NMOS provoca l'accensione di questi ultimi.

L'accensione della rete NMOS provoca l'abbassamento del potenziale dei gate dei transistor P accendendoli. A questo punto SU\_P e SU\_N si trovano allo stesso potenziale e quindi sul transistor MSU3 non circola piu corrente.

La rete di Start Up risulta quindi esclusa dal circuito I PTAT Gen una volta che questa ha raggiunto il punto di lavoro

#### 5.2 Voltage Reference Bandgap based

Il circuito si basa sul band gap voltage reference mostrato nel capitolo 4.3 che, come gia detto, e' in grado di generare una tensione di riferimento stabile in temperatura.

Il circuito di partenza e' quindi quello mostrato in fig. 4.3.2 in cui R1 ha un valore di 6,2 K $\Omega$  il fattore m e' uguale a 16 e R2 ha un valore di 44,7 K $\Omega$ .

La tensione generata dal band gap, calcolabile attraverso la (4.3.4) risulta essere di 1.207 mV. L'obiettivo inizialmente e'quello di ottenere una tensione Vref di 450 mV che poi andra' sommata e

sottratta alla Vcm (vedi fig.3.1).

Per fare cio' la tensione fornita dal band gap viene bufferizzata con un operazionale in configurazione inseguitore di tensione e successivamente scalata attraverso un partitore di tensione come mostrato in fig. 5.2.1.

Figura 5.2.1 Band Gap Voltage reference seguito dal partitore di tensione

Il buffer copia la tensione  $V_{\text{bg}}$  in ingresso al partitore di tensione, senza andare a influenzare il funzionamento del band gap. Le resistenze devono essere dimensionate al fine di ottenere la  $V_{\text{ref}}$  voluta.

Per fare cio' va invertita la relazione ingresso uscita del partitore di tensione. Noto che:

$$V_{ref} = \frac{R4}{R3 + R4} \cdot V_{bg} \tag{5.2.1}$$

conoscendo il valore di tensione  $V_{ref}$  e fissato il valore della resistenza R4 a 10 K $\Omega$  e' possibile calcolare il valore di R3 invertendo la (5.2.1). Si ottiene:

$$R3 = \frac{V_{bg} - V_{ref}}{V_{ref}} \cdot R4 = 16822 \, K\Omega \tag{5.2.2}$$

Tale tensione deve essere a sua volta bufferizzata con un'altro inseguitore di tensione al fine da non perturbare il partitore resistivo.

Da notare che  $V_{\text{ref}}$  ha le stesse caratteristiche in temperatura di Vbg visto che esplicitando la dipendenza in temperatura delle resistenze si ottiene:

$$V_{ref} = \frac{R4_0 \cdot (1 + \alpha_R \cdot (T - T_0))}{R4_0 \cdot (1 + \alpha_R \cdot (T - T_0)) + R3_0 \cdot (1 + \alpha_R \cdot (T - T_0))} \cdot V_{bg}$$

(5.2.3)

che raccogliendo a fattore comune al denominatore diventa:

$$V_{ref} = \frac{R4_0 \cdot (1 + \alpha_R \cdot (T - T_0))}{(R4_0 + R3_0) \cdot (1 + \alpha_R \cdot (T - T_0))} \cdot V_{bg}$$

(5.2.4)

dove si vede chiaramente che la dipendenza in temperatura puo essere semplificata.

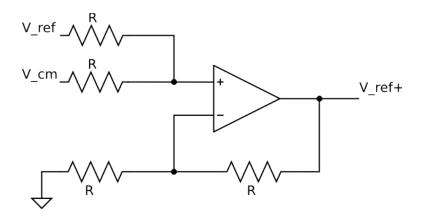

Una volta ottenuta la tensione di riferimento voluta, come mostrato in figura 3.1, essa deve essere sommata e sottratta alla  $V_{\rm cm}$ .

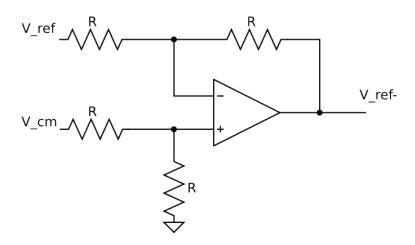

Per ottenere cio viene utilizzato un circuito sommatore e un circuito differenziale simmetrico. Il circuito sommatore viene mostrato in fig. 5.2.2

Figura 5.2.2: Circuito sommatore realizzato con op-amp

Considerando l'operazionale ideale possiamo dire che la tensione al morsetto invertente  $(V_{\cdot})$  e quella la morsetto non invertente  $(V_{+})$  sono uguali e che le correnti assorbite dai due morsetti siano nulle.

Detto cio' possiamo ricavarci la relazione di inigresso/uscita del circuito. Applicando il principio di sovrapposizione degli effettetti possiamo calcolare la tensione V<sub>+</sub> ottenendo che:

$$V_{+} = \frac{V_{ref}}{2} + \frac{V_{cm}}{2}$$

(5.2.5) .

La tensione al morsetto invertente sara' invece espressa da:

$$V_{-} = \frac{V_{ref +}}{2} \tag{5.2.6}$$

Ugualiando queste due tensioni si ricava che:

$$V_{ref} = V_{ref} + V_{cm}$$

(5.2.7).

Come si puo notare dalla (5.2.7) in uscita dall'operazionale avremo quindi la somma delle tensioni Vref e della Vcm.

Vediamo ora come viene generata la Vref-. Come detto in

precedenza viene utilizzato un circuito differenziale simmetrico mostrato in fig.5.2.3

Figura 5.2.3: Circuito differenziale simmetrico realizzato con op-amp

Come fatto in precedenza calcoliamo la relazione ingresso uscita supponendo che l'operazionale sia ideale. Applicando il prncipio di sovrapposizione degli effetti possiamo dire che:

$$V_{ref} = V_{ref}^{1} + V_{ref}^{2}$$

(5.2.8)

cioe' la tensione di uscita viene espressa dalla somma delle tensioni di uscita ottenute con uno solo dei generatori attivo.

Tenendo attiva la sola  $V_{\text{ref}}$  e cortocircuitando  $V_{\text{cm}}$  si ottiene un operazionale in configurazione amplificatore invertente, la cui relazione ingresso uscita risulta essere espressa da:

$$V_{ref}^{1} = -\frac{R}{R} \cdot V_{ref} = -V_{ref}$$

(5.2.9)

Viceversa tenendo attiva la  $V_{cm}$  e cortocircuitando la  $V_{ref}$  si ottiene un operazionale in configurazione non invertente la cui relazione ingresso uscita e' espressa da:

$$V_{ref-}^2 = (1 + \frac{R}{R}) \cdot \frac{R}{R+R} V_{cm} = V_{cm}$$

(5.2.10)

La  $V_{\text{ref-}}$  risultara' quindi espressa da:

$$V_{ref} = V_{cm} - V_{ref}$$

(5.2.11)

Si e' quindi ottenuta una  $V_{\text{ref-}}$ , concordatamente con quanto cercato, data dalla differenza fra la  $V_{\text{cm}}$  e la  $V_{\text{ref}}$ . Lo schema finale del circuito viene mostrato in fig.5.2.4

Figura 5.2.4: Schema complessivo del riferimento in tensione ottenuto partendo dal Bangap

#### Capitolo6

#### Simulazioni

I circuiti proposti sono stati simulati e i risultati delle simulazioni sono stati confrontati al fine di scegliere quale circuito dovesse essere successivamente realizzato su silicio.

I paramatri valutati sono stati descritti precedentemente nel capitolo 3.

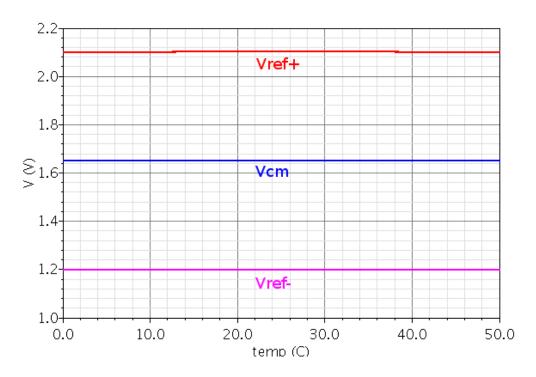

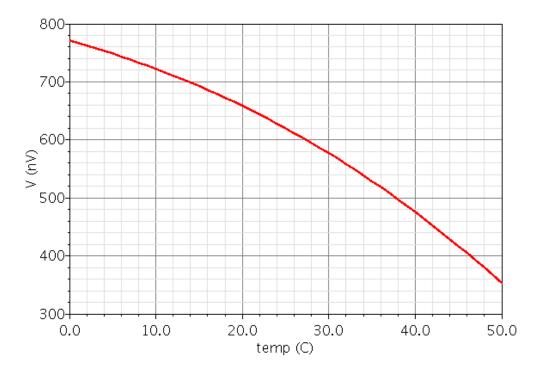

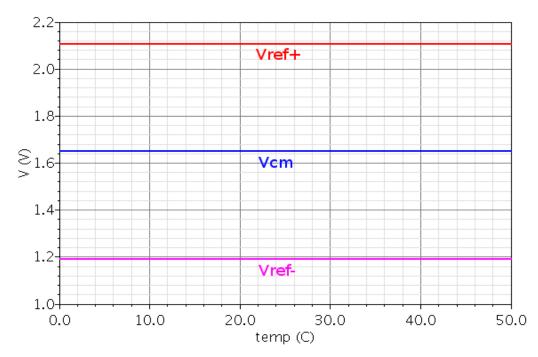

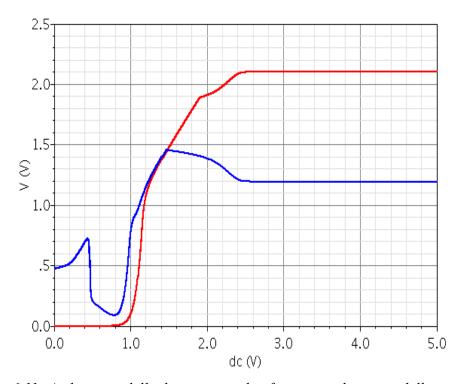

La prima parte di simulazioni riguarda la funzionalita dei circuiti. Di seguito vengono riportate le simulazioni ottenute con il circuito descritto nel capitolo 5.1. Il primo grafico (fig.6.1) rappresenta le due tensioni.

Figura: 6.1: Tensioni ottenute simulando il circuito con generatori di corrente

La simulazione e' stata effettuata impostando la tensione di alimentazione di 3.3V e una  $V_{\rm cm}$  di 1.65V. L'andamento risulta uguale a quello mostrato in fig.1.1

Di seguito (fig.6.2) si riportano invece i grafici contenenti l'andamento in temperatura dellle singole tensioni  $V_{\text{ref+}}$  e  $V_{\text{ref-}}$ .

Figura 6.2: Grafici rappresentanti la tensione Vref+ e Vref-

Dai grafici si nota come le ddue tensioni mantengano la loro simmetria anche durante le variazioni di temperatura e come tale variazione sia di 400 ppm nel range di temperatura da 10 a 40°C.

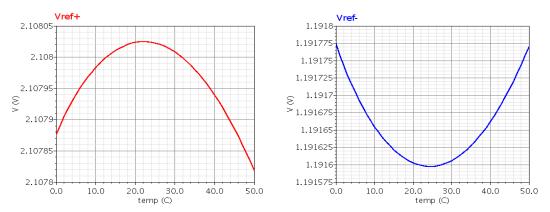

Successuvamente si riporta (fig.6.3) il grafico rappresentante la dissimmetria delle due tensioni, valutata come spiegato nella (3.2).

Figura 6.3: Grafico rappresentante la dissimmetria delle due tensioni

Il livello di dissimmetria delle due tensioni risulta avere valori massimi di poche centinaia di nV.

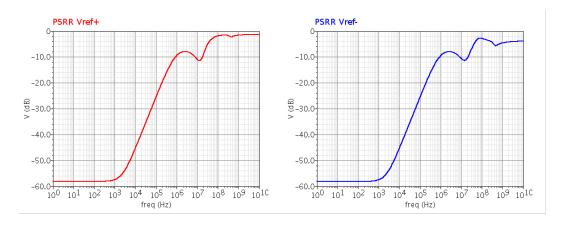

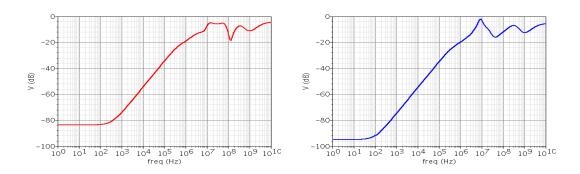

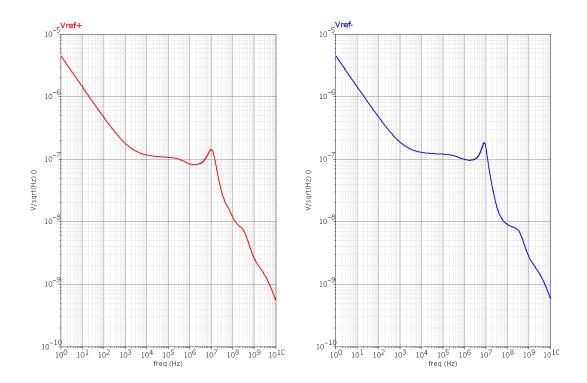

Il successivo parametro valutato e' stato il PSRR il cui grafico viene riportato in fig.6.4

Figura 6.4: Grafico del PSRR delle due tensioni di riferimento

Tali graici mostrano come il PSRR abbia un valore minimo alle basse frequenze di -59 dB e come poi degradi superati i 10 Khz. Nel capitolo 8 verrà mostrata una soluzione in grado dimigliorare l'andamento in frequenza del PSRR e diminuire il valore minimo raggiunto.

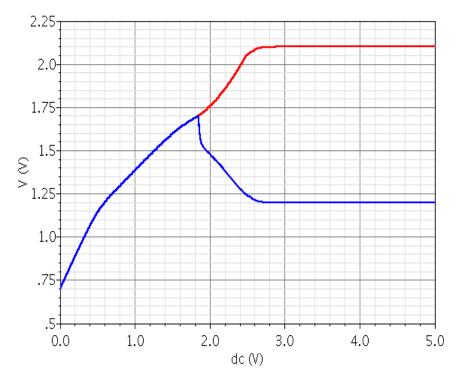

Successivamente e' stata fatta variare la tensione di alimentazione a fine di determinare il range di funzionamento corretto del circuito.

Le simulazioni sono state effettuate mantenendo costante la tensione di riferimento Vcm e facendo variare la tensione di alimentazione.

Siccome il circuito puo' funzionare sia in sistemi ad alimentazione singola che ad alimentazione duale, la tensione sull'asse delle ascisse e' da considerare come differenza di tensione fra la tensione di subtrato  $V_{ss}$  e la tensione  $V_{DD}$ . In fig.6.5 se ne riportano i risultati:

Figura 6.5: Andamento delle tensioni di riferimento al variare della tensione di alimentazione

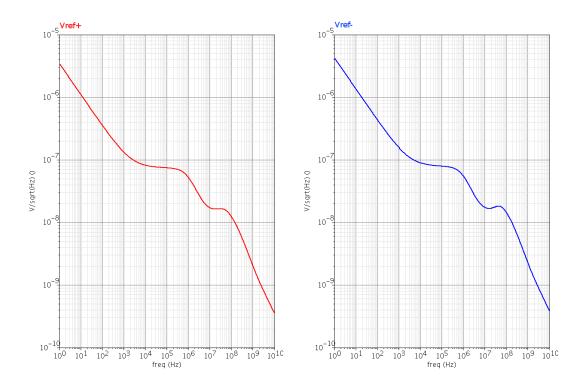

Come si puo notare il circuito iniizia a funzionare correttamente da una tensione di circa 2.7V. L'ultima simulazione e' stata effettuata per valutare il rumore generato dal riferimento in tensione. Cio' risulta importante visto che il riferimento deve lavorare con circuiteria analogica ad alta precisione e il rumore da lui generato risulta essere in ingresso a tutti gli altri stadi. In fig.6.6 se ne riportano i risultati.

Figura 6.6: Grafico che mostra lo spettro in tensione del rumore delle due tensioni generate

Il circuito presenta un rumere a 10 Khz di 80 nV/ $\sqrt{\text{Hz}}$  e una corner frequency di 1 Khz.

Andiamo ora a valutare il circuito che genera le tensioni di riferimento partendo dal bandgap.

Il primo grafico che viene, mostrato in fig.6.7, sono le due tensioni rispetto alla  $V_{\text{cm}}$ :

Figura 6.7: Grafico delle tensioni ottenute con il circuito basato su Band Gap

La simulazione e' stata effettuata, come in precedenza, con tensione di alimentazione 3.3V e Vcm 1.65V. Il gra grafico, come per il circuito precedente, risulta essere uguale a quello mostrato in fig,1.1.

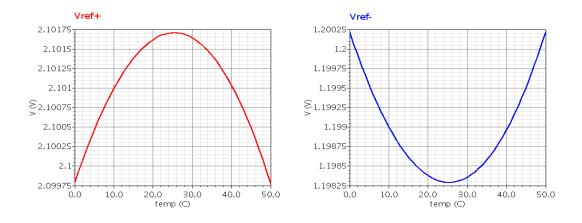

Di seguito si riportano anche gli andamenti in temperatura delle due singole tensioni (fig.6.8).

Figura 6.8: Grafico dell'andamento in temperatura delle due tensioni Vref+ e Vrefgenerate a partire della tensione del bandgap

Le due tensioni risultano avere due andamenti in temperatura simmetrici e presentato una variazione di 438 ppm nel range di temperatura da 10 a 35°C

Successivamente e' stata graficata la dissimmetria delle due tensioni che viene riportata in fig.6.9:

Figura 6.9: Grafico della dissimmetria fra le due tensioni Vref+ e Vref-

Come si può notare la dissimmetria risulta essere di qualche centinaia di  $\mu V$ , quindi considerevolmente maggiore aquanto mostrato per il circuito precedente.

In fig.6.10 viene mostrato l'andamento del PSRR:

Figura 6.10: Grafico del PSRR delle due tensioni Vref+ e Vref- ottenute con il bandgap

Il PSRR risulta avere valori massimimi di -94 dB ma, analogamente a prima, degrada alle alte frequenze.

Il grafico successivo (fig.6.11) presenta invece il risultato della simulazione effettuata al variare della tensione di alimentazione realizzata con la stessa metodologia dei grafici mostrati in fig.6.5.

Figura 6.11: Andamento delle due tensioni di riferimento al variare della tensione di alimentazione nel circuito implementato tramite bandgap

Il circuito inizia a funzionare correttamente a partire da una tensione di circa 2.6V.

Analogamente a prima come ultimo risultato vengono mostrati i risultati ottenuti effettuando le simulazioni di rumore (fig.6.12).

Figura 6.12: Grafico che mostra lo spettro in tensione del rumore delle due tensioni generate

Il circuito risulta avere un rumore di poco superiore ai 100  $nV/\sqrt{\text{Hz}}$  a 10 Khz e una corner frequency di 1 Khz.

Riassumiamo ora i dati fino a qui ottenuti in una tabella al fine di facilitarne il confronto:

|                           | V ref. Correnti |        |          | V ref. Bandgap |        |        |  |

|---------------------------|-----------------|--------|----------|----------------|--------|--------|--|

|                           | min             | max    | typ      | min            | max    | typ    |  |

| PWR [mW]                  | -               | -      | 14,53    | -              | -      | 27,41  |  |

| Δ Vref                    | 353 nv          | 771 nv | 599.5 nV | 350 µV         | 410 µV | 382 µV |  |

| PSRR [dB]                 | -59             | -1,5   | -        | -94            | -2     | -      |  |

| Supply [V]                | 2,7             | 5,5    | 3,3      | 2,6            | 5,5    | 3,3    |  |

| α [ppm]                   | -               | -      | 444      | -              | -      | 438    |  |

| Noise @ 10KHz<br>[nV/√Hz] | -               | -      | 80       | -              | -      | 100    |  |

| Corner<br>Freq[Khz]       | -               | -      | 1        | -              | -      | 1      |  |

Tabella 1: Tabella comparativa dei dati ottenuti dalle simulazioni

Come si puo notare il circuito con generatori di corrente presenta una potenza dissipata inferiore rispetto al circuito con bandgap e una maggiore simmetria delle due tensioni di riferimento.

Per quanto riguarda il PSRR il circuito con bandgap risulta essere migliore; da notare pero', facendo riferimento alle fig.6.4 e fig.6.8, che nel circuito con bandgap il valore minimo viene raggiunto per frequenze fino ai 100Hz e successivamente il valore del PSRR dei due circuiti risultano essere simili.

Inoltre l'andamento in frequenza dei PSRR delle due tensioni  $V_{\text{ref+}}$  e  $V_{\text{ref-}}$  risulta essere apprezzabilmente differente; cio' implica che, in risposta a un disturbo sull'alimentazione, le due tensioni aumentano la loro dissimmetria.

Come ultima considerazione, è da notare che l'architettura con il bandgap risulta essere piu rumorosa e inoltre e' possibile diminuire ulteriormente il rumore generato dal primo circuito andando a inserire un buffer a piu' basso rumore visto che risulta essere il componente che lo influenza di piu'.

Successivamente e' stato verificato come incertezze nel

processo di realizzazione su silicio influiscano sulle due architetture riportando i dati in tabella 2.

|                 | Processo       |          |              |          | Mismatch       |         |              |          |

|-----------------|----------------|----------|--------------|----------|----------------|---------|--------------|----------|

|                 | V ref Correnti |          | V ref Bangap |          | V ref Correnti |         | V ref Bangap |          |

|                 | Vref+          | Vref-    | Vref+        | Vref-    | Vref+          | Vref-   | Vref+        | Vref-    |

| Valor medio [V] | 2,101545       | 1,198324 | 2,100015     | 1,199976 | 2,10272        | 1,19696 | 2,10092      | 1,198987 |

| std dev [mV]    | 5,21           | 5,3      | 4,93         | 5,11     | 3,69           | 4,07    | 3,87         | 3,86     |

| std dev %       | 1,15           | 1,17     | 1,09         | 1,13     | 0,82           | 0,91    | 0,86         | 0,86     |

Tabella 2: Tabella riassuntiva dei dati ottenuti attraverso le simulazioni montecarlo

Come si puo notare i valori di tensione presentano sensibilita' simili al processo e ai mismatch.

Considerando la tabella 1 e la tabella 2, alla luce dei dati ottenuti, e' stato scelto di implementare su silicio il circuito descritto nel capitolo 5.1.

## Capitolo 7

## Implementazione su silicio

La realizzazione su silicio del circuito e' stata effettuata per la tecnologia CMOS  $0.35~\mu m$  che prevede una sezione del wafer mostrata in fig.6.1

Figura 7.1: Sezione trasversale del wafer di silicio nella tecnologia costruttiva utilizzata

Tale tecnologia prevede 4 livelli di metal per le interconnessioni e oltre ai transistor mos, e i transistor PNP parassiti i componenti di nostro interesse sono i resistori. Vi son diverse possibili implementazioni di un resistore in tecnologia CMOS ma, considerando che in questo caso il resistore e il suo comportamento in temperatura devono essere lineari si prenderanno in considerazione i resitori di tipo POLY1, i resistori di tipo POLY2, e i resistori di tipo POLYH che differiscono fra loro per I materiali di realizzazione.

In tabella 3 vengono riportate le caratteristiche fondamentali di questo tipo di resistori.

|        |                  | MIN | TYP   | MAX | UNITS   |

|--------|------------------|-----|-------|-----|---------|

| RPOLY1 | RESISTENCE VALUE | 5   | 8     | 11  | Ω/□     |

|        | TEMP COEFFICIENT |     | 0,9   |     | 10^-3/K |

| RPOLY2 | RESISTENCE VALUE | 40  | 50    | 60  | Ω/□     |

|        | TEMP COEFFICIENT |     | 0,59  |     | 10^-3/K |

| RPOLYH | RESISTENCE VALUE | 1   | 1,2   | 1,4 | ΚΩ/□    |

|        | TEMP COEFFICIENT |     | -0,75 |     | 10^-3/K |

Tabella 3: Caratteristiche fondamentali dei tre tipi di resistori disponibili in tecnologia CMOS 0.35um

Come si puo vedere dalla tabella i tre dipi di materiali prensentano caratteristiche diverse sia di resistenza per quadro che di coefficiente di temperatura. Per via del materiale utilizzato I resistori RPOLYH hanno un coefficente di temperatura negativo. Ciò non influenza però la trattazione effettuata nel capitolo 4.

Nel nostro caso la decisione e' stata presa soprattuto tenendo conto di vincoli spaziali e di precisione della resistenza ottenuta. Si e' deciso di realizzare le resistenze RPTAT e RCTAT in POLYH in modo da diminuirne l'occupazione spaziale e le resistenze utilizzate come convertitori I/V sono invece state realizzate in POLY1 per cercare di ottenere una precisione migliore.

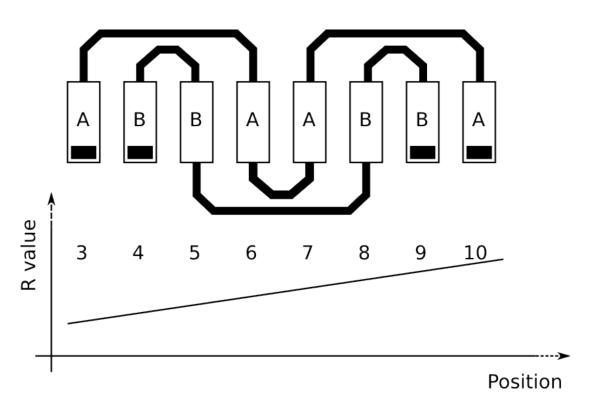

Altro fattore fondamentale nel disegno del layout di questo tipo di schematico e' il matching.

Per garantire simmetria delle due tensioni generate infatti i due resistori devono avere uguale valore, in sede di progetto del layout, quindi le resistenze sono state realizzate con ua struttura di tipo common centroid mostrata in fig.6.2

Figura 6.2: Common centroid layout per 2 resistori (o elementi)

Se consideriamo una variazione dovuta al processo, lineare in funzione della posizione, si puo' facilmente vedere che una struttura di questo tipo ganarintisce l'ugualianza delle due resistenze.

Infatti sommando i valori di resistenza dei singoli elementi che compongono i resistori otterremo che il resistore A vale 3+6+7+10=26 e il resistore B vale 4+5+8+9=26.

Ai fini di questo progetto sono state adattate solo le

resistenze; cio' non toglie pero' che anche altri componenti come ad esempio i transistor MOS possano essere adattati a loro volta.

Tale struttura puo infatti essere estesa anche a un caso multidimensionale diventando del tipo in fig.6.3.

Figura 6.3: Common centroyd layout per 4 resistori (o elementi)

Utilizzando una struttura mostrata in fig.6.3 sarebbe infatti possibile adattare i transistor PMOS e NMOS che vanno a comporre lo specchio di corrente in configurazione Wilson utilizzato nei circuiti mostrati nel capitolo 3.

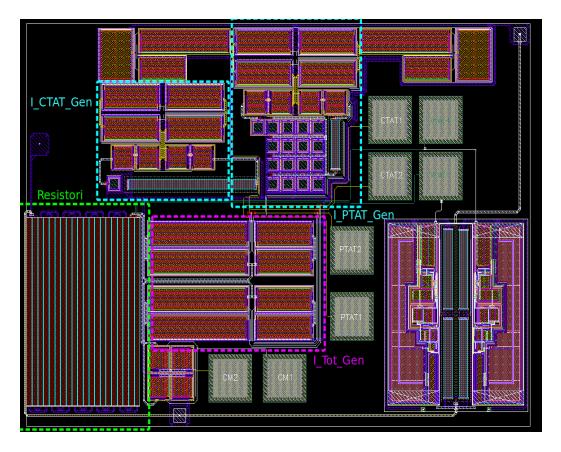

Il layout del circuito completo viene mostrato in fig.6.4

Figura 6.4: Layout completo del circuito

In fig.6.4 sono evidenziati alcuni dei componenti principali: i due resistori disegnati con layout common centroyd circondati di verde, i due circuiti I\_PTAT\_Gen e I\_CTAT\_Gen evidenziati di azzurro, i due generatori della corente totale evidenziati di rosa.

Nel layout e' possibile notare alcune piazzole che possono essere contattate con la probe station e sono utili in fase di test per verificare il corretto funzionamento del circuito.

Nell'implementazione su silicio il buffer e' stato modificato al fine di poter utilizzare una resistenza per convertire la corrente piu' piccola e far rientrare il circuito nello spazio disponibile.

Per fare cio' la tensione Vref generata e' stata dimezzata utilizzando una resistenza pari alla meta del valore calcolato.

Successivamente tale tensione e' stata moltiplicata per due attraverso un amplificatore non invertente realizzato tramite

operazionali.

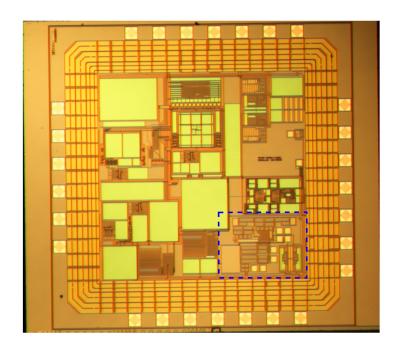

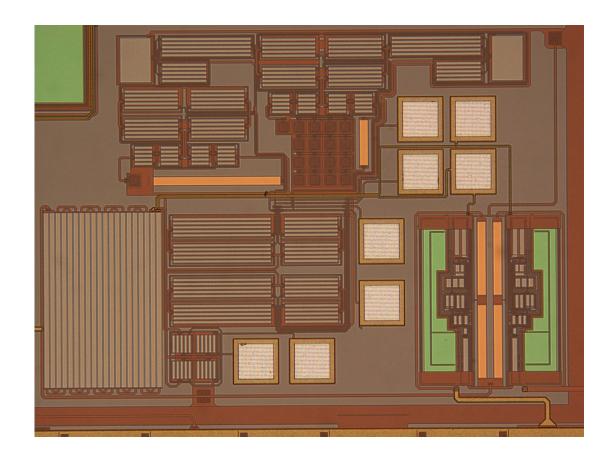

Di seguito si riporta una immagine del circuito ottenuta al microscopio (fig.6.5).

Figura 6.5: Fotografia al microscopio dell'intero chip realizzato.

Il chip occupa un'area di 5 mm<sup>2</sup>: il riferimento in tensione progettato e' stato evidenziato con il colore blu e occupa la parte in basso a destra.

Di seguito e' riportata anche una immagine contenente un ingrandimento al microscopio del circuito (fig.6.6).

Figura 6.6: Ingrandimento al microscopio del circuito realizzato su silicio

# Capitolo8

# Misure, possibili miglioramenti e conclusioni

Nel capitolo vengono presentate le misure effettuate sul prototipo di chip realizzato presso AMS C35BAC3 utilizzando una probe-station modello a quattro sonde.

Successiavamente vengono proposte soluzioni per migliorare il circuito e per renderlo programmabile.

#### 8.1 Misure

Le misure sono state realizzate su uno dei chip senza package mostrati nelle figure del capitolo precedente.

La probe-station e' fornita di quattro sonde in grado di contattare le piazzole e i pad del chip.

Per effettuare le misure, tre delle punte disponibili sono state utilizzate per fornire le tre tensioni per l'alimentazione al chip (Vdd,Vcm,gnd), mentre la quarta e' stata utilizzata per effettuare le misure sui pad e sulle piazzole del circuito.

Le misure effettuate sono indicative e non sono valide per una caratterizzazione statistica dei risultati visto lo scarso numero di campioni testati.

In tabella 8.1.1 vengono riportati i dati ottenuti.

|                                                   |                  | Misure | Simulazioni |

|---------------------------------------------------|------------------|--------|-------------|

| Tensioni di riferimento dopo buffer               | Vref+ [V]        | 2,038  | 2,102       |

|                                                   | Vref- [V]        | 1,262  | 1,198       |

| Tensioni di riferimento prima del buffer          | Vref+ [V]        | 1,844  | 1,876       |

|                                                   | Vref- [V]        | 1,455  | 1,424       |

| Polarizzazioni del generatora della corrente PTAT | I_PTAT_Bias1 [V] | 2,577  | 2,561       |

|                                                   | I_PTAT_Bias2 [V] | 1,723  | 1,662       |

| Polarizzazioni del generatora della corrente CTAT | I_CTAT_Bias1 [V] | 2,48   | 2,482       |

|                                                   | I_CTAT_Bias2 [V] | 1,522  | 1,49        |

Tabella 8.1.1: Risultati delle misurazioni effettuate sulla probe-station

Come si puo notare le due tensioni risultano essere simmetriche ma di valore pari a 388 mV, cioe' inferiore di circa il 13% rispetto al valore nominale voluto.

Cio' e' dovuto soprattutto all'incertezza sul valore delle resistenze. Una possibile soluzione a questo problema e' quella di rendere programmabile il riferimento in tensione. Tale possibilita' verra' discussa nel paragrafo successivo.

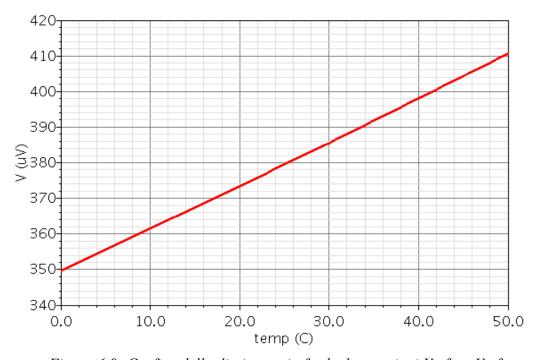

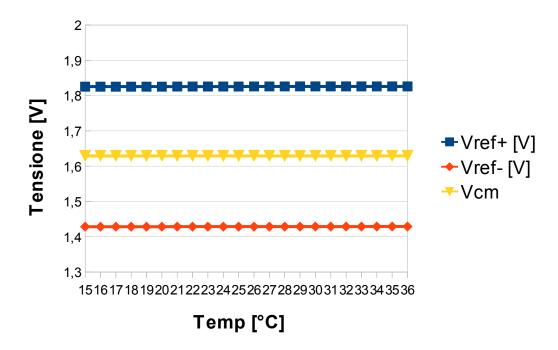

Successivamente è stata effettuata una caratterizzazione in temperatura di entrambe le tensioni al fine di verificarne la stabilità.

I risultati vengono mostrsti in fig.8.2 e in tabella 8.1.2.

Figura 8.1.1: Grafico dei dati ottenuti effettuando le misure al variare della temperatura

| Temp [°C] | Vref+ [V] | Vref- [V] | Temp [°C] | Vref+ [V] | Vref- [V] |

|-----------|-----------|-----------|-----------|-----------|-----------|

| 36        | 1,826     | 1,4291    | 25        | 1,8257    | 1,4287    |

| 35        | 1,826     | 1,4291    | 24        | 1,8257    | 1,4287    |

| 34        | 1,826     | 1,4291    | 23        | 1,8257    | 1,4287    |

| 33        | 1,826     | 1,429     | 22        | 1,8256    | 1,4287    |

| 32        | 1,826     | 1,429     | 21        | 1,8256    | 1,4287    |

| 31        | 1,826     | 1,429     | 20        | 1,8255    | 1,4286    |

| 30        | 1,826     | 1,429     | 19        | 1,8255    | 1,4286    |

| 29        | 1,826     | 1,4288    | 18        | 1,8255    | 1,4286    |

| 28        | 1,8259    | 1,4288    | 17        | 1,8255    | 1,4286    |

| 27        | 1,8259    | 1,4288    | 16        | 1,8254    | 1,4286    |

| 26        | 1,8259    | 1,4287    | 15        | 1,8254    | 1,4286    |

Tabella 8.1.2: Dati raccolti effettuando effettuando uno sweep in temperatura

Per ottenere tali risultati il chip è stato riscaldato e raffreddato per mezzo di una cella di peltier posta a contanto di un chip privato del package.

Per analizzare i risultati ottenuti occorre precisare che le misurazioni sono state effettuate sulle piazzole poste per il test e non sui pin. Questo perchè, contrariamente a quanto visto in simulazione, gli operazionali di libreria usati influenzano la caratteristica in temperatura delle tensioni che vengono generate.

Detto questo come si nota del grafico in fig.8.1.1 e dalla tabella 8.1.2 la variazione delle due tensioni risulta essere di circa 500 μV sul range di temperatura da 15 a 36°C.

# 8.2 Possibili miglioramenti

Come accennato nel capitolo precedente una prima possibilita' di sviluppo e' quella di adattare un maggior numero di componenti in fase creazione del layout su silicio.

Per la prima realizzazione infatti si e' deciso di adattare le sole resistenze che sono sicuramente un componente critico.

Cio' non toglie che anche altri componenti presentino incertezze rilevanti passando alla realizzazione fisica su silicio.

Ciascun componente ha infatti delle incertezze, modellate attraverso variabili aleatorie, ciascuna con una propria deviazione standard che dipende dal materiale di realizzazione del componente e dalle dimensioni del componente stesso.

Con una conoscenza piu accurata di quali siano le possibilita' di variazione dei componenti si puo' cercare di realizzare una struttura maggiormente insensibile al processo di fabbricazione su silicio e, qualora le incertezze non possano essere minimizzate a sufficienza, attraverso l'adattamento dei componenti si ha la possibilita' di limitare la variabilita' entro una percentuale voluta.

Basta pensare ad esempio ai fattori di forma dei transistor PMOS e NMOS che vanno a comporre i circuiti presentati nel capitolo 4; in quel caso non e' importante che i valori siano precisi ma che tutti siano uguali fra di loro o mantengano un determinato rapporto.

Ecco allora che con le tecniche di matching e' possibile migliorare questa caratteristica.

Una volta effettuati i matching di tutti i componenti sensibili e' possibile poi prevedere una rete di correzzione programmabile per le tensioni. Le soluzioni possibili sono due:

1. una prima possibilita' e' quella di sostituire le due resistenze usate come convertitore corrente/tensione con la serie fra una resistenza fissata  $R_{\rm F}$  e una resistenza variabile  $R_{\rm V}$  come mostrato in fig.8.1.

Figura 8.1: Schema del riferimento in tensione con possibilita' di trimmeraggio attraverso resistenze variabili

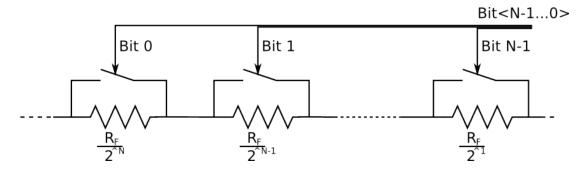

La resistenza variabile viene realizzata tramite la serie di resistori con in parallelo uno switch ciascuno dei quali e' comandato da uno degli N bit di programmazione. Una rappresentazione schematica della resistenza variabile e' mostrata in figura 8.2.

Figura 8.2: resistenza variabile da utilizzare nello schematico mostrato in fig.8.1

in questo caso la tensione di uscita puo' essere incrementata ottenendo che:

$$V_{ref+} = V_{cm} + V_{ref} + \frac{V_{ref}}{2^{N}} \cdot \overline{(Bit)_{DEC}}$$

(8.4.1)

$$V_{ref} = V_{cm} - V_{ref} - \frac{V_{ref}}{2^{N}} \cdot \overline{(Bit)_{DEC}}$$

(8.4.2)

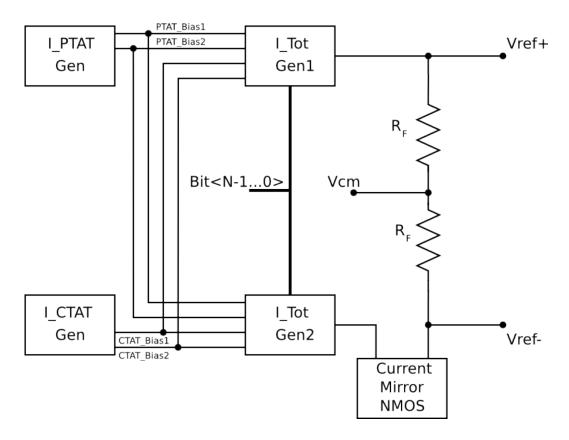

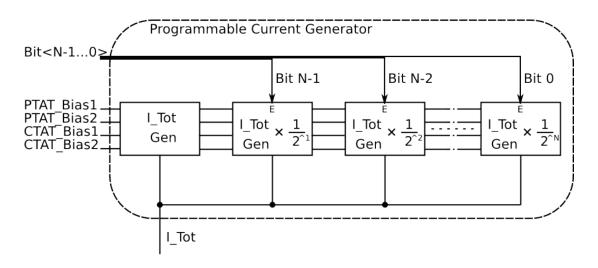

2. Un'altra possibile implementazione di un trimmeraggio digitale del riferimento in tensione proposto potrebbe consistere nel mantenere fissa il valore di resistenza e variare la corrente che circola attraverso un generatore di corrente programmabile tramite N bit, come mostrato in figura 8.3.

Figura 8.3: Circuito del riferimento in tensione realizzato con generatore di corrente variabile

Il generatore di corrente da utilizzare viene mostrato in fig.8.4

Figura 8.4: Generatore di corrente programmabile utilizzabile nel circuito mostrato in fig.8.3

Tale soluzione permette di ottenere due tensioni programmabili del valore di:

$$V_{ref} = V_{cm} + V_{ref} + \frac{V_{ref}}{2^{N}} \cdot (Bit)_{DEC}$$

(8.4.3)

$$V_{ref} = V_{cm} - V_{ref} - \frac{V_{ref}}{2^{N}} \cdot (Bit)_{DEC}$$

(8.4.4)

Va valutato quindi quale delle due soluzioni possa presentare caratteristiche migliori di matching e occupazione di area.

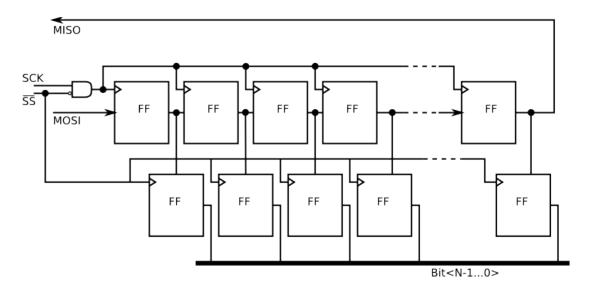

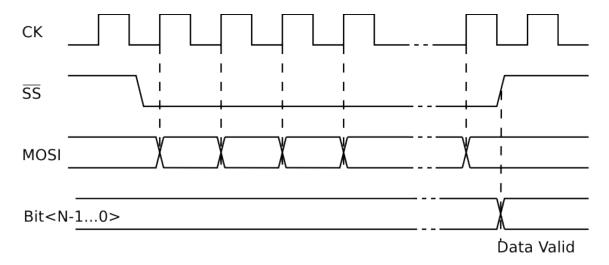

Per rendere possibile la programmazione dei due circuiti occorre implementare anche una interfaccia SPI (Serial Peripheral Interface Bus). Di seguito, in fig. 8.5 e fig. 8.6 se ne riporta uno schema con le relative forme d'onda.

Figura 8.5: Schema di una interfaccia SPI

L'interfaccia e' formata da un registro a scorrimento e da un registro che rende disponibile il dato al termine della trasmissione.

Figura 8.6: Forme d'onda di una trasmissione SPI

L'inizio della tasmissione avviene quando il segnale SS (Slave Select) diventa basso.

I dati provenienti dal master "scorrono" quindi nello shifterregister fino a che il segnale SS non torna a livello alto.

Su questo fronte di salita la trasmissione e' terminata e il dato viene reso disponibile.

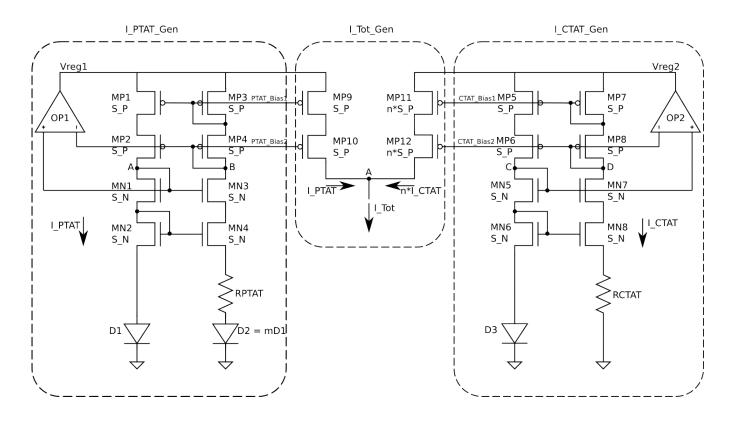

Come ultimo possibile miglioramento del circuito viene presentata una soluzione che permette di incrementare il PSRR (fig.8.7).

Figura 8.7: Soluzione circuitale per incrementare il PSRR del Voltage reference progettato

I due operazionali OP1 e OP2, posti in retrazione, fissano rispettivamente le tensioni nei punti A e B (OP1), C e D (OP2) e fanno in modo che i circuiti di generazione delle tensioni di riferimento siano alimentati attraverso una tensione generata internamente (Vreg1, Vreg2) rendendo il circuito piu insensibile alle fluttuazioni dell'alimentazione esterna.

La regolazione puo' essere descritta come segue; l'incremento di Vdd causa l'incremento della tensione Vreg facendo incrementare così il flusso di corrente attraverso i transistor MN1 e MN3 e, di conseguenza, della tensione di drain dei due transistori.

L'operazionale amplifica la differenza di queste due tensioni e, grazie al controllo in retroazione, tende a far abbassare la Vreg ristabilendo la situazione di partenza.

#### 8.3 Conclusioni

Nell'elaborato viene presentato un riferimento in tensione in grado di generare due tensioni simmetriche del valore di 450 mV stabili in temperatura.

L'architettura proposta risulta essere di nuova concezione dato che durante l'attività di ricerca non sono stati trovati circuiti in grado di fornire questo tipo di riferimento in tensione.

Come si nota dalle simulazioni effettuate il circuito garantisce un elavato livello di simmetria delle tensioni generate e un andamento in temperatura paragonabile alle soluzioni presentate in letteratura.

Durante l'implementazione del circuito sono stati affrontati tutti i problemi dovuti alle incertezze del processo di realizzazione in modo da poter minimizzare tali effetti sul circuito realizzato su silicio.

Le misurazioni effettuate su un singolo chip hanno dimostrato che il circuito rispecchia le prestazioni ottenute con le simulazioni e che il matching dei componenti ha permesso di limitare le imprecisioni delle tensioni generate facendo si che la principale causa di variazione sia il solo valore nominale dei resistori.

Infine sono state proposte alcune possibili miglioramenti da apportare al circuito proposto al fine di migliorarne le prestazioni e la precisione.

## **Bibliografia**

- [1] Byung-Do Yang, Young-Kyu Shin, Jee-Sue Lee, Yong-Kyu Lee, and Keun-Chul Ryu VLSI Circuit & System Lab., Chungbuk National University, Cheongju, Chungbuk, Republic of Korea, "An Accurate Current Reference using Temperature and Process Compensation Current Mirror", IEEE Asian Solid-State Circuits Conference November 16-18, 2009 / Taipei, Taiwan.

- [2] Shen Hui, Wu Xiaobo and Yan Xiaolang, "A Precise Bandgap Reference with High PSRR", Electron Devices and Solid-State Circuits, 2005 IEEE Conference on, 19-21 Dec. 2005

- [4] Huang Xiaomin, Shen Xubang, Zhou Xuecheng, and Jang Xiang, "A Precise CMOS Bandgap Voltage Reference," in ELECTRONIC ENGINEER, 2004.

- [4] R. J. Baker, CMOS Circuit Design, Layout, and Simulation, 2nd ed. New York: John Wiley and Sons, 2005

- [5] Zhu Tiancheng, Yao Suying, and Li Binqiao, "A high precision programmable bandgap voltage reference design for high resolution ADC" School of Electronic Information Engineering, Tianjin University, Tianjin 300072, China

- [6] Jin L, Xing H, Chen D, "A self-calibrated bandgap voltage reference with 0.5 ppm/°C temperature coefficient", IEEE International Symposium on Circuits and Systems, 2006, 4: 2856

### Ringraziamenti

Portando a termine questo elaborato chiude un percorso di studi durato 5 anni volevo ringraziare innanzitutto la mia fimiglia, che ha ha reso possibile questa esperienza universitaria.

Vorrei ringrazioere anche tutti I ragazzi, ricercatori e dottorandi, che lavorano alla seconda facolta' di ingegneria qui a cesena.

In particolare Federico Thei, Marco Crescentini, Marco Bennati, Michele Rossi che hanno lavorato con me per questi ultimi 9 mesi mettendo a mia disposizione la loro competenza e la loro esperienza.

Ringrazio il mio relatore Marco Tartagni che mi ha dato la possibilita' di affrontare un percorso di tesi completo e di alto livello.

Infine ringrazio la mia ragazza Chiara che e' stata con me per tutto lo svolgimento della laurea specialistica e della tesi e I miei amici con cui ho passato bellissimi momenti in questi uktimi due anni.

E' grazie a tutte queste persone che porto oggi a compimento un percorso di studi impegnativo ma che mi lascia molto piu ricco di prima.

Auspicando che la mia passione per l'ingegneria e la ricerca possa proseguire in futuro in ambito lavorativo e non ringrazio tutti per l'attenzione.