# Alma Mater Studiorum · Università di Bologna

# SCUOLA DI SCIENZE Corso di Laurea in Informatica

# Porting of the $\mu$ MPS3 Educational Emulator to RISC-V

Relatore: Chiar.mo Prof. Renzo Davoli Presentata da: Gianmaria Rovelli

I Sessione Anno Accademico 2022/23

Sometimes it is the people no one can imagine anything of who do the things no one can imagine. Alan Turing

#### Abstract

Teaching operating systems to students has always been a challenging task for lecturers. To address this issue, educational architectures, and emulators have been developed to offer students an easier entry point into the subject matter.

In this context, Virtual Square has created a simplified architecture named  $\mu$ MPS, along with its emulator. This simplified architecture serves as a starting point for students to familiarize themselves with the operating systems, allowing them to gain foundational knowledge and understanding in the field.

Virtual Square has developed a range of software tools that emulate the MIPS and ARM RISC architectures. In recent years, RISC-V has emerged as a new and interesting RISC architecture. Known for its open-source nature, RISC-V offers a promising instruction set architecture. One of its significant advantages is the ability for students and professionals to directly study and customize the architecture, making it a valuable resource for learning and exploration. This thesis aims to expand Virtual Square's software family by incorporating the new RISC-V architecture, inheriting the skeleton of the previous project  $\mu$ MPS3.

#### Sommario

Insegnare i sistemi operativi agli studenti è sempre stato un compito impegnativo per i docenti. Per affrontare questo problema, sono state sviluppate architetture didattiche ed emulatori con l'obiettivo di offrire agli studenti un approccio semplificato a questa materia complessa.

In questo contesto, Virtual Square ha sviluppato, insieme al suo emulatore, un'architettura semplificata chiamata  $\mu$ MPS. Questa architettura è stata progettata con l'obiettivo di fungere da punto di partenza per gli studenti, offrendo loro l'opportunità di familiarizzare con i sistemi operativi, di acquisire conoscenze e comprensione fondamentali in questa materia.

Virtual Square ha sviluppato una gamma di strumenti software che emulano le architetture di tipo RISC: MIPS e ARM. Negli ultimi anni è comparsa RISC-V, una nuova e interessante architettura RISC. Conosciuta per la sua natura open source, RISC-V offre una promettente architettura di istruzioni. Uno dei suoi punti di forza è la possibilità che da a studenti e professionisti di studiare e personalizzare direttamente l'architettura, rendendola una risorsa preziosa per l'apprendimento e l'esplorazione. Lo scopo di questa tesi è espandere questa famiglia di software sviluppata da Virtual Square incorporando la nuova architettura RISC-V, ereditando lo scheletro del precedente progetto  $\mu$ MPS3.

# Contents

| 1 | Inte | RODUCTION                                                                                           | 1  |  |  |  |  |  |  |  |  |  |  |  |  |

|---|------|-----------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|--|

|   | 1.1  | State of the Art                                                                                    | 1  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.2  | Background                                                                                          | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.1 RISC-V                                                                                        | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.2 $\mu$ MPS                                                                                     | 4  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.3 Emulation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 5  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.4 Translation Lookaside Buffer (TLB) $\ldots \ldots \ldots$                                     | 6  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.5 Disassembler $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 7  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.6 Debugger $\ldots$                                                                             | 8  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.7 Symbol Table $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 9  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.8 Toolchain $\ldots$                                                                            | 10 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.9 Build System                                                                                  | 11 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.3  | Objective                                                                                           | 13 |  |  |  |  |  |  |  |  |  |  |  |  |

| 2 | Impi | Implementation                                                                                      |    |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1  | Processor                                                                                           | 15 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.1 New Processor's State                                                                         | 16 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.2 Removed Coprocessor                                                                           | 17 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.3 Control and Status Register (CSR) $\ldots \ldots \ldots$                                      | 17 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2  | Exception Handling                                                                                  | 20 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.1 Processor Behaviour                                                                           | 21 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.3  | BIOS                                                                                                | 23 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.3.1 Bootstrap                                                                                     | 23 |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.3.2 Library Services                                                                              | 24 |  |  |  |  |  |  |  |  |  |  |  |  |

## Contents

|   | 2.4 | Device   | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26 |

|---|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 2.4.1    | Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26 |

|   | 2.5 | A sim    | ple disassembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27 |

|   |     | 2.5.1    | Usage $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27 |

|   | 2.6 | GNU I    | Debugger (GDB) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27 |

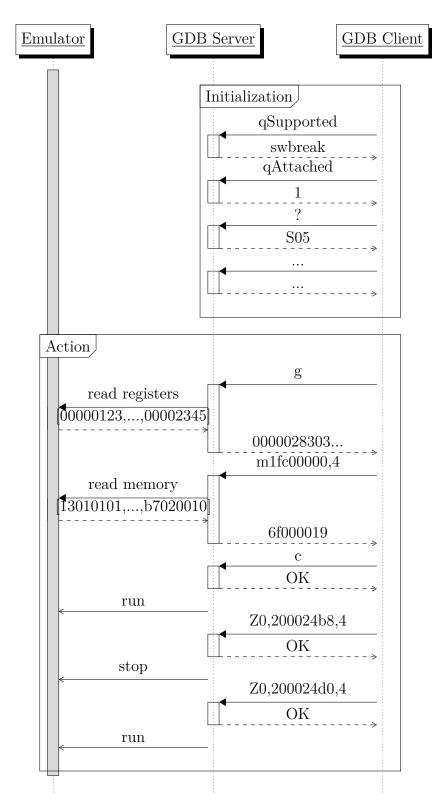

|   |     | 2.6.1    | $Design \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 |

|   |     | 2.6.2    | Features implemented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30 |

|   |     | 2.6.3    | Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32 |

|   | 2.7 | Utilitie | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33 |

|   |     | 2.7.1    | uriscv-elf2uriscv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33 |

|   |     | 2.7.2    | $uriscv\text{-}mkdev \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

|   |     | 2.7.3    | uriscv-mkconfig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34 |

|   | 2.8 | Comm     | nand-Line Interface (CLI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35 |

|   |     | 2.8.1    | Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36 |

| 3 | Ραν | dOS pi   | I US                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37 |

| 0 | 3.1 |          | roject                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37 |

|   | 0.1 | 3.1.1    | Phase 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38 |

|   |     | 3.1.2    | Phase 2       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . </td <td>39</td> | 39 |

|   |     | 3.1.3    | Phase 3       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . </td <td>40</td> | 40 |

|   | 3.2 |          | iling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41 |

|   | 0.2 | 3.2.1    | Toolchain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41 |

|   |     | 3.2.2    | Compiling the kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42 |

|   |     | 3.2.3    | Compiling the User processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43 |

|   | 3.3 |          | ng PandOS on $\mu$ RISCV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44 |

|   | 0.0 | 3.3.1    | Making the config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44 |

|   |     | 3.3.2    | Running the Emulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44 |

|   | ~   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4 |     | ICLUSIO  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45 |

|   | 4.1 | -        | vements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45 |

|   |     | 4.1.1    | Memory Management Unit (MMU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45 |

|   |     | 4.1.2    | Terminal Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46 |

|   |     | 4.1.3    | Graphical Interface and GDB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46 |

#### Contents

|        | 4.1.4  | Software | Pack | agin | g. | <br> | <br>• |       | <br>• |   | <br>• |   |   | 47 |

|--------|--------|----------|------|------|----|------|-------|-------|-------|---|-------|---|---|----|

| 4.2    | Final  | thoughts |      |      |    | <br> | <br>• | <br>• | <br>• | • | <br>• | • | • | 47 |

| Biblio | GRAPHY | Ý        |      |      |    |      |       |       |       |   |       |   |   | 51 |

| Acknow | WLEDG  | EMENTS   |      |      |    |      |       |       |       |   |       |   |   | 55 |

# 1 INTRODUCTION

This chapter presents a summary of the subject matter, providing the reader with adequate background knowledge to comprehend the Implementation section (see chapter 2). Furthermore, it aims to establish the objective of the thesis.

# 1.1 State of the Art

Educational emulators represent cutting-edge technology in the education field, providing immersive and interactive learning experiences that bridge the gap between theory and practice. These software applications emulate real-world environments, allowing students to explore and engage with various subjects in a safe and controlled virtual setting. With the advancement of technology, educational emulators have evolved to offer increasingly sophisticated and realistic simulations, revolutionizing the way we teach and learn across multiple disciplines.

Over the years, multiple projects have been initiated to educate individuals about the intricacies of computer architecture. Albeit many researchers have expressed their concern about the difficulty of that task [3], this effort has been acknowledged as a crucial undertaking, as it guarantees continuous advancement and exploration in the development and research realm. Projects worth to be cited are (three of them suggested by C. Yehezkel and W. Yurcik [36]) *EasyCPU* [36], *Little Man Computer* [36, 37], *RTLSim* [36], and *Nand2Tetris* [28]. *EasyCPU* [36] is a simulator designed to emulate a simplified version of the Intel X86 microprocessor. It offers users a user-friendly graphical user in-

terface (GUI) that allows them to edit, assemble, execute, and debug programs. Little Man Computer [36, 37] is a web-based simulation tool aimed at providing students with a comprehensive understanding of the internal operations of a CPU, including the fetch-execute cycle. On the other hand, RTLSim [36] simulates a non-pipelined processor similar to MIPS, where the user assumes the control unit (CU) role. The last cited project was incorporated as a component of the Computer Architecture examination in the Computer Science course (2020/2021) at the University of Bologna. Nand2Tetris [28] is a stepby-step course where participants acquire fundamental computer knowledge, starting from the basic logic gate NAND [20] and progressing to developing complex programs such as Tetris [29].

Over the years, the complexity of what such projects could achieve increased, even though keeping such works user-friendly and approachable to undergraduate students. For instance, VisibleZ [35] is a mainframe architecture emulator that helps students to understand how the mainframe technology works and its inner components, including storage and I/O channels. In *VisibleZ*, users can also define their instructions with custom semantics, broadening their understanding of how computer architectures work. Related to the RISC-V instruction set and this thesis, it is relevant to cite three recent projects: EmulsiV [31], riscvOVPsim [17], and  $\mu MPS$  [15]. EmulsiV [31] is a visual simulator based on the minimal <sup>1</sup> subset of the RISC-V instruction set called *Virgule* [31]. In EmulsiV, the users, albeit limited by design, can discover how a processor works, compiling a C program, linking it, and executing it, giving them a broad overview of such a process. In addition, riscvOVPsim [17] is a RISC-V Instruction Set Simulator (ISS) perfect entry point for learning computer architecture. It provides users with debugging facilities. The students' source code can be compiled easily using a cross-compiler, while the GUI helps the users to see memory and register values. One of the key features of *riscvOVPsim* is the possibility to simulate real Operating Systems (OS) and Real-time operating systems (RTOS).  $\mu MPS$  [15] provides users with a user-friendly GUI, debugging features, and virtual memory management, allowing students to develop

<sup>&</sup>lt;sup>1</sup>"minimal" means only the base instructions generated from a simple C program

their operating system and run it using the emulator bundled with  $\mu$ MPS.  $\mu$ MPS is described in further detail in section 1.2.2.

# 1.2 BACKGROUND

This section provides the reader with an understanding of the larger context and offers a concise description of the subjects that have been addressed in the thesis.

# 1.2.1 RISC-V

RISC-V is an open standard instruction set architecture (ISA). The name "RISC-V" stands for "Reduce Instruction Set Computer - Version 5", which means that RISC-V is designed based on the reduced instruction set computer (RISC) principles. RISC-V is available under royalty-free open-source licenses, which means that any firm or user can freely use, modify, distribute, and incorporate code to RISC-V without the need to pay royalties or licensing fees. The RISC-V ISA is a load-store architecture, meaning that the instructions are of two categories: memory access and arithmetic logic unit (ALU) operations.

The principal characteristics of the RISC-V ISA include:

- Openness and Modularity: RISC-V is an open standard, meaning anyone can access and contribute to its development. The design of RISC-V allows it to be modular, letting the user select specific instruction sets that best suit their needs;

- *Simplicity*: the instructions provided by the RISC-V ISA are minimal and easy to decode. The core instruction set provides the basic operations, while more complex instructions, such as vector processing is available thanks to the extensions;

- Multiple Privilege Levels: RISC-V supports a hierarchical privilege model with multiple privilege models (in  $\mu$ RISC-V just user and machine-level

are used). This allows the implementation of operating systems and virtualization techniques;

- *Scalability*: RISC-V is designed to be used either on embedded devices or high-performance computing systems. It supports 32-bit, 64-bit, and 128-bit words, although the latter is still "not frozen"<sup>2</sup>.

- *Software Ecosystem*: due to the open nature of RISC-V, the ecosystem of compilers, development tools, and libraries for that architecture has grown considerably.

The RISC-V ISA has become popular among students and educational institutions as a valuable learning resource thanks several reasons. First of all, the openness of RISC-V allows students to approach it easily, while onlinea documentation fosters hands-on exploration. Although remaining a very expressive architecture, the simplified architecture makes RISC-V a perfect entry point for students new to computer architecture. For instance, on a RISC-V core can be executed Linux [18]. Over the years, the community has grown, and numerous educational content appeared on the Internet, such as courses, tutorials, and community-driven projects.

## $1.2.2 \ \mu MPS$

$\mu$ MPS is an educational computer system architecture that aims to be simple but remains realistic. The  $\mu$ MPS processor implements the MIPS I <sup>3</sup> instruction set, avoiding the need to develop a compiler for it, since the existing MIPS compilers work.

The architecture and its emulator are now at their third version (fourth if we consider MPS, see Preface in [13]):  $\mu$ MPS3, which is not backward compatible with  $\mu$ MPS2 (nor  $\mu$ MPS). The evolution of  $\mu$ MPS has been gradual:

<sup>&</sup>lt;sup>2</sup>Frozen means that it is being reached a point in the development after which making changes to ISA has become strictier

$<sup>^{3}</sup>$ MIPS R2000/R3000

- 1. *MPS* [27]: it is the first attempt, but the virtual memory management was unsuitable for undergraduates;

- 2.  $\mu MPS$  [15]: implemented the virtual memory management that better matched the theory of textbooks;

- 3.  $\mu MPS2$  [19]: upgrade of the GUI, multiprocessor support implemented, and debugging features;

- 4.  $\mu MPS3$  [13, 1]: migrating from GNU Autotools [8] to CMake [4], changed exception handlers, migrating the GUI to Qt5, and introduced the new class of flash devices.

All these projects are part of the project family under the umbrella of Virtal-Square [12].  $\mu$ ARM [22] is another project from the same family, that shares the same goals with  $\mu$ MPS, but through a more popular architecture: ARM (used in almost every Android device).

#### 1.2.3 Emulation

Emulation is a powerful technique that replicates the behavior and functionality of one system on another. It enables running software or operating systems designed for a specific platform on different hardware or software environments. Emulation can be achieved through software or hardware approaches.

Software emulation involves creating an emulator that interprets instructions intended for the original hardware and executes them on the host system. This method allows running legacy software on modern computers or virtual machines, extending the lifespan and accessibility of obsolete systems. The emulation of gaming consoles, such as the GameBoy, is a perfect example of software emulation.

Hardware emulation goes beyond software emulation by replicating both the software and physical hardware components of the target system. It requires building specialized hardware platforms that accurately mimic the architecture and behavior of the original system. Hardware emulation is particularly useful

for studying, debugging, and analyzing complex systems at a low level. For instance, the MiSTer project <sup>4</sup> is a popular hardware emulation platform based on FPGA (Field Programmable Gate Array) technology.

Emulation offers students valuable opportunities to explore and understand different computer systems, software, hardware, and programming concepts interactively. By emulating the behavior of different computer architectures, to say one, emulation provides a practical and immersive learning experience. By examining the behavior of emulated systems at the hardware level, students can gain insights into concepts such as instruction execution, memory management, and I/O operations. Emulation platforms enable them to experiment with different instruction sets and architectures, fostering a deeper understanding of computer organization and design, which is one of the goals of  $\mu$ RISCV.

## 1.2.4 TRANSLATION LOOKASIDE BUFFER (TLB)

The Translation Lookaside Buffer (TLB) is a relevant component in computer science systems that helps the efficiency of virtual memory management. It serves as a cache for memory address translations, reducing the time and resources required to access data from a physical address.

The TLB consists of an array of entries, with each storing a virtual-to-physical address mapping. Each entry typically contains the virtual page number, the corresponding page number, and other control bits, such as the dirty bit. The TLB is organized as a content-addressable memory ( $\mu$ RISCV uses this type of TLB) or a hash table, allowing for fast associative lookup based on virtual page numbers.

The TLB works besides the memory management unit (MMU) and the page table to translate virtual addresses into physical ones. When a program references a memory location, the TLB first check a match in its cache. If there is, the TLB retrieves the corresponding physical address directly, avoiding the

<sup>&</sup>lt;sup>4</sup>https://mister-devel.github.io/MkDocs\_MiSTer

need to access the page table. In the event of a TLB miss, where the requested virtual address is not found in the TLB, the MMU performs a page table walk to retrieve the information needed to: fill the TLB (TLB-Refill event in PandoOS plus [14]) and complete the translation.

## 1.2.5 DISASSEMBLER

A disassembler is a powerful tool that analyzes binary code and converts it into assembly language instructions. It plays a vital role in reverse engineering, software debugging, and understanding the inner workings of compiled programs. The disassembler's work is the symmetrical opposite of the assembler's one.

The disassemblers operate by reading the binary code of a program, analyzing the code, identifying the operation code (opcode), and translating it into their corresponding mnemonic representations. The disassembler's output provides details about the program's instructions, including the opcode, operands, registers, memory addresses, and control flow instructions.

One main application of a disassembler is reverse engineering, where it enables the examination of compiled software without having access to the source code. Reverse engineering can use the disassembled code to analyze the algorithm, identify vulnerabilities, understand program behavior, perform malware analysis, and extract valuable information such as data structures, function names/calls, and control flow.

In addition, a disassembler plays a vital role in debugging and troubleshooting. When investing the reasons behind a program's crash, the disassembler allows the developers to trace the execution flow, and examine the registers and memory to identify potential bugs or errors.

Disassemblers can be found in various forms, ranging from standalone commandline tools to integrated development environment (IDE) plugins. Some disassemblers offer advanced features such as symbolic debugging (such as  $\mu$ RISCV), cross-referencing, and graph visualization to assist the code analysis.

# 1.2.6 Debugger

*Debuggers* are powerful tools, that allow the programmers to analyze the program execution. They assist developers in the laborious activity of bug finding and error fixing. Debuggers provide a wide range of features to aid in the debugging process, such:

- *Breakpoints*: debuggers allow programmers to set breakpoints at a specific line of code, which pause the normal execution flow when reached and allow a to examine the current status of the program, including the processor's state;

- *Variable inspection*: developers can inspect variables' value at specific points of the program, helping them to discover potential issues;

- *Call stack and Stack trace*: debuggers keep trace and display the call stack, which shows the sequence of function calls that led to the current point in the program. This feature helps the developer to understand the path, and which branches have been taken to reach a point of the execution;

- *Watchpoints*: watchpoints are similar to breakpoints, but they can be set only on variables and are triggered when such variables change their values. This helps track down unexpected modifications and avoid useless interruptions;

- *Stepping and flow control*: debuggers provide the functionalities to run programs step-by-step, to step over lines (bypassing checking), and to step out to return to the calling function;

- *Memory inspection*: debuggers allow developers to inspect the content of an arbitrary memory location, helping them to identify potential issues, such as buffer overflow or memory leaks.

- Debug symbols: debuggers work in conjunction with a compiler to incorporate debug symbols into the executable (see section 1.2.7).

Debuggers are essential tools for software development, not only do they help find issues, but they also accelerate the whole process. In the  $\mu$ RISCV project, a *debugging stub* (see section 2.6) has been implemented. A *debugging stub* is a component of the debugging system that resides on the target device. It works as a bridge between the debugger and the host machine. A debugging stub provides communication channels and services that enable the exchange of debugging information and commands between the target (e.g.  $\mu$ RISCV) and the debugger.

# 1.2.7 Symbol Table

The symbol table is a data structure used by compilers, linkers, and debuggers to store information about symbols (names) in a program. It serves as a database for mapping symbols to their attributes and provides efficient lookup.

The symbol table stores a wide range of information related to symbols, including variable names, function names, constants, labels, memory addresses, and their respective offsets. It also keeps track of data types, scope information, visibility, and other relevant attributes.

During the *compilation phase*, the symbol table is populated by the compiler as it scans the source code. Symbols encountered such functions and variables are added to the table. This allows, later on, the compiler to perform name resolution, type checking, and other semantic analysis tasks.

In the *linking phase*, the symbol table plays a relevant role, especially in resolving external symbols. Indeed, when multiple object files (programs, modules) are compiled together in a single executable or library, the linker can use symbols already resolved in one program on another one, reducing the linking time and avoiding issues related to redundancy.

*Debuggers* utilize the symbol table to facilitate program debugging. When debugging a program, the debugger can access the symbol table to display meaningful names and information about the variables and functions currently

involved in the debugging (this is the case of  $\mu$ RISCV). This helps programmers in understanding state, set breakpoints, and examine stack traces.

#### 1.2.8 TOOLCHAIN

A toolchain is a collection of development tools that work together to facilitate the building, compilation, testing, and deployment of complex software. It includes tools like compilers, linkers, assemblers, debuggers, and code analyzers.

The streamline of the software development process made in the act by a toolchain usually begins with the compiler. A compiler is a tool that translates highlevel source code into machine code or an intermediate machine language. Compilers convert the code written in programming languages like C, C++, and Rust into executable or object files.

Once the source code is compiled, the *linker* comes to play. The role of the linker is to resolve symbols and references, combine object files and generate the final executable of library files. It ensures that all the dependencies are linked together and that the program can run.

Assemblers are a vital component of toolchains, especially when programming in low-level languages. They translate assembly language code into machine code, providing a bridge between human-readable instructions and the computer's processor.

*Debuggers* are powerful tools, that allow the programmers to analyze the program execution (see section 1.2.6).

*Code analyzers* and static analysis tools perform static code analysis. They examine the code for potential errors, security vulnerabilities (CVE) [25], code quality issues, and coding standards (e.g. naming convention, refactoring). These tools assist developers in writing cleaner, safe, and more maintainable code.

In addition to these tools, a toolchain may also include *profiles*, *performance* analysis tools, documentation generators, build systems (see section 1.2.9), and version control systems.

Toolchains can be customized based on the language, target platform, and development workflow. A particular type of toolchain called *cross-platform* toolchains allows the developer to write code on platform A to compile an executable targetted for platform B. It provides a unified development environment, allowing developers to write code once and deploy it across different platforms without significant modifications. To achieve the goal of cross-platform compatibility, toolchains often rely on inherently portable programming languages, such as C, C++, or Python. Cross-platform toolchains allow developers to develop the program without directly owning the target machine, reducing the cost for the programming environment in its complex. In general, they provide various advantages, including code reusability, faster development cycles, and reduced maintenance efforts.

In this dissertation, to compile the PandoOS plus project (see chapter 3), the RISC-V GNU cross-platform toolchain <sup>5</sup> has been used, since usually, the developer host's architecture is x86, while the project has to be compiled for the RISC-V architecture.

#### 1.2.9 Build System

A *build system* is a software tool that automates the process of compiling source code, linking dependencies, and generating executables or object files. It provides a structured and repeatable approach to building software applications, simplifying the complex sequence of steps to perform to transform source code into a runnable application.

<sup>&</sup>lt;sup>5</sup>The GNU cross-platform toolchain can be found on GitHub: https://github.com/ riscv-collab/riscv-gnu-toolchain

The main goal of a build system is to provide efficiency, consistency, and reliability in the process of building an executable independently from the platform or development environment.

One of the striking features of a build system is the ability to track dependencies between source files. Moreover, it can manage the subsequent build, when a build is triggered, the system only recompiles the changed source, avoiding unnecessary recompilation and speeding up the whole process.

In addition, a build system is also capable of managing external dependencies, automatically downloading required libraries, and integrating them into the project. This feature assists developers to find and keep dependencies upgraded, especially among different platforms.

Another relevant feature of build systems is their integration with version control systems. Indeed they often support continuous integration (CI) and continuous delivery (CD) workflows. This allows to automatize the whole process of compiling, testing, and generating deployable artifacts.

Many are popular build systems, such as Make, Maven, Gradle, and Autotool, each with its advantages and features for specific programming languages.

*Make* is one of the most popular build systems. It is generally used to build software, but it has applications whenever arbitrary commands need to be executed. When executed, Make searches the current directory for a *makefile*, which is a well-formatted list of rules. Although Make is an incredible tool, it has problems when comes to executing a makefile on different platforms. For instance, a compiler on x86 might not accept the same options on RISC-V. To resolve this issue, tools like Cmake or Autoconf, have been developed.

Cmake is not a build system itself, indeed it only generates configuration files for other build systems like Make. It allows developers to specify project structure, dependencies, compiler options, and other build-related settings in a CMakeLists.txt file. One of the key advantages of CMake is that developers can define different configurations based on, for instance, platform or compiler availability. In addition, it provides a modular and hierarchical approach to organizing projects, allowing the creation of libraries, executables, and subprojects, keeping a clear and structured representation of complex software.

# 1.3 Objective

The learning-by-doing principle is a widely adopted teaching method, where the students learn hands-on on a practical project: their source of knowledge is the direct experience [26].  $\mu$ RISCV and all the versions of  $\mu$ MPS agreed with such a theory. This project aims to teach students how computer architecture and operating systems work, avoiding relatively useless and convoluted implementation details, that spread in those fields. Inner components had to be simplified, to achieve the goal of practical learning and maintain the project's realism. For instance, even though students do not directly manage external devices, they understand their functioning and how to interact with them.

The previous MIPS-based editions of  $\mu$ MPS ( $\mu$ MPS2,  $\mu$ MPS3) were optimal for teaching, but not ahead of the time, since nowadays its real-world applications are rare. On the other hand, RISC-V (see section 1.2.1), an emerging instruction set architecture, is gradually revolutionizing the entire market, thanks to its versatility ranging from embedded devices to high-performance computers.  $\mu$ RISCV provides an entry point for students to discover this practical instruction set.

The knowledge acquired through the utilization of  $\mu$ RISCV should not be limited to its specific environment, but rather it should be transferable and applicable in diverse contexts. For instance, the debugger feature section 1.2.6, which uses GDB [10], is a practical skill that students can reuse in future projects, thanks to the popularity of GDB.

To summarize, the objectives of  $\mu$ RISCV are: teaching students the fundamental concepts of computer architectures and operating systems in a straightforward yet realistic manner; introducing students to the RISC-V instruction set, which holds great potential for future advancements and innovations in the field of computer architecture; enabling students to acquire skills that extend

beyond the specific  $\mu \rm RISCV$  environment, ensuring that the knowledge and competencies gained are applicable and transferrable to other contexts.

# 2 Implementation

This chapter covers the implementation of  $\mu$ RISCV, including all the additional and modified features. By the end of this chapter, the reader should have a clear understanding of how the processor, exception handling, and other components of the emulator function. The assumption is that the reader already possesses an overview of  $\mu$ MPS3, enabling them to comprehend extensively the enhancements made by this porting.

# 2.1 Processor

The processor is the heart of the computer and so of the emulation. It is responsible for operations like fetching, decoding, and executing the program's instructions, commonly called Fetch-Decode-Execute (FDE) cycle. The  $\mu$ RISCV's processor emulates the *RV32I* [33] version supporting the Integer Multiply/Divide (I) extension. Every machine cycle, the processor checks whether the *CPU TIMER* (see section 2.2) interrupt has to be signaled, then the previously fetched instruction is executed. If an exception occurs during the previous step, the exception handler is called while the various registers are correctly assigned to handle it. After incrementing the PC (Program Counter), the processor checks for the interrupts. If an interrupt occurs during this process, similarly to exceptions, the exception handler will tackle it. In the end, the processor fetches the next instruction, and whether necessary, the MMU translates its address from a virtual to a physical address. The executing behavior of the processor's steps heavily depends on the ISA. The various op-

#### 2 Implementation

codes defined by RISC-V, based on their composition, can be divided into six groups:

- *R type*: branching instructions (BEQ, BNE, BLT, BGE, BLTU, BGEU);

- *I type*: basic unsigned integer arithmetic and bitwise instructions (ADDI, SLLI, XORI, ANDI, etc.);

- *I2 type*: operations over CSR (see section 2.1.3) and break, ecall, return instructions (non-canonical);

- *S type*: store instructions;

- *U type*: sign extended unconditional jump instructions;

- *J type*: unconditional jump instructions;

The phases of Decoding and Execute of the instruction are combined to simplify the logic of the processor, while the Fetch of the new instruction is accomplished immediately after those two steps.

# 2.1.1 New Processor's State

A processor state is the collection of information and data that represents the current condition and context of the processor's execution. The processor's state constantly changes as instructions are fetched, executed, and results are stored in registers. During a context switch, the processor's state is saved to memory by a BIOS routine (see section 2.3), and another state previously saved in memory is executed.

Since the status register no more holds information about the interrupts enabled, a new register, called *mie* (see fig. 2.6), must to be saved in the processor's state.

Listing 2.1: Processor's state

```

typedef struct state {

unsigned int entry_hi;

```

```

unsigned int cause;

unsigned int status;

unsigned int pc_epc;

unsigned int mie;

unsigned int gpr[STATE_GPR_LEN];

} state_t;

```

Every field of the processor's state stores the corresponding register value (see section 2.1.3). For instance,  $entry\_hi$  holds  $CSR\_ENTRYHI$  value.

The hi and lo fields, previously dedicated to holding results from multiplication and division operations (see 2.1 of [13]), have been completely removed since unused in  $\mu$ RISCV.

#### 2.1.2 Removed Coprocessor

The  $\mu$ MPS3 project included a coprocessor, which extends the processor functionality. Such a coprocessor had a series of special purpose registers and provided support for two operation modes, for exception handling, a processor Local Timer, and a Memory Management Unit (MMU) [13]. Unlike MIPS, which provides support for an ISA-level coprocessor, RISC-V does not. It would be possible to design a coprocessor specific to the project architecture, but since the aim of  $\mu RISCV$  is educational, the idea has been discarded. Some of the registers of the MIPS processor supported the TLB handling, so those are the only ones that have to be ported in the new project. RISC-V architecture provides additional registers for custom purposes that have been used to cover the missing coprocessor (see section 2.1.3).

#### 2.1.3 Control and Status Register (CSR)

The Control and Status Registers (CSR) are registers that store CPU data. RISC-V defines 4096 CSRs. A few of them are allocated by RISC-V [33], whilst the others are designed for custom purposes.

#### 2 Implementation

The relevant CSRs used in  $\mu$ RISCV are:

- *time*: real-time counter;

- *mtvec*: trap handler address (see section 2.2);

- *mepc*: address to return after an exception is handled;

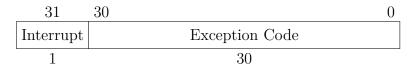

- *mcause*: code indicating the event that caused the trap (see fig. 2.1);

- *mstatus*: keeps track of current processor state (see fig. 2.2);

- *mie*: interrupt enabled bits (see fig. 2.6);

- *mip*: interrupt pending bits (see fig. 2.7);

Figure 2.1: Machine cause register layout [33] (only relevant bits are named)

| 31 13 | 12 11    | $10 \ 8$ | 7    | 6 | 5 | 4 | 3   | 2 | 1 | 0 |

|-------|----------|----------|------|---|---|---|-----|---|---|---|

| 0     | MPP[1:0] |          | MPIE | 0 | 0 | 0 | MIE | 0 | 0 | 0 |

| 19    | 2        | 3        | 1    | 1 | 1 | 1 | 1   | 1 | 1 | 1 |

Figure 2.2: Machine status register layout [33] (only relevant bits are named)

Since there are no registers dedicated to the TLB, some from the custom CSRs area have been selected (see fig. 2.3). The names and semantics of these registers are inherited from the TLB handling of  $\mu$ MPS3 to keep compatibility with previous projects.

| Macro          | Value | Description                       |  |  |  |  |  |

|----------------|-------|-----------------------------------|--|--|--|--|--|

| ENTRYLO        | 0x800 | Higher part of a TLB entry        |  |  |  |  |  |

| ENTRYHI        | 0x801 | Lower part of a TLB entry         |  |  |  |  |  |

| INDEX          | 0x802 | Index of the TLB table            |  |  |  |  |  |

| RANDOM         | 0x803 | Random index of the TLB table     |  |  |  |  |  |

| BADVADDR 0x804 |       | Virtual address that generated an |  |  |  |  |  |

|                |       | error                             |  |  |  |  |  |

Figure 2.3: Custom CSRs

# 2.2 Exception Handling

Exceptions are events that change the normal execution flow of the instruction currently processed by the machine. There are two main types of exceptions: *interrupts* and *exceptions*. From the point of view of the hardware, the latter can be again divided into two categories: *User TLB exceptions* and *all the other ones*. The handling proposed in the RISC-V manual is quite different compared to the MIPS one. The RISC-V specs provide a list of interrupts and exceptions that a machine should handle (see fig. 2.4).

| Interrupt | Exception code | Description                     |

|-----------|----------------|---------------------------------|

| 1         | 3              | Machine software interrupt (In- |

|           |                | terval Timer)                   |

| 1         | 7              | Machine timer interrupt (CPU    |

|           |                | Timer)                          |

| 1         | $\geq 16$      | Designed for platform use (De-  |

|           |                | vices)                          |

| 0         | 0              | Instruction address misaligned  |

| 0         | 1              | Instruction access fault        |

| 0         | 2              | Illegal instruction             |

| 0         | 3              | Breakpoint                      |

| 0         | 4              | Load address misaligned         |

| 0         | 5              | Load access fault               |

| 0         | 6              | Store address misaligned        |

| 0         | 7              | Store access fault              |

| 0         | 8              | Environment call from U-mode    |

| 0         | 11             | Environment call from M-mode    |

| 0         | 12             | Instruction page fault          |

| 0         | 13             | Load page fault                 |

| 0         | 15             | Store page fault                |

| 0         | 24-31,48-63    | Designed for custom use         |

Figure 2.4: Machine cause register (mcause see fig. 2.1) values after trap (see Table 3.6 in [33])

There are no predefined codes for handling TLB exceptions. Consequently, a portion of the *Designed for custom use* area has been used (see fig. 2.5) for this purpose.

| Interrupt | Exception code | Description          |

|-----------|----------------|----------------------|

| 0         | 24             | TLB mod              |

| 0         | 25             | TLB load fault       |

| 0         | 26             | TLB store fault      |

| 0         | 27             | User TLB load fault  |

| 0         | 28             | User TLB store fault |

Figure 2.5: Custom exceptions to handle TLB events

mtvec is a special register that defines how the machine should retrieve the correct subroutine to handle a specific event. This register has two fields: *BASE* (30-bit) and *MODE* (first 2-bit). Where *BASE* indicates the base address of the subroutine, *MODE* specifies how the processor must interpret the *BASE* field. There are two possible values for mode:  $\theta$  (direct mode) or 1 (vectorized mode). This project aims to let students develop their small kernel in a highlevel language (e.g. C). Using the vectorized mode would mean introducing another layer represented by the assembly code to handle the various exceptions. So to maintain the logic of the processor simple,  $\mu$ RISCV implements the direct mode. Since the *mtvec* in the direct mode stores only one address, the procedure to determine whether the TLB-Refill or general exception handlers should be called, is now incorporated in the BIOS (see section 2.3).

#### 2.2.1 PROCESSOR BEHAVIOUR

An interrupt breaks the normal flow of the machine, so when raised the processor state (i.e. registers) must be saved to continue the stopped execution after such an interrupt has been handled. The routine to handle exceptions/interrupts has not changed apart from the processor state field that has been modified (see section 2.1.1). Indeed since the *cause* register, replaced with

#### 2 Implementation

the CSR register *mcause* (see fig. 2.1), no more holds the information about which interrupts are enabled, a new CSR register, *mie* (see fig. 2.6), has been introduced to achieve that. In addition, a new CSR register, called *mip* (see fig. 2.7), holds the pending bits of all interrupts. Interrupt cause number i (see fig. 2.1, fig. 2.8) corresponds to the *i*-th bit in both *mip* and *mie*.

| 15 | <br>     | 10 | 0 | 0 | 7    | 0 | 0 | - | 0    | _ | - | 0 |

|----|----------|----|---|---|------|---|---|---|------|---|---|---|

|    | <br>MEIE | 0  | 0 | 0 | MTIE | 0 | 0 | 0 | MSIE | 0 | 0 | 0 |

| 4  | 1        | 1  | 1 | 1 | 1    | 1 | 1 | 1 | 1    | 1 | 1 | 1 |

Figure 2.6: Interrupt enable bits (mie 0:15) layout [33]

| 15 1 |      | 10 | 0 | <u> </u> | 7    | 0 | 0 | - |      | _ | <u> </u> |   |

|------|------|----|---|----------|------|---|---|---|------|---|----------|---|

|      | MEIP | 0  | 0 | 0        | MTIP | 0 | 0 | 0 | MSIP | 0 | 0        | 0 |

| 4    | 1    | 1  | 1 | 1        | 1    | 1 | 1 | 1 | 1    | 1 | 1        | 1 |

Figure 2.7: Interrupt pending bits (mip 0:15) layout [33]

The full procedure is similar to the one described in [13] but slightly modified:

- 1. Load the Exception PC (EPC) CSR register with the current PC value;

- 2. Set the exception cause code in *mstatus* (see fig. 2.1, fig. 2.2, fig. 2.4)

- 3. Copy the value of the *mie* bit in *mstatus* CSR register into the *mpie* bit of *mstatus*, then reset the *mie* bit;

- 4. Copy the current machine mode into the *mpp* field of *mstatus*, then set the current machine mode to *Machine* (0x3) [33];

- 5. Load the PC with the value of the mtvec CSR register (see section 2.2).

Then whenever a *mret* instruction [33] is executed, the complementary operations are performed: the *mie* bit of *mstatus* is set to the value of *mpie* bit, and the current mode is set to the value of the *mpp* field of *mstatus*.

| Interrupt Line | Description               |

|----------------|---------------------------|

| 16             | Inter Processor Interrupt |

| 17             | Disk Device               |

| 18             | Flash Device              |

| 19             | Ethernet Device           |

| 20             | Printer Device            |

| 21             | Terminal Device           |

Figure 2.8: Custom interrupt lines

# 2.3 BIOS

The BIOS ROM code provides low-level services such as:

- Bootstrap function: then BIOS routine is the first code executed when  $\mu$ RISCV is turned on;

- *TLB-Refill* handler: routine invoked whenever a TLB-Refill event occurs;

- *Exceptions* handler: routine invoked whenever an exception occurs;

- *Library* services: wrapper function to access/modify CPU registers and to manage the TLB table;

# 2.3.1 BOOTSTRAP