Alma Mater Studiorum  $\cdot$  University of Bologna

School of Science Department of Physics and Astronomy Master Degree in Physics

# FPGA-based hardware demonstrator of a Hough Transform pattern recognition algorithm for the ATLAS Phase-II trigger upgrade

Supervisor:

Prof. Alessandro Gabrielli

**Co-supervisor:**

Dr. Fabrizio Alfonsi

Submitted by: Alice Santarelli

Academic Year 2020/2021

Those who can imagine anything, can create the impossible. (Alan Turing)

# Abstract

The advent of the High-Luminosity (HL) phase of the Large Hadron Collider (LHC) at CERN will contribute to study, with a significantly improved sensitivity, known mechanisms expected by the theory of the Standard Model and new rarer processes which can be the sign of physic Beyond Standard Model. In fact, in this new operational phase the increase of the luminosity will allow to produce the demanded larger datasets of proton-proton collisions. The LHC complex is planned to deliver in 2027 a luminosity up to  $7.5 \times 10^{34} \ cm^{-2} s^{-1}$ , corresponding to  $\mu = 200$  of events per bunch crossing, with the ultimate goal to provide an integrated luminosity of up to  $3000/4000 \ fb^{-1}$ . To come up with these new conditions, the detectors placed in the four interaction points of LHC require an upgrade. In particular, the higher number of signals produced inside the detectors would eventually make the trigger and readout electronics currently in use in these experiments obsolete and, for this reason, new strategies for data acquisition and processing will be necessary. This Master Thesis discusses the Phase-II upgrade of the Trigger and Data Acquisition system of the detector called A Toroidal LHC ApparatuS (ATLAS). An R&D program, which has included the creation of two task forces, was launched in the 2021 Spring with the aim to produce one engineered solution for the track reconstruction at the Event Filter (EF) level. The Electronic group of the University of Bologna is taking part in the proposal of the heterogeneous commodity task force, which consists of the previous project called Hardware Tracking for the Trigger. The heterogeneous solution is based on a mixed commodity platform of classic processors and accelerators, where track reconstruction is expected to be performed via the use of mathematical functions, for example through the implementation of Hough Transform algorithm on the FPGA which will be part of the EF of ATLAS Phase-II. The R&D

activities performed until now include the development of the firmware for the HT. Final goal of this Master Thesis is the creation of a hardware demonstrator able to test the ongoing firmware design. To fulfill this purpose, a new firmware architecture is exploited and it relies on a manageable Peripheral Component Interconnect Express transmission. The integration of the two firmware designs is realized with the development of a two first-in-first-out structure. In this way it is demonstrated the correct implementation of the ongoing Hough Transform firmware design.

# Contents

| Introduction i |          |        |                                                                                                           |    |  |  |  |  |  |

|----------------|----------|--------|-----------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

| Co             | Contents |        |                                                                                                           |    |  |  |  |  |  |

| 1              | CEI      | RN and | d LHC                                                                                                     | 1  |  |  |  |  |  |

|                | 1.1      | Struct | ure of LHC                                                                                                | 1  |  |  |  |  |  |

|                |          | 1.1.1  | LHC parameters                                                                                            | 5  |  |  |  |  |  |

|                | 1.2      | LHC s  | chedule                                                                                                   | 6  |  |  |  |  |  |

| <b>2</b>       | ATI      |        |                                                                                                           | 10 |  |  |  |  |  |

|                | 2.1      | Coordi | inate system                                                                                              | 10 |  |  |  |  |  |

|                | 2.2      | Detect | for composition $\ldots$ | 12 |  |  |  |  |  |

|                |          | 2.2.1  | Inner Detector                                                                                            | 13 |  |  |  |  |  |

|                |          | 2.2.2  | Calorimeters                                                                                              | 16 |  |  |  |  |  |

|                |          | 2.2.3  | Muon Spectrometer                                                                                         | 18 |  |  |  |  |  |

|                |          | 2.2.4  | Magnetic System                                                                                           | 20 |  |  |  |  |  |

|                |          | 2.2.5  | Forward detectors                                                                                         | 21 |  |  |  |  |  |

|                | 2.3      | Trigge | r and Data Acquisition system                                                                             | 22 |  |  |  |  |  |

| 3              | ATI      | LAS P  | hase-II upgrade                                                                                           | 26 |  |  |  |  |  |

|                | 3.1      | Upgra  | de proposals                                                                                              | 26 |  |  |  |  |  |

|                |          | 3.1.1  | Inner Tracker                                                                                             | 28 |  |  |  |  |  |

|                |          | 3.1.2  | High Granularity Timing Detector                                                                          | 29 |  |  |  |  |  |

|                |          | 3.1.3  | Calorimeter                                                                                               | 30 |  |  |  |  |  |

|              |     | 3.1.4   | Muon Spectrometer                 | 31 |

|--------------|-----|---------|-----------------------------------|----|

|              | 3.2 | Trigger | r and the Data Acquisition        | 33 |

|              |     | 3.2.1   | Baseline Architecture             | 35 |

|              |     | 3.2.2   | Evolved Architecture              | 38 |

|              |     | 3.2.3   | Hardware Tracking for the Trigger | 40 |

|              |     | 3.2.4   | A new baseline                    | 46 |

| 4            | Hou | igh Tra | ansform for tracking              | 49 |

|              | 4.1 | TDAQ    | overview                          | 49 |

|              |     | 4.1.1   | Commodity accelerators            | 51 |

|              | 4.2 | System  | a overview and functional blocks  | 51 |

|              | 4.3 | Hough   | transform for particle tracking   | 53 |

|              |     | 4.3.1   | Hough transform for circles       | 54 |

|              |     | 4.3.2   | Implementation of the HT $\ldots$ | 57 |

|              |     | 4.3.3   | The accumulator                   | 58 |

| <b>5</b>     | Den | nonstra | ator development for HT algorithm | 64 |

|              | 5.1 | Hardw   | are framework of Bologna          | 64 |

|              |     | 5.1.1   | Hardware HT algorithm             | 66 |

|              | 5.2 | Hardw   | are device for data transmission  | 68 |

|              |     | 5.2.1   | Experimental Set-up               | 70 |

|              |     | 5.2.2   | Data transmission through PCIe    | 71 |

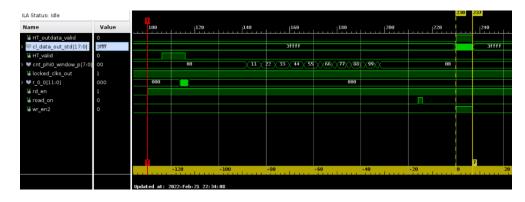

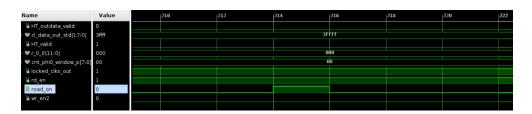

|              | 5.3 | Prelim  | inary tests                       | 74 |

|              |     | 5.3.1   | PCIe FIFOs                        | 74 |

|              |     | 5.3.2   | FIRST and SECOND FIFOs            | 75 |

|              |     | 5.3.3   | Bits mapping                      | 75 |

|              | 5.4 | Final t | cests                             | 79 |

| A            | FPG | ĞΑ      |                                   | 89 |

| в            | PCI | e       |                                   | 93 |

| $\mathbf{C}$ | FIF | 0       |                                   | 96 |

|              |     |         |                                   |    |

# Chapter 1

# CERN and LHC

CERN, from the French acronym "Conseil Européen pour la Recherche Nucléaire", or European Council for Nuclear Research, was founded in 1952 with the aim of establishing a fundamental physics research organization in Europe. The laboratory sits astride the Franco-Swiss border near Geneva and nowadays physicists and engineers from around the world are probing the fundamental structure of the universe using the world's largest and most complex scientific instruments that are pushing the limits of technology.

## 1.1 Structure of LHC

The Large Hadron Collider (LHC) project started with the aim to design a high energy physics collider able to deliver a center of mass energy higher than the Large Electron-Positron (LEP) and Tevatron. The purpose was to investigate the nature of electroweak symmetry breaking and the search for physics beyond the Standard Model at the TeV scale. The realization of this particle accelerator was approved by CERN Council in December 1994 [1] and obtains important achievements during years of running, one of the most important was the discovery of the Higgs boson in 2012 [2] whose properties are under continuous study in order to confirm the Standard Model predictions and to search for new physics phenomena.

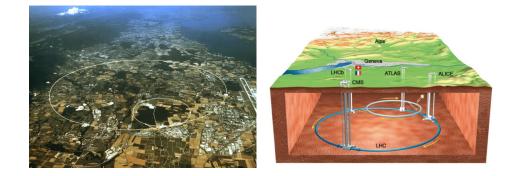

LHC is placed 100 m underground, near Geneva (Fig. 1.1), in the tunnel floor of the old LEP Collider. It consists of a 27.6 km ring of superconducting magnets with

Figure 1.1: The LHC underground position in the French-Swiss border[3][4].

a number of accelerating structures to boost the energy of the particles along the way. Differently from the previous particle-antiparticle colliders, in which both beams share the same phase space in a single ring, the LHC machine is based on a proton-proton (pp) collision. The two counter-rotating proton beams are currently accelerated to a center of mass energy of  $\sqrt{s} = 13$  TeV, value that in the next Run upgrade will be increased to 14 TeV. The LHC will also collide heavy ions (A), in particular lead nuclei, at 5.5 TeV per nucleon pair.

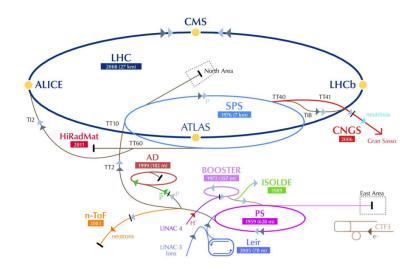

In order to reach these energies, the beam has to approach several steps of acceleration as it is illustrated in Fig. 1.2.

Protons are produced stripping electrons from small  $H_2$  silos and subsequently they go inside Linac2 where their energy is raised to 50 MeV. The circular Booster (PSB) accelerates them to 1.4 GeV and in the Proton Synchrotron (PS) they reach 25 GeV. The Super Proton Synchrotron (SPS) follows, here they acquire an energy of 450 GeV. In the final step protons are transferred to the LHC where each beam is accelerated to 6.5 TeV. For the heavy ions [5], instead, a linear accelerator called Linac3 takes the lead ions at an energy of 4.5 MeV/n and a Low Energy Ion Ring (LIER) accelerates them to 72 MeV/n. Then they enter the SPS and follow the same path as protons before entering LHC, reaching an initial energy of 5.9 GeV/n and then of 177 GeV/n. In the last ride, LHC accelerates lead ions at 1.38 TeV/n. The acceleration of the charged particles is fulfilled by a set of Radio Frequency (RF) cavities, whose task is to compensate for the synchrotron energy loss. This is a phenomenon that happens when a charged particle is accelerated in a circular collider, generating an electromagnetic radiation emission and it

Figure 1.2: The CERN accelerator system.

should be avoided as much as possible because it induces a relevant loss of energy. The RF cavities focus the packets of protons (bunches) along the beam-pipe. The proton beams are kept in circular track by a set of 1232 superconducting dipole magnets made with copper-clad niobium-titanium cables. The superconductivity is mandatory to reach the magnetic field necessary to achieve the energy required in the center-of-mass of the collision. On the other hand, to focus the protons perpendicularly to the beam pipe it is used a set of 858 quadrupole magnets that are placed one next to another and perpendicularly with respect to the poles. Furthermore, other multi-pole magnets are used all over the LHC. In order to sustain the two-ring architecture of LHC, twin bore magnets consisting of two sets of coils are used. The system requires a low temperature of 2 K and this can be realized through the use of liquid Helium.

Proton beams can circulate for many hours inside the LHC under normal operating conditions. Differently from the LEP collider, which had eight crossing points, LHC has four interaction points in which are placed four experiments that, between 1996 and 1998, received official approvals for their construction. Currently active at LHC, each one of these four experiments have different physics goals:

• ATLAS (A Toroidal LHC ApparatuS) [6] is a multi-purpose experiment built for probing pp (and lead-lead) collisions. This thesis work is related to this detector and, for this reason, a more detailed description will be provided in the next chapters.

- CMS (Compact Muon Solenoid) [7] is a multi-purpose experiment that was conceived, similarly to ATLAS, to study pp (and lead-lead) collisions. It is 21 m long, 15 m in diameter, with a weight of about 14,000 t. Although CMS has the same scientific goals as the ATLAS experiment, it uses different technical solutions and a different magnet-system design. Indeed the detector is built around a huge solenoid magnet that generates a field of 4 T. This structure surrounds an all-silicon pixel and strip tracker, a lead-tungstate scintillating-crystals electromagnetic calorimeter and a brass-scintillator sampling hadron calorimeter. The iron yoke of the flux-return is equipped with four stations of muon detectors covering most of the 4π solid angle.

- LHCb (LHC-beauty) [8] is a specific apparatus for pp collisions. It is dedicated to precision measurements of CP violation and rare decays of B hadrons. Instead of surrounding the entire collision point with an enclosed detector, such as in ATLAS and CMS, the LHCb experiment uses a series of subdetectors to detect mainly particles thrown forwards by the collision in one direction. The first subdetector is mounted close to the collision point, with the others following one behind the other, over a length of 20 m. Starting from the interaction point, are placed in order: a tracker, a ring imaging Cherenkov detector (RICH), other trackers, another RICH, an electromagnetic calorimeter, an hadronic calorimeter and a muon detector;

- ALICE (A Large Ion Collider Experiment) [9] is a general-purpose, heavy-ion detector which investigate the strong-interaction sector of the Standard Model, the QCD. With a weight of 10,000 t, the detector is 26 m long, 16 m high, and 16 m wide. It is designed to study strongly interacting matter and the quark-gluon plasma at extreme values of energy density and temperature in nucleus-nucleus collisions. The physics programme of this experiment does not only include lead ions and protons running, but also lighter ions collisions, lower energy running and dedicated proton-nucleus runs. It is composed of 18 detectors surrounding the collision point that includes a time projection chamber (TPC), a transition radiation chamber, a "time of flight" detector, electromagnetic and hadronic calorimeters and

a muon spectrometer.

### 1.1.1 LHC parameters

The protons, after all the pre-LHC chain, reach an energy of 450 GeV/n and are injected in packets (bunches) into LHC. Each bunch contains  $\approx 1.2 \times 10^{11}$  protons and is  $\sim 7.55$  cm long and 16.7  $\mu$ m squeezed radially. The final beam consists of 2808 bunches of protons. Two of them collide at the same energy, speed and direction and opposite verse. The number of collisions between protons per bunch-crossing (pileup) must be as high as possible ( $\mu \sim 15-50$  along Run 1 and 2, and  $\mu \sim 150-200$  targeted for High Luminosity LHC, presented in the next Section 1.2). The focusing inside the LHC also increases the number of collisions. Every 25 ns there is a collision and this is an important parameter since this implies that, consequently, all the detectors at LHC need to conform to the 40 MHz collider frequency. The energy reached at the collision center-of-mass by the proton in the acceleration chain can be calculated with the relativistic formulation, with the Lorents factor of 7460. LHC has been designed to reach an instantaneous luminosity with a peak of  $10^{34} \ cm^{-2} \ s^{-1}$  (for lead nuclei  $10^{27} \ cm^{-2} \ s^{-1}$ ) and a center of mass energy of 14 TeV (5.5 Tev for lead nuclei). The instantaneous luminosity expresses the collider performance, as well as the capability of the apparatus to generate physics events, based on the energy and density of the particles. It is defined as:

$$\mathcal{L} = f \frac{n_1 \cdot n_2}{4\pi \cdot \sigma_x \cdot \sigma_y} F \tag{1.1}$$

where  $n_i$  is the number of particles in the accelerator, f is the revolution frequency of the bunches and  $\sigma_x, \sigma_y$  is related to the transverse dimensions of the beam. The 1.1 can also be expressed in terms of the number of bunches inside the ring  $(n_b)$ , the number of particles per bunch  $(N_b)$ , the revolution frequency of the bunches in the accelerator  $(f_{rev}, \text{ that is } 11.2 \text{ kHz})$ , the relativistic Lorentz factor  $(\gamma_r)$ , the normalized transverse beam emittance  $(\epsilon_n, \text{ that is } 3.75 \ \mu\text{m})$ , the beta function of the collision point  $(\beta^*, \text{ that}$ is 0.55 m) and the geometric luminosity reduction factor, due to the crossing angle of the two beams at the interaction point (F):

$$\mathcal{L} = \frac{1}{\sigma} \frac{dN}{dt} = \frac{N_b^2 \cdot n_b \cdot f_{rev} \cdot \gamma_r}{4\pi \cdot \epsilon_r \cdot \beta^*} F$$

(1.2)

The Inegrated luminosity can be in this way calculated,

$$L = \int_{\Delta t} \mathcal{L} \cdot dt \tag{1.3}$$

and, together with the cross section, gives the total number of events in a Run:  $N_e = L \cdot \sigma_e$ .

## 1.2 LHC schedule

The scientific program of the LHC, summarized in Fig. 1.3, spans over many years of operation and includes an ambitious series of future upgrades. In the first period of operation (Run1) the instantaneous luminosity reached was  $7.7 \times 10^{33} \ cm^{-2} s^{-1}$  and the center of mass energy spanned in a range from 900 GeV up to 8 TeV.

Figure 1.3: Timetable for the future years of LHC in terms of different phases. Runs are the working periods of the collider including data taking by the experiments, while Long Shutdowns represents the stop periods due to upgrades required by the accelerator and detectors.

#### 1.2 LHC schedule

The bunch crossing time was 50 ns, double compared to the design specifications. Energy and  $\mathcal{L}$  were very promising at that time: over half of the target features. With these parameters the Higgs boson was observed in 2012 and, at the beginning of 2013, Run 1 concluded. The Long Shut-down 1 (LS1) followed between 2013 and 2014, where machine elements were consolidated. The magnet splices were repaired and the collimation scheme was upgraded in order to achieve the design beam energy and luminosity. Since 3 June 2015 the LHC has operated in Run 2 at center of mass energy of 13 TeV and has progressively reached the luminosity of  $\mathcal{L} = 1 \times 10^{34} \ cm^{-2} \ s^{-1}$  on 26 June 2016. Despite the reduced number of bunches (about 2200 cf. 2800 nominal), it was obtained a peak luminosity up to  $1.2 \times 10^{34} \ cm^{-2} \ s^{-1}$  through the reduced emittance from the injectors and a  $\beta^*$  value of 40 cm (cf. 55 cm nominal value) at the high luminosity

Despite the reduced number of bunches (about 2200 cf. 2800 nominal), it was obtained a peak luminosity up to  $1.2 \times 10^{34} \ cm^{-2} \ s^{-1}$  through the reduced emittance from the injectors and a  $\beta^*$  value of 40 cm (cf. 55 cm nominal value) at the high luminosity interaction points. Total integrated luminosity was of about 35  $fb^{-1}$ . The Run 2 proton physics ended marking the conclusion of an extremely successful data taking period. Approaching the year 2024, the LHC will hopefully further increase the peak luminosity. During the Long Shutdown 2 (LS2), between 2019 and 2020, the Linac4 was connected into the injector complex and with the injection beam energy of the Proton Synchrotron Booster. Moreover, new cryogenics plants will be subsequently installed to separate the cooling of the superconducting radio frequency modules and the magnet cooling circuit. From 2022, during Run 3, the LHC design parameters should allow for an ultimate peak instantaneous luminosity of  $L \sim 2.2 \times 10^{34} \ cm^{-2} \ s^{-1}$  (Phase-I operation) and for delivering an integrated luminosity of ~ 300  $fb^{-1}$ . The end of this run is scheduled for 2024 and the expectation is that the statistical gain, in running the accelerator without a significant luminosity increase beyond its design and ultimate values, will become marginal.

The LHC ring comes with the major results reached during years of operation such as the discovery of the Higgs boson or the high precision measurements of the physics at the electroweak scale. As a consequence, stronger confidence of the LHC potential arises with the aim to realize a major luminosity upgrade that was approved in Brussels on 30 May 2013: 'Europe's top priority should be the exploitation of the full potential of the LHC, including the high luminosity upgrade of the machine and detectors with a view to collecting ten times more data than in the initial design, by around 2030'

to 4000 after a period of about 12 years.

[10]. The running time necessary to have the statistical error of a given measurement after 2020 will be more than ten years. Therefore, to maintain scientific progress and to exploit its full capacity, the LHC will need a decisive increase of its luminosity after 2020. In the Long Shutdown 3 (LS3), from 2024 to 2026, the LHC will undergo a major upgrade of its components, like low- $\beta$  quadrupole triplets and the use of crab cavities at the interaction regions. After the LS3 the Phase-II will begin and it regards the High Luminosity LHC (HL-LHC), called in this way since its instantaneous luminosity will significantly increase. Main motivations for a high luminosity regime consist in the need for significantly large data sets, that would offer the possibility to improve the sensitivity of actual measurements and perform completely new ones. In the first proposals the nominal levelled instantaneous luminosity should have reached a value of  $L = 5 \times 10^{34} \ cm^{-2} \ s^{-1}$ , corresponding to an average of roughly  $\langle \mu \rangle = 140$  inelastic proton-proton collisions per beam crossing (pileup). Later, a new scenario with an ultimate levelled luminosity was introduced, with a peak up to  $L \sim 7.5 \times 10^{34} \ cm^{-2} \ s^{-1}$ , corresponding to  $\mu = 200$ , delivering an accumulated integrated luminosity of around 3000  $fb^{-1}$  per year of operation. Data collected by HL-LHC run therefore, would be an order of magnitude more than previously. HL-LHC was expected to be active for the operations in the second half of 2026, but because of some delays the timetable has been slightly postponed. The final goal is to provide an ultimate integrated luminosity of up

# Chapter 2

# ATLAS

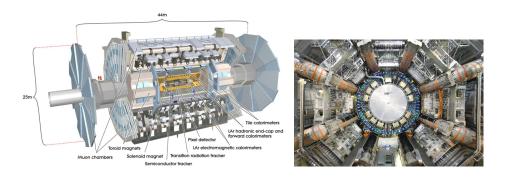

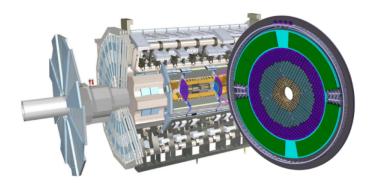

ATLAS [11] is a multi-purpose experiment where over 3000 physicists from over 175 institutes collaborate. It rises in the so-called Point 1 at CERN, 100 m underground, and has a forward-backward symmetric cylindrical geometry with a nearly  $4\pi$  coverage in solid angle. The dimensions of the detector are 25 m in height and 44 m in length and its overall weight is approximately 7000 t. ATLAS studies proton-proton and heavy-ion collisions at the LHC. This chapter introduces the architecture of the detector.

## 2.1 Coordinate system

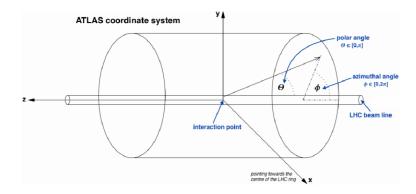

The ATLAS detector and the particles emerging from the pp collisions are described using the coordinate system illustrated in this section.

As it is shown in Fig. 2.1, the nominal interaction point (IP) is defined as the origin of the coordinate system in a 3D Cartesian frame of reference, with coordinates (x, y, z). The z-axis defines the beam direction while the x-y plane is transverse to the beam direction. In particular, the positive x-axis points the centre of the LHC ring and the positive y-axis points upwards. In addition, the positive z-axis defines the side-A of the detector, while the negative z-axis the side-C. The transverse plane can be also described with the  $r - \phi$  coordinates. The azimuthal angle  $\phi$  is measured from the positive x-axis, while the polar angle  $\theta$  is the angle from the positive z-axis, along the detector. The radial coordinate r, describes the distance from the beam. In general, instead of  $\theta$  it is

Figure 2.1: Common coordinate system used in the ATLAS experiment.

used the pseudorapidity, a function of the angular position of the particle, not taking into account its nature and energy:

$$\eta = -\ln \tan(\frac{\theta}{2}). \tag{2.1}$$

The pseudorapidity ranges from 0, alongside the y-axis, to infinity, alongside the zaxis. However, considering massive objects such as jets, it is used the rapidity, which is Lorentz-invariant for transformations along the z-axis and is defined as:

$$y = \frac{1}{2} ln[\frac{E+p_l}{E-p_l}].$$

(2.2)

where  $p_l$  is the particle linear momentum. The transverse momentum  $p_T$ , the transverse energy  $E_T$  and the missing transverse energy  $E_T^{miss}$ , are defined in the x-y plane unless stated otherwise. Based on these considerations, it is possible to measure the angular distance between two particles in the pseudorapidity-azimuthal angle space:

$$\Delta R = \sqrt{\Delta \eta^2 + \Delta \phi^2}.$$

(2.3)

The importance of this new coordinates system  $(\eta, \phi, z)$  is that it is Lorentz invariant under boosts along the z-axis.

| Detector component   | Required resolution                          | $\eta$ coverage        |  |

|----------------------|----------------------------------------------|------------------------|--|

|                      |                                              | Measurements (Trigger) |  |

| Tracking             | $\sigma_{p_T}/p_T = 0.05\% p_T \oplus 1\%$   | $\pm 2.5$              |  |

| EM calorimeter       | $\sigma_E/E = 10\%\sqrt{E} \oplus 0.7\%$     | $\pm 3.2 \ (\pm 2.5)$  |  |

| Hadronic calorimeter |                                              |                        |  |

| barrel and end-cap   | $\sigma_E/E = 50\%\sqrt{E} \oplus 3\%$       | $\pm 3.2 \ (\pm 3.2)$  |  |

| forward              | $\sigma_E/E = 100\%\sqrt{E} \oplus 10\%$     | $3.1 <  \eta  < 4.9$   |  |

|                      |                                              | $(3.1 <  \eta  < 4.9)$ |  |

| Muon spectrometer    | $\sigma_{p_T}/p_T = 10\%$ at $p_T = 1 \ TeV$ | $\pm 2.7 \ (\pm 2.4)$  |  |

Table 2.1: General performance goals of the ATLAS detector. Units for E and  $p_T$  are in GeV. The muon-spectrometer performance is independent of the inner-detector system for high  $p_T$ .

# 2.2 Detector composition

ATLAS structure is composed of different detectors, where each one of them covers a pseudorapidity  $(\eta)$  range and has a specific purpose. The overall ATLAS detector layout is shown in Fig. 2.2 and its main performance goals are listed in Tab.2.1.

The ATLAS inner tracking detector (ID) is the first detector which the produced particles traverse after the pp interaction. All this tracking system is surrounded by a thin superconducting solenoid, which provides a magnetic field of 2 T that allows it to perform momentum measurements. The magnet configuration has driven the design

Figure 2.2: Composition of the ATLAS experiment detector with a recent image.

of the rest of the detector. It comprises three large superconducting toroid magnets (one in the barrel and two in the end-caps) that are arranged with an 8-fold azimuthal symmetry around the other two ATLAS detectors: the calorimeters. As the radial distance increases, the electromagnetic calorimeter is the first and its goal is to measure energy and the track of electrons, positrons and photons. However, all these detectors cannot measure the more energetic particles, the hadrons, and for this reason there is also the hadronic calorimeter which measures their energy. Eventually, only the particles with a very low cross section survive, mainly muons and neutrinos. The former can be detected in the muon spectrometer while the latter cannot be detected directly by ATLAS, thus they are studied with the missing energy technique.

### 2.2.1 Inner Detector

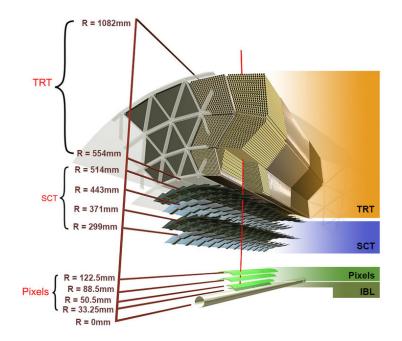

The Inner Detector [12] is the closest to the beam line, hence its technology must be very resistant to radiation. This apparatus is 6.2 m long with a diameter of 2.1 m and its pseudorapidity range coverage is  $|\eta| < 2.5$ . ID was built for the early tracking stage of ATLAS and it is composed of: the Pixel Detector (PD) [13], the Semiconductor Tracking (SCT) [14] and the Transition Radiation Tracker (TRT) [15]. During 2014 a new detector, the Insertable Barrel Layer (IBL) [16], was added. The ATLAS ID, including the IBL detector and its envelope, is shown in Fig. 2.3 with also the 3-dimensional structure of the IBL detector with its services. In Tab. 2.2 are listed the general characteristics of every sub-components.

The task of all these detectors is to provide a high precision measurement of the track of the particles and this can be performed through the inside-out and the outsidein algorithms. The first one uses three seeds in the silicon detectors (PPD and SCT) in order to reconstruct the track of charged particles coming from primary interactions. To do this, a combinatorial Kalman-filter algorithm adds the following hits. In the outside-in algorithm, instead, the reconstruction of the track of secondary particles is done starting from the hits in the TRD. Silicon hits, if present, are added with the combinatorial Kalman-filter algorithm. The efficiency of track reconstruction is measured by simulated events, and it varies as a function of  $p_T$  and  $\eta$ .

Figure 2.3: Section of the Pixel Detector with the distances of the sub-detectors and layers from the LHC beam pipe[19]

#### The Pixel Detector

The Pixel Detector (PD) is a silicon based detector which uses the pixel technology. PD has the highest granularity in all ATLAS and it consists of three disks (for each side of the interaction region) and four barrels layers: Insertable B-Layer, B-Layer, Layer1, Layer 2. The Insertable B-Layer (IBL) [20] is a new innermost tracking detector that was installed during the LS1 between the B-Layer and a new smaller radius beam pipe. This is the latest upgrade of the pixel detector. The layer was added with the intention to maintain the full ID tracking performances and robustness during the Phase-I operation despite read-out bandwidth limitations of the Pixel layers at the expected peak luminosity and the accumulated radiation damage to the silicon sensors and frontend electronics. The IBL is designed to operate until the end of Phase-I, when a full tracker upgrade is planned for HL-LHC operation. It consists of 14 carbon composite staves, providing full azimuthal ( $\phi$ ) hermeticity for high transverse momentum ( $p_T > 1$ GeV) particles and longitudinal coverage up to  $|\eta| = 3$ . Each stave supports 20 pixel

| Detector                                          | Hits tracks | Elements size             | Hits Resolution $(\mu m)$ |

|---------------------------------------------------|-------------|---------------------------|---------------------------|

| PD, $ \eta  < 2.5$                                |             |                           |                           |

| 4 barrel layers                                   | 3           | $50 \times 400 \ \mu m^2$ | $10(R-\phi) - 115(z)$     |

| $3\times 2$ lateral disks                         | 3           | $50 \times 400 \ \mu m^2$ | $10(R-\phi) - 115(z)$     |

| SCT, $ \eta  < 2.5$                               |             |                           |                           |

| 4 barrel layers                                   | 8           | $50~\mu m$                | $17(R-\phi) - 580(z)$     |

| $3\times 2$ lateral disks                         | 8           | $50 \ \mu m$              | $17(R-\phi) - 580(z)$     |

| TRD, $ \eta  < 2.0$                               |             |                           |                           |

| 83 barrel tubes                                   | 30          | $d=4\ mm, l=144\ mm$      | 130/straw                 |

| $9\times 2\mathrm{end}\text{-}\mathrm{cap}$ disks | 30          | $d=4mm, l=37\ mm$         | 130/straw                 |

Table 2.2: Main characteristics of the ID's detector.

sensor modules together with their electrical services and a cooling pipe. Every module is constructed from a pixel sensor with pixels of nominal size  $250 \times 50 \ \mu m^2$  electrically bonded to a channel of a read-out chip, the FE-I4B. With the usage of this chip, the new technology of IBL makes the detector itself more radiation hard and with a higher surface coverage.

### The Semi-Conductor Tracker

The Semi-Conductor Tracker (SCT) is a 4-layer silicon microstrip detector. Each layer is formed by modules composed by two microstrip detectors bound together and glued with a 40 mrad angle of their planes. This layout is used to obtain a better z-measurement. In the end-cap region the plane of the microstrip detector is perpendicular to the beam line, while in the barrel region is parallel.

#### The Transition Radiation Tracker

The Transition Radiation Tracker (TRT) is the largest track detector of ID and surrounds the previous two. It consists of about  $5 \times 10^4$  straw tubes that are cylindrical, with one positive wire in their inside and the internal wall at negative voltage. In the barrel region the tubes are parallel to the beam line, while in the end-cap region are perpendicular. With an high number of hits, the straws all together contribute to the measurement of the particle momentum. Every straw is filled with a mixture of Xenon (70 %),  $CO_2(27 \%)$ , and  $O_2$  (3 %).

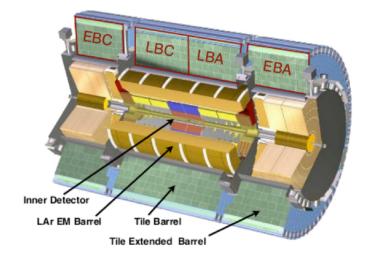

### 2.2.2 Calorimeters

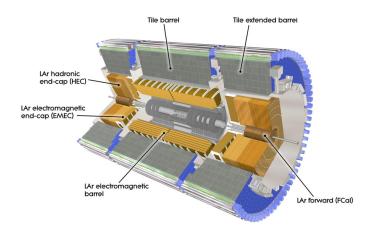

The ATLAS calorimeter system presented in Fig. 2.4 is composed of two sampling calorimeters, electromagnetic and hadronic, that measure the energy of a crossing particle. The entire sub-detector is constituted of different multiple parts, according to the particle type. Each calorimeter consists of four parts: a barrel part, an extended barrel part, an end-cap part and a forward part. The whole system covers a pseudorapidity up to  $\eta = 4.9$  and a complete  $\phi$  coverage.

#### Electromagnetic calorimeter

The electromagnetic sampling calorimeter contains Lead/liquid-argon (LAr). Due to its radiation hardness and its good energy resolution, liquid argon is a good active medium, while the lead is a good absorber. The track and the electromagnetic energy measurements of electrons, positrons, photons and  $\pi^0$  is provided exploiting the electromagnetic showers produced inside it. Since about 99% of the shower energy is emitted at the most in 20  $X_0$ , the EM calorimeter is 22 radiation lengths ( $X_0$ ) deep in the barrel region and more than 24 in the end-caps. The barrel region covers a  $|\eta| < 1.475$  and the end-cap region is composed by two coaxial wheels where the outer covers  $1.375 < |\eta| < 2.5$  and the innermost one covers with  $2.5 < |\eta| < 3.2$ . The region of  $|\eta| < 2.5$  is segmented in three parts, where the first layer is granulated finely in  $\eta$  to achieve a high photon-neutral pion separation. In the barrel region it is possible to discriminate photons and electrons between  $\sim 5 \ GeV$  and  $5 \ TeV$ . The resolution achievable in the barrel and end-cap region is

$$\frac{\sigma_E}{E} = \frac{9.4\%}{\sqrt{E(GeV)}} \oplus 0.1\%. \tag{2.4}$$

In general, in resolution measurements, the first factor describes the stochastic behaviour,

Figure 2.4: Scheme of ATLAS Calorimeter system.

the second one refers to the electronic noise of the read-out channels and the last constant factor regards the temperature, the age of the detector, the radiation damages and others constant contributions. There is a "grey zone" in  $1.37 < |\eta| < 1.52$  not used for precision measurements because of the presence of the barrel-end cap transition zone, where the material reaches  $7X_0$ .

#### Hadronic calorimeter

The energy and the missing momentum of hadrons produced during pp collision or formed from secondary decays can be measured, instead, by the Hadronic Calorimeter (HCAL).

Differently from the other calorimeter, it exploit the strong interaction which occurs when particles travel inside it, developing hadronic showers. It is formed by the Hadronic Tile Calorimeters (HTC), a scintillator-tile calorimeter, by the Hadronic End-Caps Calorimeters (HEC) and the Forward Calorimeter (FCAL) which are both LAr calorimeters. The first one is composed of one central barrel and two smaller extended one at each side of the biggest cylinder. The pseudorapidity is  $|\eta| < 1.7$ . The covered interaction length is respectively 4.0, 1.4, and 1.8. Steel is used as the absorber while scintillating tiles are the active material. The energy resolution is different depending on the calorimeter composition:

$$\frac{\sigma_E}{E} = \frac{10\%}{E} + (1.2 \pm 0.1^{+0.5}_{-0.6}\%) \tag{2.5}$$

in the barrel and in the end-cap region,

$$\frac{\sigma_E}{E} = \frac{10\%}{E} + (2.5 \pm 0.4^{+1}_{-1.5}\%) \tag{2.6}$$

for the forward calorimeter.

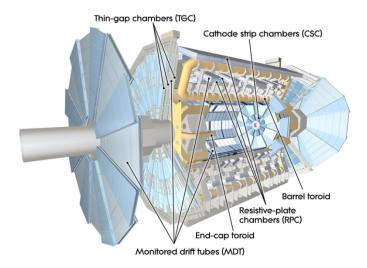

### 2.2.3 Muon Spectrometer

Many physics processes in ATLAS require high  $p_T$  muons signatures and the muon spectrometer schematized in Fig. 2.5 plays an important role in the identification of this particle. The detector is designed to reach high precision and resolution and it also provides an independent muon trigger from the rest of the apparatus. The measurement is based on the magnetic deflection of muon tracks in the large superconducting aircore toroid magnets. The muon spectrometer is divided in barrel and end-cap region, in which toroid magnets are placed. The system is divided in two different groups: Precision Chambers and Trigger Chambers. These sub-detectors are composed by four different detector technologies, the former are composed by Monitored Drift Tubes and Cathode Strip Chambers while the latter by thin Gap Chambers and Resistive Plate Chambers. Muons with an energy lower than the threshold,  $p_T > 3 \ GeV/c$ , cannot be identified because they are completely absorbed before reaching the muon spectrometer. Pseudorapidity range in the whole system is  $|\eta| < 2.7$  and the measured resolution of  $p_T$ is about 20% at 1 TeV.

#### Monitored Drift Tubes and Cathode Strip Chambers

Monitored Drift Tubes (MDT) and Cathode Strip Chambers (CSC) measure the muon momentum. MDT chambers are drift chambers with two multi-layer drift tubes which are focused on precise measurement of the z coordinate in the barrel region. Here pseudorapidity is  $|\eta| < 2$ . Hit position of the particle can be reconstructed measuring

Figure 2.5: Overview of the ATLAS Muon Spectrometer

the drift time in single tubes. CSC are multi-wire chambers with strip cathodes for the measurement of muon momentum in the range of  $1.0 < |\eta| < 2.7$ . The CSC wires are composed of parallel anodes which are perpendicular to 1 mm large strips of opposite polarity. They are placed close to the beam pipe in the innermost layer of the end-cap.

#### Thin Gap Chambers and Resistive Plate Chambers

Thin Gap Chambers (TGC) and Resistive Plate Chambers (RPC) provide the online trigger. TGC in the end-cap region is a very thin multi-wire chamber. The spatial resolution of these detectors is 4 mm in the radial direction and 5 mm in the  $\phi$  coordinate. The anode-cathode spacing is smaller than the anode-anode spacing, leading to a drift time lower than 20 ns. The TGC are also used to improve the measurements along the  $\phi$ coordinate obtained from the precision chambers. RPC in the barrel region are gaseous parallel electrode-plate detectors, with a spatial resolution of 1 mm in two coordinates and a time resolution of 1.0 ns. This sub-detector works in the avalanche regime: when a charged particle passes inside the chamber, the primary ionization electrons are multiplied into avalanches by a high electric field.

Figure 2.6: Overview of the ATLAS magnet system.

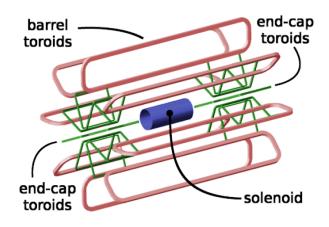

## 2.2.4 Magnetic System

As was already anticipated, momenta measurements of charged particles are done by ATLAS through a system of superconducting magnets. They consist of a Central Solenoid (CS), placed between the ID and the calorimeter system, and three large aircore toroids (one in barrel and two in end-cap), which generate the magnetic field in the muon spectrometer. Fig. 2.6 shows this magnetic system structure. The 2 T magnetic field of the CS points in the positive z-axis direction. It is 5.3 m long, with a diameter of 2.4 m and a weight of 5 t. The operating temperature of 4.5 K is maintained by a cryostat shared with the electromagnetic calorimeter barrel. The barrel toroid consists of 8 flat superconducting race-track coils, 25.3 m long and 5 m wide each. The 8 coils in the torus are kept in position by 16 support rings. Its total weight is 830 t. Toroids magnet produce a magnetic field of 3.9 T and are cooled down to 4.7 K by the liquid helium. Two end-cap toroids are positioned inside the barrel toroid, at both ends, and provide the required 4.1 T magnetic field across a radial span of 1.5 m to 5 m. Each end-cap toroid has a weight of 240 t. The coil system of the end-cap toroid is rotated by an angle of 22.5° compared to the barrel toroid coil. In this way, radial overlap between the two coil systems is provided and the bending power optimized. The most important parameters for momentum measurements are:

$$I_1 = \frac{0.3}{p_T} \int_0^l Bsin(\theta)_{(d\vec{I},\vec{B})} dl,$$

(2.7)

$$I_2 = \frac{0.3}{p_T} \int_0^{lsin(\theta)} \int_0^{\frac{r}{sin(\theta)}} Bsin(\theta)_{(d\vec{I},\vec{\mathbf{B}})} dl dr.$$

(2.8)

$I_1$  describes the bending power field and  $I_2$  represents the total transverse deflection of the particle from its initial path. They are field integrals calculated on the azimuthal direction of the particle  $(l = r/sin(\theta))$  and on its radial trajectory.  $\theta$  is the longitudinal component of the angle between the track and the magnetic field.

## 2.2.5 Forward detectors

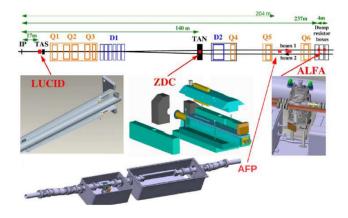

The ATLAS forward region is covered by a set of small sub-detectors: LUCID (Luminosity measurement using Cherenkov Integrating Detector) [19], ZDC (Zero-Degree Calorimeter) [20], AFP (ATLAS Forward Proton) [21] and ALFA (Absolute Luminosity For ATLAS) [22]. Fig. 2.7 shows their position along the beam line.

Figure 2.7: Infrastructure of the ATLAS Forward Detector.

#### LUCID

Luminosity measurement using Cherenkov Integrating Detector (LUCID) is a Cherenkov counter that monitors the luminosity delivered by the LHC accelerator. Two LUCID detectors are placed in both forward regions at 17 m from the interaction point in a symmetrical way. Each one is made of 16 photomultiplier tubes and 4 quartz fiber bundles.

In the quartz window, as well as in the fiber bundles, Cherenkov light is produced by the charge particle. The photomultipliers detect charged particles when the light is carried to the photomultipliers.

### ZDC

Zero-Degree Calorimeter (ZDC) detects forward neutrons, in both pp and heavy ion collisions, for  $|\eta| < 8.3$ . The detector is placed at 140 m in both sides of ATLAS and is composed by an electromagnetic module (about 29 radiation lengths thick), and three hadronic modules, made by tungsten with an embedded matrix of quartz rods, attached to photomultiplier tubes.

### AFP

The goal of ATLAS Forward Proton (AFP) is to measure transfer momentum and energy loss of protons emitted from the collision point in very forward directions. Along the beam line there are two AFP detectors, at 204 m and 217 m, that contain a 3D silicon tracker and a time-of-flight detector in the far stations.

#### ALFA

Absolute Luminosity For ATLAS (ALFA) is the furthest detector, located 237 m from the interaction point, on both ATLAS sides. Each detector is made of staggered layers of square-shaped scintillating fibers, read out by photomultiplier tubes. It aims to measure the elastic pp scattering at small angles. The detector can approach the beam very close without entering the machine vacuum because the set-up is installed in Roman Pot stations, vessels that are connected to the accelerator vacuum via bellows.

## 2.3 Trigger and Data Acquisition system

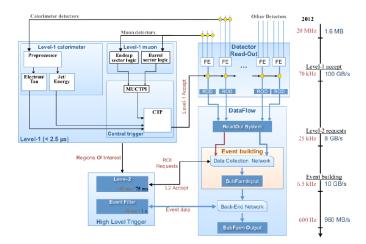

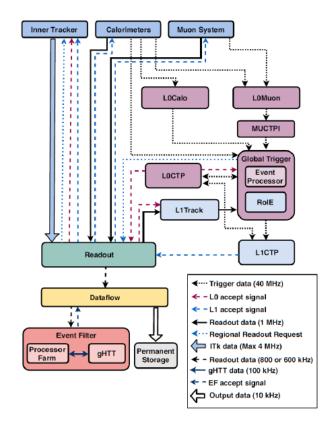

The Trigger and Data Acquisition (TDAQ) system [23], shown in Fig. 2.8, is a fundamental component of the ATLAS detector because it ensures optimal data-taking conditions. This thesis work is related to the ATLAS TDAQ system and, in particular,

Figure 2.8: Performance of the ATLAS Trigger System in 2015 [24].

in chapter 3 will be presented its future upgrade as a consequence of the high luminosity that will be achieved by HL-LHC ( $\sim 10^8$  pp processes produced in 1 s).

Data of collision event is moved from the detector readout electronics into frontend buffers at the bunch crossing rate. Only some of these events are interesting and might lead to new discoveries. The entire set of the events cannot be saved because it would require a memory not compatible with the storage technologies used as hard disk and tapes. Moreover, their costs of production and maintenance (about hundreds of PetaBytes of data produced per year) would be too high. Trigger and DAQ system select a few hundred events per second for recording to a permanent storage for later study. In order to do this, the DAQ system has to transport and assemble the event data from the front-end buffers to the recording on disk. To reduce the flow of data to manageable levels, ATLAS Run 2 Trigger started to exploit an event selection system based on a multi-level trigger: Level-1 (L1), Level-2 (L2) and Event-Filter (EF). The L1 trigger is hardware-based and processes data from the calorimeter and the muon detectors; more precisely the data to trigger comes from the RPC and the TGC chambers. The L1 trigger decision is taken by the Central Trigger Processor (CTP), which receives inputs from the L1 calorimeter (L1Calo) and L1 muon (L1Muon) triggers as well as several other subsystems like the Minimum Bias Trigger Scintillators (MBTS) [25], LUCID Cherenkov counter and the ZDC. This set of sub-detectors gives the trigger signatures as high- $p_t$ muons, electrons/photons, jets,  $\tau$  – leptons decaying into hadrons and missing transverse

energy. The data passing through the hardware are subjected to discrimination by the ReadOut Driver (ROD) structure which applies fragment building and associated error detection, data checking, transformation and monitoring. Then the data are received by a readout device called Read-Out System (ROS) which sends the information to the High-Level-Trigger (HLT), a set of the two subsystems: the Trigger Level-2 and Event Filter trigger. HLT is a processor farm exploiting 28k CPU to rapidly investigate the Region-of-Interest (RoI,  $\eta$  and  $\phi$ ) identified by the L1. The rate of the dataflow here is reduced to approximately 50 kHz, with a decision time for each collision of 2  $\mu s$  from the collision itself. The hardware-programmable coincidence logic rules are six muon  $p_T$ threshold for this part of the trigger, three for the 6-9 GeV (low  $p_T$ ) and three for the 9-35 GeV (high  $p_T$ ). The L2 trigger is software-based and operates from a large farm of about 40k CPU cores. Informations of RoIs from L1 can be used for regional reconstruction by the trigger algorithms. It can reach a rate less than 5 kHz in periods lower than 50 ms. Eventually, the Event Filter is the final stage of the trigger chain. It gives the possibility to reach 30 Hz in 4 s, that is the standard time of the off-line event reconstruction of the ATLAS TDAQ. The HLT achieves a further reduction to 0.4-1 kHz. After the events are accepted by the HLT, they are transferred to local storage at the experimental site and exported to the Tier-0 facility at CERN's computing centre for offline reconstruction.

# Chapter 3

# ATLAS Phase-II upgrade

High-Luminosity upgrade has the aim to expand the LHC research area for physics beyond the Standard Model. After the end of Run 3 the accelerator will be pushed to and beyond its structural limits in terms of peak of luminosity, pile-up and proton-proton collision energy. In order to keep up with these new conditions, the ATLAS experiment requires an upgrade in terms of sensitivity and precision of its detectors. The most important modifications planned for this so-called Phase-II involve the Trigger and Data Acquisition system, the Inner Tracker system, the Calorimeters (both the Liquid Argon and the Tile one) and the Muon Spectrometer.

## 3.1 Upgrade proposals

Physics research of the ATLAS detector during Phase-II will include:

- Precision measurements of the properties of the Higgs Boson (i.e. the coupling of fermions or self-coupling);

- Precision Standard Model measurements, (i.e. top mass and cross-section);

- Searches for Beyond Standard Model (i.e. Super Symmetry or long-lived particles);

- Flavour physics (i.e. rare B-meson decay);

- Heavy-Ion Physics.

HL-LHC will represent an extremely challenging environment to the ATLAS experiment. All modifications required to sustain this run period will be done during the Long Shutdown 3 (LS3) that targets to step forward in sensors, hardware, firmware, software and strategies to reach values of the LHC parameters one order of magnitude higher even than those planned. For example, the total integrated luminosity expected is at least 3000  $fb^{-1}$ , compared to the 300  $fb^{-1}$  of Run 3. As a consequence, data collected during the HL-LHC run will be ten times that of the initial design, by around 2030. In order to endure this new operational phase of working, the ATLAS experiment will require an upgrade as well. Exploring the new HL-LHC scenario, technical limits of the LHC capabilities give the possibility to study the performances of the detector through simulations, which ensures also that the Phase-II detector upgrade is able to take advantage of the ultimate luminosity. The ATLAS collaboration firstly gave a description of the initial plan for the Phase-II upgrade of the detector in the Letter of Intent (LoI) in 2012. Since then, the collaboration has been improving and refining the initial proposals considering that the possible development of the upgrade will depend on the actual maximum luminosity reached and on the mean number of interactions per bunch-crossing.

The most important upgrades planned by the ATLAS collaboration involve the Trigger and Data Acquisition (TDAQ) and the Inner Tracker (ITk) system, which are also the most expensive components of the whole detector. Other changes will be carried out in the Calorimeters (both the Liquid Argon and the Tile one) and in the Muon Spectrometer (MS). Some of the sub-detectors will be completely replaced but, in other cases, such as the most new sub-detectors and for the ones which can sustain the high pileup, only the electronics for the readout will be substituted. The new sub-detectors design is driven by the instantaneous Luminosity of  $7.5 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ , letting a  $3000/4000 \text{ fb}^{-1}$ of integrated luminosity with a pile-up of 200. The detecting strategy will be analogous as the current experiment, with a similar kind of set up, with detectors placed at the same distance to the interaction point. The  $|\eta|$  coverage will slightly change as: the Inner Tracker will sample data from  $|\eta| = 4$ , the Muon Spectrometer will receive new RPC allowing to reach  $|\eta| < 1$  and the new High Granularity Timing Detector is planned to cover  $2.4 < \eta < 4.0$ . The following sections focus on ATLAS Phase-II most relevant upgrades planned for this new working period of HL-LHC.

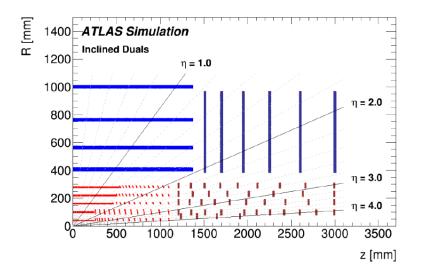

Figure 3.1: Active areas of ITk are schematized in the ATLAS coordinate system, with in the vertical axis the radius from the beam pipe and in the horizontal axis the z coordinate parallel to the beam line [26].

### 3.1.1 Inner Tracker

The increased luminosity anticipated in previous chapters, along with the associated data rate and accumulated radiation damage, make the current ATLAS inner detector inoperable. The Inner Tracker (ITk) is a new all-silicon double tracker detector with the same function as the current Inner Detector (ID) of Section 2.2.1, that will represent the core of the new ATLAS detector. The general requirement for the ITk is to deliver equal or better tracking performance to that provided by the current ID, despite an average pile-up of up to  $\langle \mu \rangle = 200$  events. This can be stand through an "inclined layout" with  $|\eta| = 4$ . ITk is composed of the Strip Detector and the Pixel Detector. The former, starting from the outside, will have four barrel layers and six petal-designed end-cap disks covering  $|\eta| < 2.7$ . The Pixel Detector, instead, will have five flat layers, five inclined layers and five end-cap layers, together giving  $|\eta| < 4$ . The ITk planned layout is shown in Fig. 3.1, while through a software simulation it is possible to build the core scheme of ATLAS, as illustrated in Fig. 3.2.

This detector is designed to measure the transverse momentum and direction of isolated particles (particularly muons and electrons), and allows to reconstruct the vertices

Figure 3.2: Scheme of the ITk detector of ATLAS reconstructed by simulations.

of pile-up events and associate it with the hard interaction. Moreover, ITk will be able to reconstruct and identify secondary vertices in b-jets with a high efficiency and purity and also the decay of  $\tau$ -leptons, including impact parameter information. As already anticipated, the detector has to afford an environment in which the integrated radiation dose is ten times more than previous LHC conditions. Indeed, considering the instantaneous luminosity and the pileup at which HL-LHC operates, the radiation tolerance of the inner technology should achieve a resistance of 9.9 MGy.

New technologies are used to ensure that the system can survive this harsh radiation environment. Moreover, the new read-out scheme allows the implementation of a track trigger contributing to the major improvements in the online trigger capabilities using a CMOS technology fabricated front-end chip.

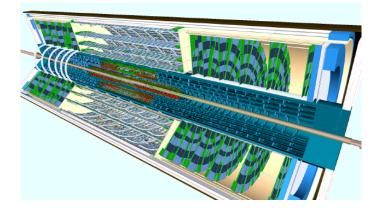

## 3.1.2 High Granularity Timing Detector

The High Granularity Timing Detector (HGTD) [27] is a new architecture proposed in order to increase the precision of luminosity measurements. A better view of where it is expected to be placed is shown in Fig. 3.3. This position is very strategic because it gives the possibility to measure both online luminosity bunch-per bunch during HL-LHC running and enhance the high precision sampling of the integrated luminosity. The consequent increase in the luminosity resolution is fundamental for the Higgs couplings survey. The HGTD will increase the spatial and time performance of ITk with a 30 ps

Figure 3.3: 3D view of the new HGTD detector and its position in the future ATLAS structure.

time resolution for the minimum ionizing particle going through the innermost detector. Between the HGTD and the end-cap/forward calorimeters region, a 50 mm moderator is planned to be inserted to protect from back-scattered neutrons the HGTD and the ITK. The front-end custom ASIC ALTIROC is being developed and it is planned to be bump-bonded to the silicon sensor that is currently under study. The advantage in developing this ASIC consists in the high time and spatial resolution and the radiation hardness provided. Other important operations are: counting the number of hits registered in the sensor; 40 MHz transmission to allow unbiased, bunch-per-bunch measurements of the luminosity; coping with the minimum-bias trigger. The HGTD end-cap will integrate: one hermetic vessel, two instrumented double sided layers mounted on two cooling/support disks and two moderator pieces internally and externally the hermetic vessel. The detecting region of HGTD will cover the range of  $2.4 < |\eta| < 4.0$ .

### 3.1.3 Calorimeter

The read-out electronics and the low-voltage powering system of the ATLAS Liquid Argon Calorimeter (LAr) will be updated [28] in order to overcome the technology limitation and obsolescence. Along with the modifications done during Phase-I, the LAr will gain readout performance efficiency from new boards in the on-detector region: the FEB2 (Front-End Board 2) and Calibration Board. The first one will be responsible to manage the analog processing and the second to inject calibration signals. On the off-

Figure 3.4: Calorimeter system scheme in the ATLAS Phase-II detector. The Long Barrel (LB) and the Extended Barrel (EB) are both divided in A and C.

detector side a new board, LAr Signal Processor Board (LSPB), will be used to transmit data to the DAQ structure. Its goal will be to digitize FEB2s information and apply digital filtering to the signals of each LAr calorimeter cell. Custom ASIC will be the technology used for the FEB, while for the LSPB it will be FPGA.

Instead, in the central region of the hadronic calorimeter, the Tile Calorimeter (Tile-Cal) [29] will have the same position and goal as in Section 2.2.2. Fig. 3.4 shows the scheme and position of the Tile Calorimeter in the scenario of ATLAS Phase-II. The sub-detector will capture roughly 30% of the jet energy and, similarly to the previous runs, it will be of crucial relevance in jet and missing energy measurements, jet substructure, electron isolation and triggering.

## 3.1.4 Muon Spectrometer

The Muon Spectrometer (MS) [30] during Phase-II requires a significant improvement in terms of performances and of precision in the track reconstruction by the triggering system. The current muon spectrometer provides a Level-1 (L1) hardware muon trigger according to the coincidences of hit within different detector layers. A software confirmation of it is performed by the high-level trigger which exploits refined  $p_T$  measurements from the precision chambers. For the Phase-II upgrade the muon spectrometer will pro-

Figure 3.5: Scheme of the active areas and layout of the MS Phase-II.

vide a finer granularity trigger based on Monitored Drift Tube (MDT). This improves the sharpness of the transverse momentum threshold at L1 and, if the L0 latency allows it, also at L0. Concerning L0, its coverage and redundancy will rise, due to the addition of the new Resistive Plate Chamber (RPC) detectors that will be placed in the barrel region ( $|\eta| < 1$ ). Moreover, for the Phase-II upgrade, the original on-chambers electronics for the MDT may be partially or completely replaced. The final configuration of the upgraded Muon spectrometer is shown in Fig. 3.5. The trigger electronics is upgraded both in the barrel and the end-cap spectrometers and, in order to improve the trigger selectivity, a replacement of the trigger chambers in the forward region ( $2.0 < |\eta| < 2.4$ ) is expected. The new ATLAS requirements of the L0/L1 trigger system are automatically applied to the readout electronics are not able to sustain the rate of 400 kHz, and it must be replaced with an improved one. Eventually, another important reason for the upgrade of the trigger electronics consists of the necessity for an improved selectivity for high  $p_T$  tracks, which calls for a better space resolution in the bending direction ( $\eta$ ).

In the Reference scenario, the muon acceptance will grown thanks to the inclusion of a very forward muon tagger, attached to the New Small Wheel (NSW) shielding disk and covering the range of  $2.6 < |\eta| < 4.0$ . The main modifications for this scenario involve the barrel and end-cap detectors. In the barrel region, the RPC is added with also a small tube diameter MDT (sMDT) in the small sectors of the Barrel Inner layer (BI). In the latter the already existing on-detector electronics will be replaced. In the end-cap region, the MDT front-end readout will be replaced and a very forward tagger is included to take advantage of the very-forward ITk tracking, which in the Reference scenario has the largest extension. The modifications are required for this new run period because, for instance, present MDT read-out electronics cannot cope with the expected trigger rate. For this reason, the new trigger system will have to maintain a high level of efficiency, that consists of finding high- $p_T$  tracks and keeping the rate of fake triggers low. Moreover, always in the end-cap region, the L0 trigger electronics of all the chambers (excluding the NSW) will be replaced. Indeed, the current read-out electronics of the trigger chamber systems do not supply information on the pulse height of the signals, therefore position measurements cannot be performed by using charge interpolation.

## 3.2 Trigger and the Data Acquisition

The HL-LHC upgrade represents a significant challenge also for the Trigger and the Data Acquisition (TDAQ) system of ATLAS [31]. In order to perform physics research mentioned in Section 3.1, it is necessary a high efficient event selection regarding the Higgs boson and new physics. Considering the larger step increase in the luminosity, exceptional performances from the trigger and data acquisition system are required to sustain a higher maximum rate and a longer latency. Similarly to what happened for most of the components of the ATLAS detector, also the upgrade of the TDAQ system comes through different evolution stages in terms of designs and technologies compared to the initial plan.

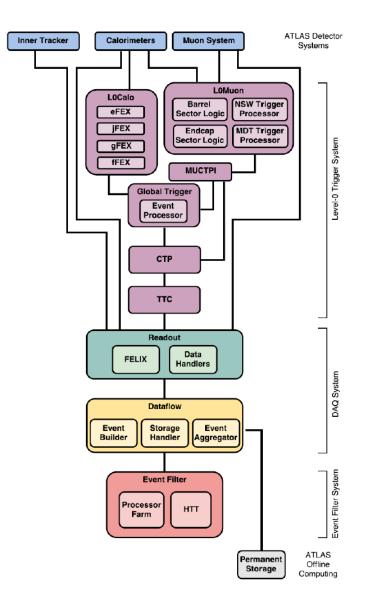

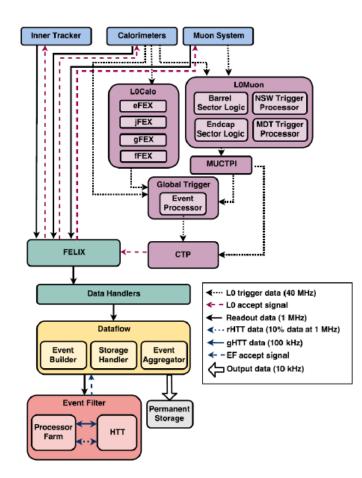

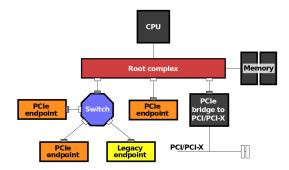

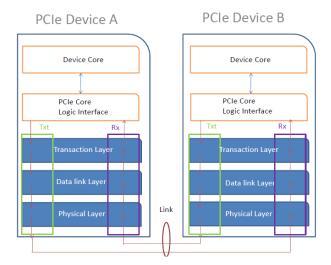

A general architecture layout is given in Fig. 3.6, where there are the main three different subsystems which compose the ATLAS TDAQ: the Level-0 Trigger, the DAQ (Readout and Dataflow subsystems) and the Event Filter. In the Reference scenario, during LS2 the front-end electronics of all the existing ATLAS detector systems are replaced, excluding the systems already upgraded during the LS1 for the Phase-I. The architecture that will be chosen has passed through three different designs: the baseline, the evolved and an alternative. The first one is a single level trigger (L0-Level) which was planned to evolve with the inclusion of a L1track level, which differs compared to the alternative in terms of the technology exploited:

• a hardware-based system (i.e., HTT), made of custom-designed Associative Memory (AM) Application Specific Integrated Circuit (ASICs) for pattern recognition

Figure 3.6: Design of the baseline L0-only of the TDAQ Phase-II architecture. The upgrade project is divided into three main system: Level-0 Trigger, DAQ (Readout and Dataflow subsystems) and Event Filter.

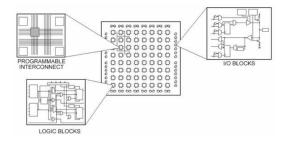

and Field Programmable Gate Arrays (FPGAs) for track reconstruction and fitting;

• a software system, mostly Central Processing Unit (CPU)-based servers with or without accelerators (e.g., GPGPUs).

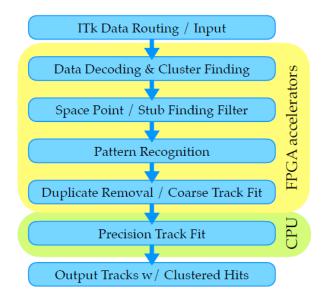

In the initial plan of the Technical Design Report (TDR) of the TDAQ Phase-II, the baseline for EF Tracking is the so-called Hardware Tracking for the Trigger (HTT). The latency requirement suggested an evolved configuration of this hardware tracking system with the inclusion of a new level of trigger, Level-1 (L1), which would have processed regional data from the strips and the outer Pixel Detector layers. The current status of the research is to remove the option to evolve to a L0/L1 system, thanks to the improved resource-efficiency of the software, that allows to remove the latency constraints. Therefore the decision is to refine a new baseline. Since the methods developed for track reconstruction in both TDR baseline and evolved scenarios represent viable options for the new EF Track alternative implementations, more details about them are soon presented. In Section 3.2.3 the pattern matching method of the baseline relies in the AM ASIC technology, while in the next chapter is described the method developed for the evolved design, which exploits Hough Transform algorithm implemented on FPGAs.

## 3.2.1 Baseline Architecture

The baseline architecture initially selected for the TDAQ system consisted of three levels: the Level-0 trigger, the DAQ (Readout and Dataflow) and the Event Filter. The sub-parts of the trigger itself and the baseline design for the TDAQ architecture are shown in Fig.3.7. The hardware-based L0 trigger system is composed by four different subsystems:

- The Level-0 Calorimeter Trigger (L0Calo) is based on the Phase-I L1Calo system with a new forward Feature EXtractor(fFEX), to ensure an efficient electron identification in the region  $3.2 < |\eta| < 4.0$ . Electrons,  $\tau$ -leptons, jet candidate are reconstructed through coarse-granularity data that can also calculate the missing transverse energy  $E_T^{miss}$ .

- The Level-0 Muon Trigger (L0Muon) is completely upgraded compared to the

Figure 3.7: Design of the TDAQ Phase-II baseline architecture where the trigger is in purple. The single level hardware-trigger L0 is composed by the L0Calo and L0Muon sub-systems, it steps through the Global Trigger and eventually reaches the CPT. The L0 trigger dataflow is represented by the black dotted arrows, while the full black lines represent the readout dataflow, which will start only if the detectors and the FELIX recive the L0 accept signal (dashed purple line). Readout is in green, dataflow in yellow and Event Filter in red [31].

Phase-I system. The sub-system employs the upgraded logic of the barrel and endcap sector and the NSW trigger processors to reconstruct the muon in the barrel, forward and end-cap regions;

- Global Trigger is a subsystem of the L0 trigger system that will perform offline-like algorithms on full-granularity calorimeter data. It will also identify topological signatures that can include a wide variety of four-vector combinations involving sums, angles and invariant masses.

- Central Trigger Processor (CTP) subsystem considers the trigger menu configuration, prescale factors, and dead-time requirements to form the final Level-0 decision, which is transmitted as a L0A signal applying flexible pre-scales and vetoes to trigger items.

The MUCTPI (Muon CTP Interface) provides an interface between the barrel and end-cap components of the L0Muon system on one hand, and the Global Trigger and CTP on the other. It identifies muon candidates that are counted twice in the L0Muon system (overlap removal) and calculates multiplicities for various transverse-momentum thresholds. The L0Calo and L0Muon/MUCTPI subsystems send their selected objects to the Global Trigger, including spatial locations, reconstructed energy/momentum values and discriminant variables. These objects are then combined with the results of the Global Trigger calorimeter processing to refine the e/gamma, tau, muon and jet selections.

Following the Level-0 trigger decision, the resulting data are transmitted over custom point-to-point serial links, to the Readout subsystem within the DAQ system. The first element of the Readout is the Front-End Link eXchange (FELIX) subsystem and it provides a common interface between the detector-specific custom point-to-point seriallinks and the commodity multi-gigabit data network downstream. Data are received along the network by Data Handlers, where detector specific processing (such as formatting and/or monitoring) can be implemented before the Dataflow subsystem, in which data are buffered. The Readout subsystem is designed to handle 1 MHz event rate, for a total bandwidth of 5.2 TB/s. In order to endure this 1 MHz input rate of data, a large Event Filter (EF) processor farm is required and commodity-CPU-based event processing would have been handled by the Hardware-based Tracking for the Trigger HTT subsystem, that was designed to provide the fast hardware-based track reconstruction for the TDR baseline TDAQ. Regional tracking by the regional HTT (rHTT) allows a fast initial rejection in the EF of single high- $p_T$  lepton and multi-object triggers from background processes, to reduce the rate to around 400 kHz. This system is specified to operate at 1 MHz and use up to 10% of the ITk data, by selecting tracking modules in regions based on the results of the Level-0 trigger system. Software-based reconstruction follows to achieve further rejection. This is aided by global tracking at around 100 kHz using the global HTT (gHTT) but in this case with the intent to produce tracks closer to offline quality, suitable for b-jet tagging,  $E_T^{miss}$  soft term calculation, soft jets and pile-up suppression. Events selected by the EF are in the end transferred to the permanent storage of the ATLAS offline computing system. The raw output event size is expected to be 6 MB, and the total trigger output is expected to be 10 kHz; thus, the total bandwidth out of the system is 60 GB/s.

### 3.2.2 Evolved Architecture

The solution of a single hardware trigger considered by the TDR baseline TDAQ system had two critical aspects which involved the main impacts on the performance of the system itself: the hadronic trigger rate and the inner Pixel Detector layer occupancy must not become higher than their expected values. With the purpose to fix the issues that could have been raised in case in which this happens, TDAQ hardware-based trigger infrastructure was designed to "evolve". This solution relied on the inclusion of a new level of trigger, Level-1 (L1), which should have processed regional data from the strips and the outer Pixel Detector layers. This two-level development architecture included a L0 trigger rate up to 2-4 MHz and 10  $\mu s$  latency, followed by a L1 trigger rate of 600-800 kHz and latency up to 35  $\mu s$ . ITk PD at this point should have required a higher readout rate of 4 MHz for the layers 2 to 4 where the data selection for L1 needed off-detector in the Readout System based on Global Trigger information. ITk Strip Detector could reach 4 MHz at L0 without changes. The architecture design of the evolved system is shown in Fig. 3.8.

In the evolved case ATLAS would have been touched entirely with different solutions

Figure 3.8: Design of the TDAQ Phase-II evolved architecture. In purple the L0 trigger is composed by the L0Calo and L0Muon sub-systems, the Global Trigger and the L0CPT. Readout is in green, dataflow in yellow and Event Filter in red. In light blue the L1 trigger is composed of L1Track and L1CTP. The black dotted lines represent the L0 and also L1 dataflow. The full black lines correspond to the readout dataflow at 1 MHz, while the dashed black lines represent the readout dataflow at 800 or 600 kHz [31].

in all its parts:

- The hardware trigger was split into a two-level hardware trigger system where HTT should have been the primary reduction operator of L0 for an EF affordable farm size;

- A Region of Interest Engine (RoIE) was added to the Global Trigger in order to calculate Region of Interest (RoI) dependently from L0;

- The data from the ITk strip and ITk outer pixel layers were here used in the Readout system to select the relevant data for L1Track. Similarly to the rHTT of the baseline system, the Readout system was reconfigured to be able to reconstruct tracks within 6  $\mu s$  of latency, but only for tracks with  $p_T > 4 \ GeV$ . It should have reconstructed tracks in the RoIs, which would have been composed of the same hardware and firmware as the HTT components, but with an additional latency of 10  $\mu s$ ;

- Right after the track reconstruction, the resulting trigger was combined with calorimeter and muon-based trigger objects in the Global Trigger;

- the CTP formed the L1 decision.

Resuming, the main differences between evolved and baseline scenarios are the L1Track, the L1CTP and the shift of rHTT from the EF to the L1 Track. In this design, the hardware-based track reconstruction was planned to be implemented in the L1 trigger system, through the reconfiguration of a part of the HTT. Therefore, the main characteristics of the trigger chain are almost the same, excluding that in the evolved system, right after the L1, the whole data rate of 1 MHz is shared between the full and regional detector readout. Hence, the regional readout gets priority over the full readout, with respectively a rate of 200-400 kHz and 600-800 kHz detector readout.

## 3.2.3 Hardware Tracking for the Trigger

The Hardware Tracking for the Trigger (HTT) system was the hardware-based system that was created by the ATLAS collaboration with the aim to reconstruct tracks inside the TDAQ during HL-LHC running. The current decision of the new Event Filter Tracking (EFT), which was launched after HTT, is to commit to the different commodity based solution. This comes from the choice of previous HTT to create two task forces with the purpose to investigate the technologies suggested for both baseline and evolved scenarios.

For this reason, in this section the HTT system for both of the options is described. The HTT structure is divided into rHTT (regional tracking), that finds the tracks in Region of Interest (RoIs), and gHTT (global tracking), that reconstructs the tracks in the entire ITk coverage. For the baseline solution of Section 3.2.1, gHTT provides global tracking with  $p_T > 1$  GeV, while rHTT gives regional tracking with  $p_T > 2$  GeV. In the evolved scenario of Section 3.2.2, instead, the regional tracking is provided by the L1Track, for tracks with  $p_T > 4$  GeV.

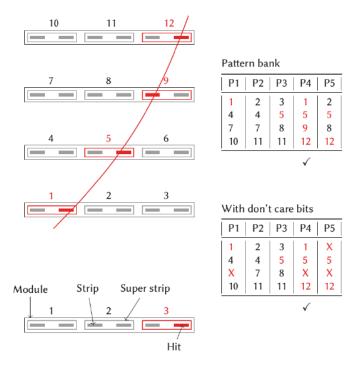

The HTT system performs the track reconstruction in two main steps. Initially, clusters from an eight-layer subset of ITk layers are matched to predefined patterns using a custom-designed AM ASICs, the same technology used in Run 1. This step is the same for both the regional and global reconstruction. In a second step, clusters which are compatible with particle tracks are sent to a fast track-fitter implemented in FPGAs.

In the end, the output produced consists of candidate tracks with also the associated  $\chi^2$  of the track-fit. A second-stage fit is eventually performed by the gHTT system, using clusters from the rest of the ITk layers once they are recovered through the first stage fit.

The latency requirement on the HTT depends on how long data can be buffered and how fast ITK can be read out. In the baseline scenario there is no latency requirement on the HTT because data can be buffered in EF for seconds. On the other hand, in the evolved trigger scheme, data has to be buffered in the read out electronics and in the ITk has to be read out at a much higher rate. Based on these considerations, the latency requirement for the last option is  $6\mu s$  on the regional tracking. This fact has important consequences on the technology chosen by HTT for the reconstruction of tracks and the fitting that is a hardware-based system made of AM ASICs and FPGAs. In fact, a system based on processors and GPUs have longer latency and would require larger buffers, thus more hardware memory. Moreover, in hardware logic, the silicon use is tailored for the specific application, resulting in a lower consumption compared to the general-purpose CPUs and GPUs.

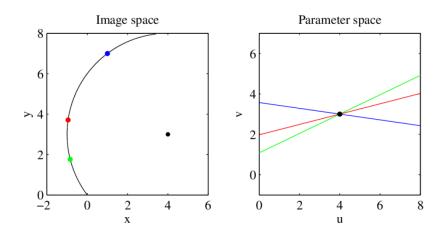

Due to the risks connected to the development of a new ASICs, such as design deadlines, performances and power budget, for the evolved scenario, a new solution that pointed to a clustering filtering method based on the Hough transform algorithm for the track reconstruction was investigated as an alternative to the AM pattern matching technology. A better description of this method will be done in the next chapter, since it is also under study as an option for the final scenario of the EF Track alternative implementation.

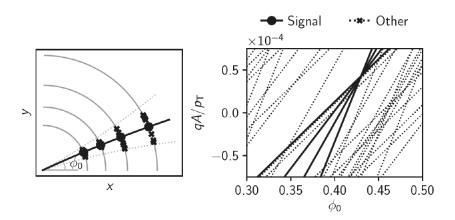

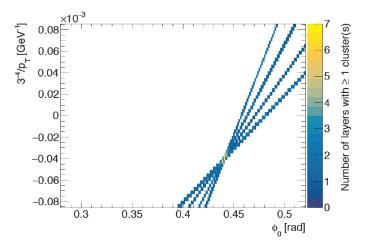

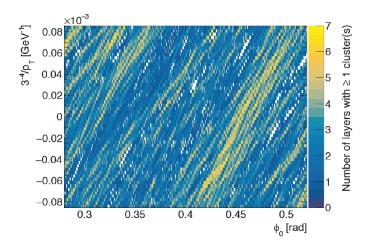

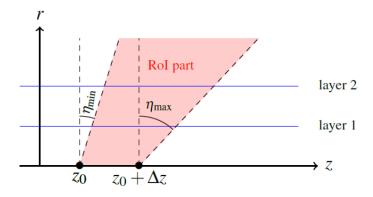

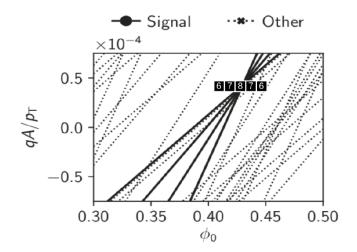

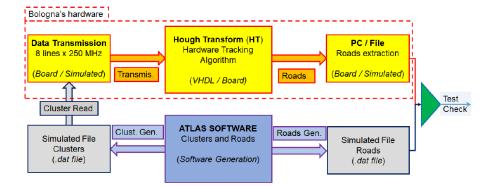

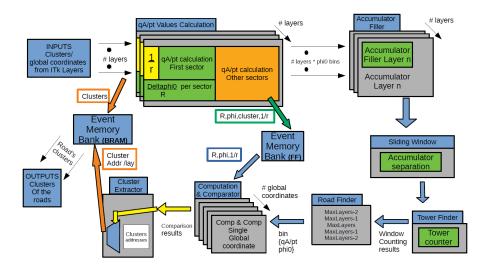

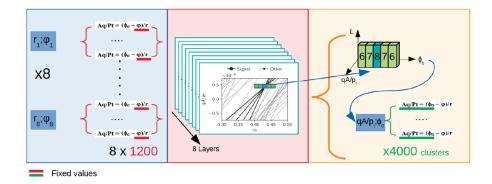

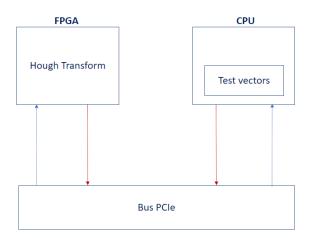

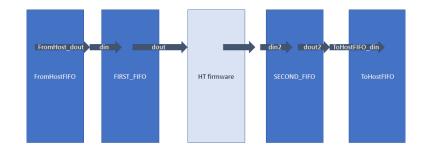

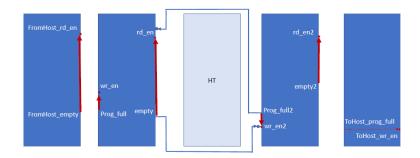

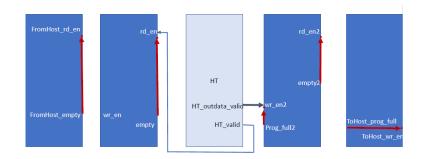

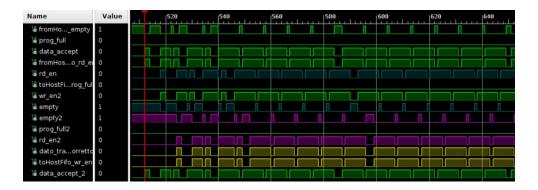

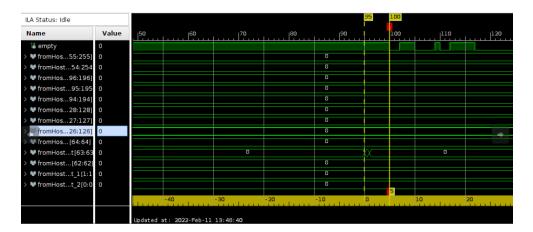

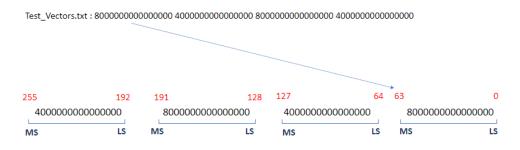

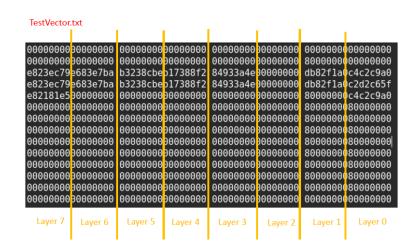

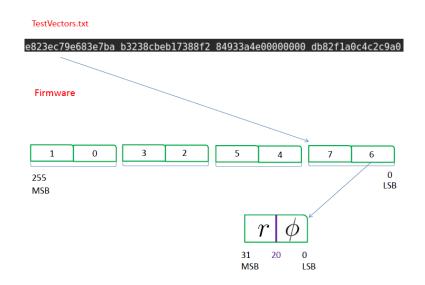

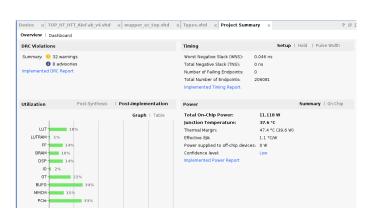

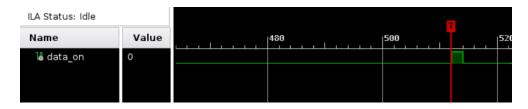

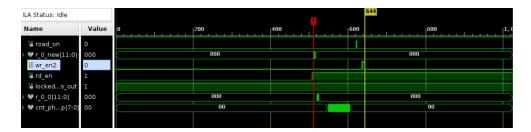

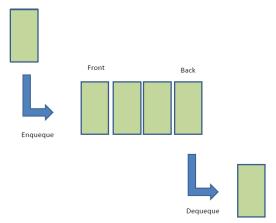

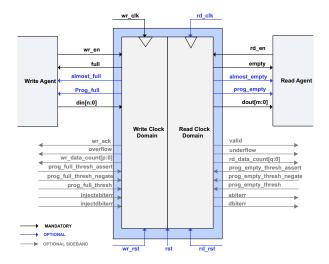

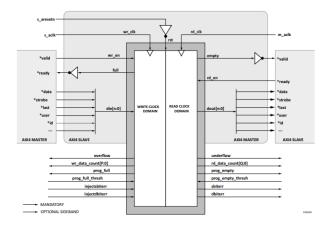

#### Associative Memories