## ALMA MATER STUDIORUM - UNIVERSITÀ DI BOLOGNA

# **Engineering and Architecture School. Electronic Engineering.**

Electronic and Communications Science and Technology Master Program.

## **Master Thesis**

On

Hardware-Software Design of Embedded Systems

# Instruction Prefetching Techniques for Ultra Low-Power Multicore Architectures

Candidate. Maryam Payami Supervisor. Prof. Luca Benini

Academic Year 2015/2016 Session II I would like to dedicate this thesis to my beloved parents and lovely husband

#### Abstract

As the gap between processor and memory speeds increases, memory latencies have become a critical bottleneck for computing performance. To reduce this bottleneck, designers have been working on techniques to hide these latencies. On the other hand, design of embedded processors typically targets low cost and low power consumption. Therefore, computer architects tend to adopt techniques that can satisfy these constraints for embedded domains. While out-of-order execution [1][2], aggressive speculation [3], and complex branch prediction algorithms [4] can help hide the memory access latency in high-performance systems, yet they can cost a heavy power budget and are not suitable for embedded systems.

Prefetching is another popular and effective method for hiding the memory access latency, and has been studied very well for high-performance processors to bridge the CPU-memory gap [5][6]. Similarly, for embedded processors with strict power requirements, the application of complex prefetching techniques is greatly limited, and most of the proposed techniques often suffer from a significant energy loss due to a large amount of wasteful over-prefetching operations and/or the complicated prefetching hardware components. This is while, for embedded systems low energy consumption is also one of the key design issues, especially for those used in battery driven mobile/hand-held devices where large and heavy batteries are not feasible. For this reason, a low power/energy solution is mostly desired in this context.

In this work, we focus on instruction prefetching in ultra-low power processing architectures and aim to reduce energy overhead of this operation by proposing a combination of simple, low-cost, and energy efficient prefetching techniques. We study a wide range of applications from cryptography to computer vision and show that our proposed mechanisms can effectively improve the hit-rate of almost all of them to above 95%, achieving an average performance improvement of more than 2X. Plus, by synthesizing our designs using the state-of-the-art technologies we show that the prefetchers increase system's power consumption less than 15% and total silicon area by less than 1%. Altogether, a total energy reduction of 1.9X is achieved, thanks to the proposed schemes, enabling a significantly higher battery life.

### Acknowledgements

I would like to thank my supervisor Professor Luca Benini for his support and guidance, and for providing this exciting opportunity to work with the state-of-the-art technologies and hardware platforms. My gratitude also goes to Dr. Igori Loi for defining this project and for his valuable insights. Lastly, I would like to thank my lovely husband Erfan for bearing with me and for all the guidance which I received from him throughout this work.

# Contents

| 1 | Intr | roduction and Related Works                          | 1 |

|---|------|------------------------------------------------------|---|

|   | 1.1  | Memory Latency Hiding Techniques                     | 2 |

|   | 1.2  | An Overview of Caching                               | 2 |

|   |      | 1.2.1 Replacement Policy                             | 4 |

|   |      |                                                      | 5 |

|   |      | 1.2.3 Different Types of Cache Misses                | 7 |

|   | 1.3  |                                                      | 8 |

|   |      |                                                      | 9 |

|   |      | 1.3.2 Hardware-based Prefetching                     | 0 |

|   | 1.4  | Related Works                                        | 2 |

|   | 1.5  | Contribution of this Thesis                          | 6 |

| 2 | Met  | thodology and Setup 1                                | 7 |

|   | 2.1  | Hardware Configuration                               | 7 |

|   |      | 2.1.1 Replacement Policy                             | 9 |

|   | 2.2  | Gathered Statistics                                  | 1 |

|   |      | 2.2.1 Average Hit-rate                               |   |

|   |      | 2.2.2 Memory Access Time (MAT)                       | 2 |

|   |      | 2.2.3 Miss Traffic                                   |   |

|   |      | 2.2.4 Total Cache Usage                              |   |

|   |      | 2.2.5 Total Execution Time                           |   |

|   |      | 2.2.6 The Address and MAT Plot                       |   |

|   | 2.3  | Studied Benchmarks                                   |   |

|   |      | 2.3.1 Group 1: Benchmarks with Large Loop Bodies     |   |

|   |      | 2.3.2 Group 2: Benchmarks with Many Function Calls 2 |   |

|   | 2.4  | Baseline Results                                     |   |

|   |      | 2.4.1 Effect of Replacement Policy                   |   |

|   |      | 2.4.2 Effect of Cache Size                           |   |

|   |      | 2.4.3 Effect of Cache Associativity                  |   |

| 3 | Pre  | fetcher Design 3                                     | 5 |

| _ | 3.1  | Design of a Software Prefetcher (SWP)                |   |

|   | 3.2  | Design of a Next-line Prefetcher (NLP)               |   |

|   | 3.3  | Extending the NLP to a Stream Prefetcher (STP)       |   |

| 4 | Effect of Prefetching on Performance                    | 41 |  |

|---|---------------------------------------------------------|----|--|

|   | 4.1 Software Prefetching Results                        | 41 |  |

|   | 4.2 Next-line Prefetching Results                       | 44 |  |

|   | 4.3 Stream Prefetching Results                          | 49 |  |

| 5 | Analysis of Power Consumption, Energy, and Silicon Area | 52 |  |

| 6 | Conclusions                                             |    |  |

|   | Bibliography                                            | 58 |  |

# List of Figures

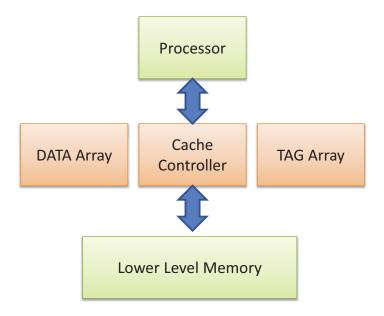

| 1.1  | A simple block diagram of a cache                                                                                                     | 3  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

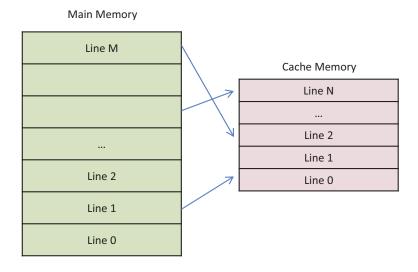

| 1.2  | The mapping in a fully associative cache                                                                                              | 5  |

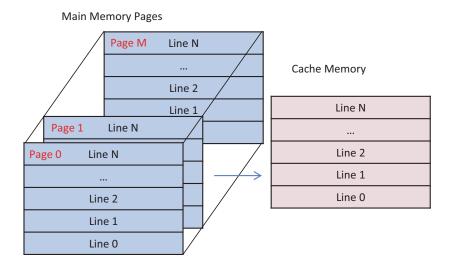

| 1.3  | The mapping in a direct-mapped cache                                                                                                  | 6  |

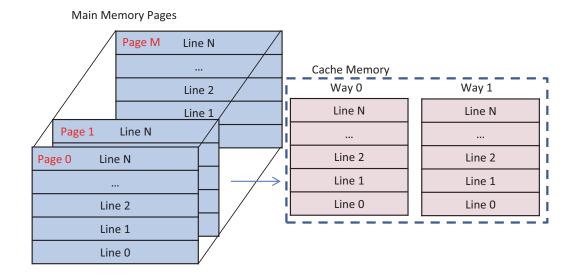

| 1.4  | The mapping in a 2-way set-associative cache                                                                                          | 7  |

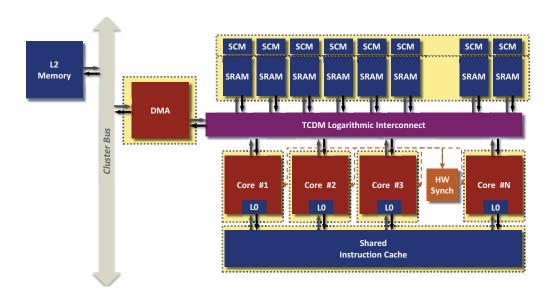

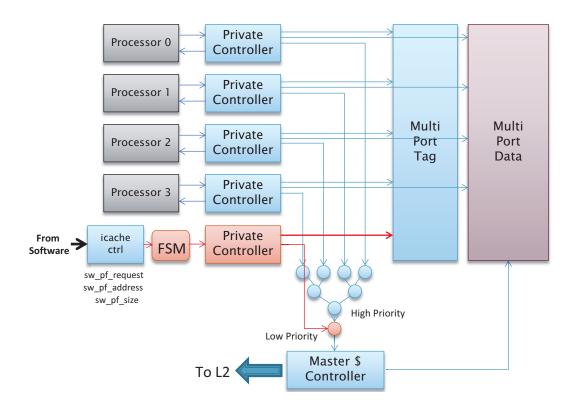

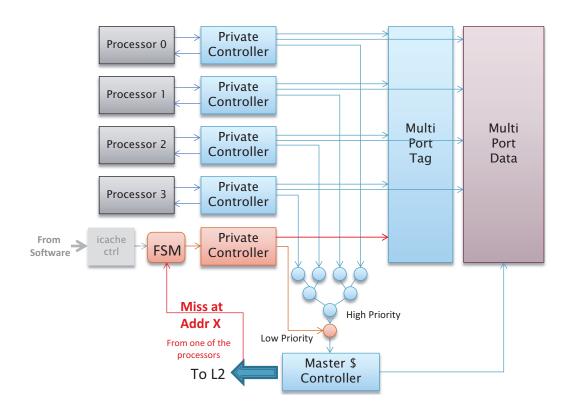

| 2.1  | An overview of a processing cluster in the PULP platform                                                                              | 18 |

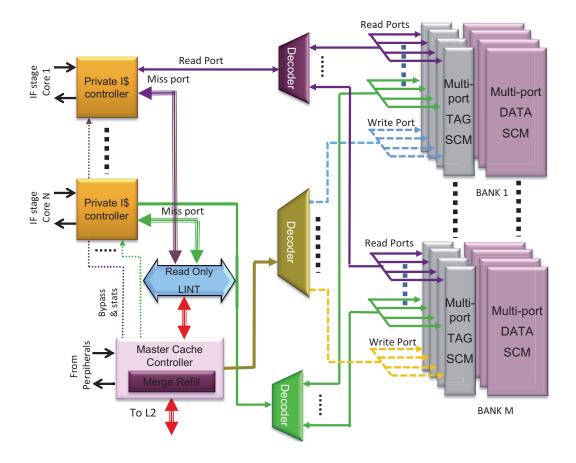

| 2.2  | Detailed block diagram of the multi-ported shared instruction cache in PULP                                                           | 19 |

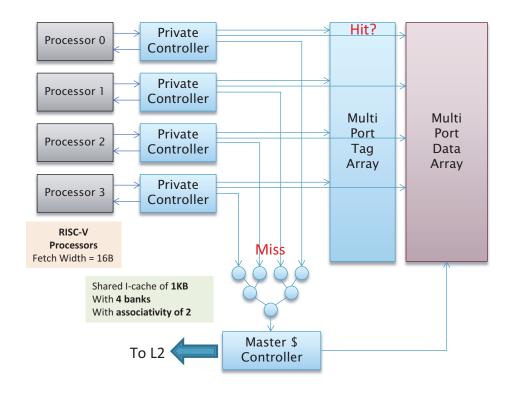

| 2.3  | Simplified block diagram of the multi-ported shared instruction cache in PULP                                                         | 20 |

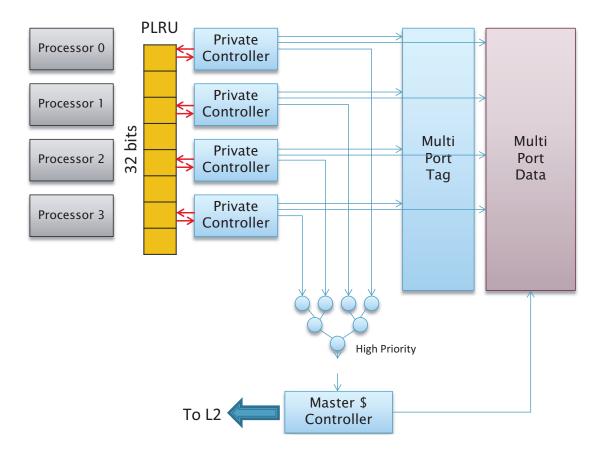

| 2.4  | An overview of the PLRU counters added to the baseline cache                                                                          | 21 |

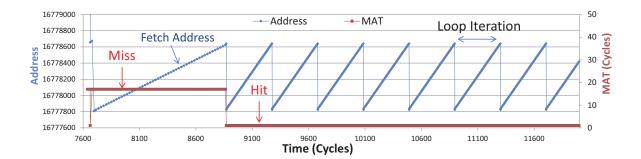

| 2.5  | The Address and MAT plotted together for an application with a single                                                                 | -1 |

|      | loop                                                                                                                                  | 23 |

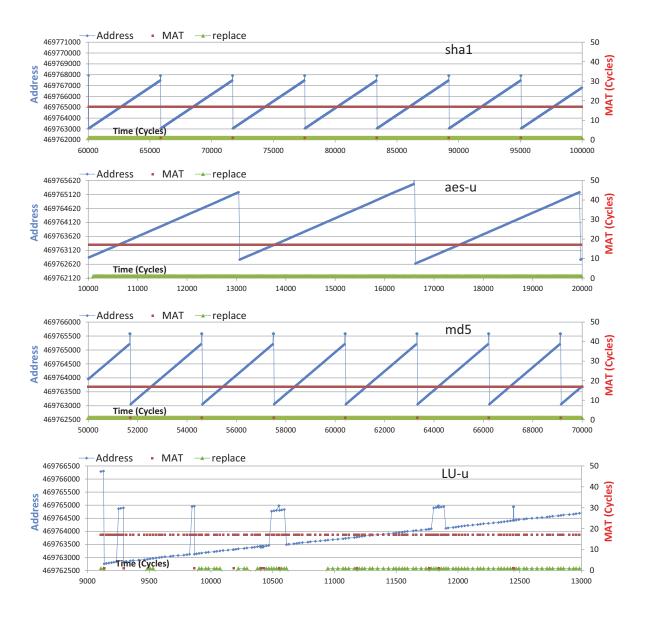

| 2.6  | Address plot for sha1, aes-u, md5, and lu-u                                                                                           | 25 |

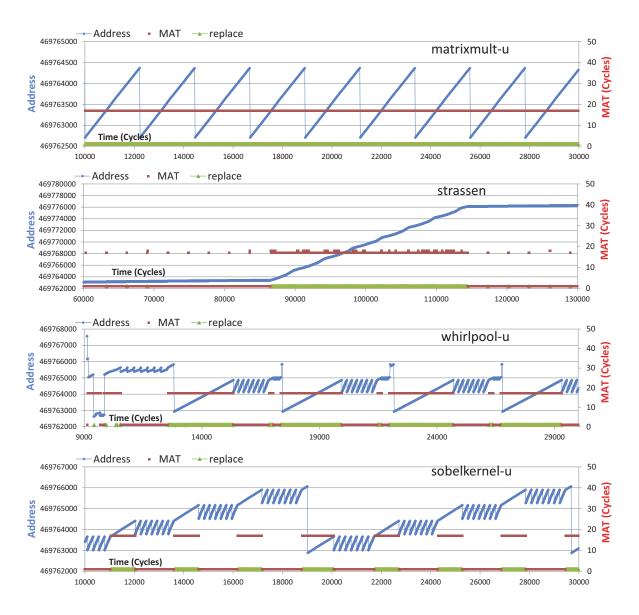

| 2.7  | Address plot for matrixmult-u, strassen, whirlpool-u, and sobelkernel-u                                                               | 26 |

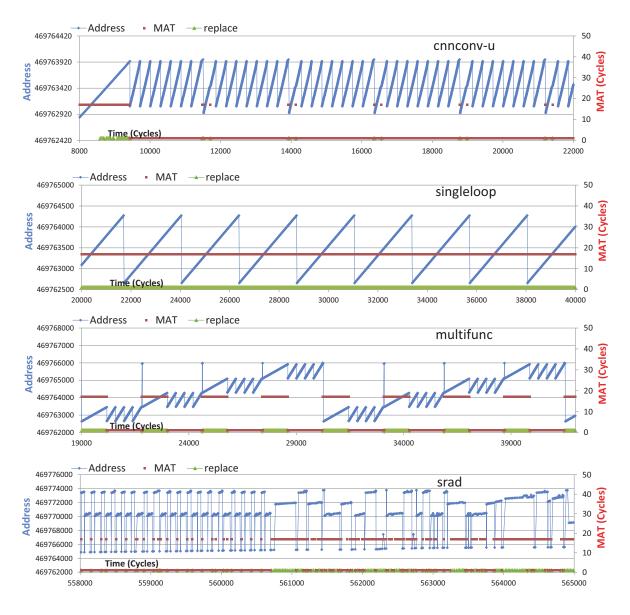

| 2.8  | Address plot for cnnconv-u, singleloop, multifunc, and srad                                                                           | 28 |

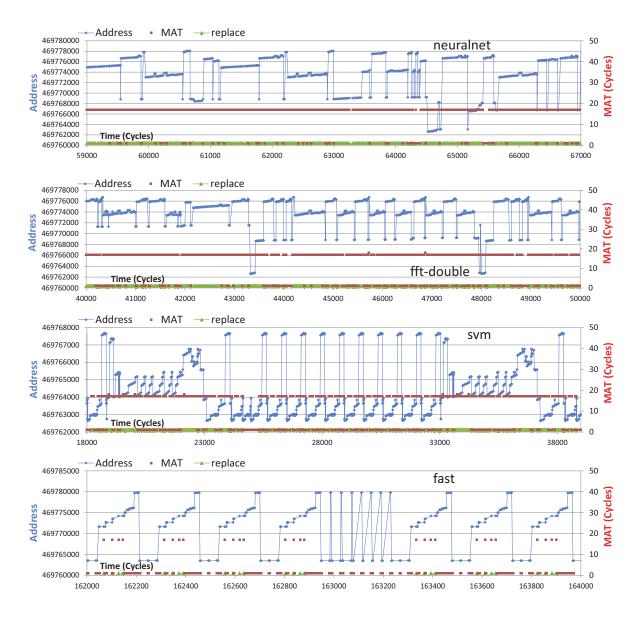

| 2.9  | Address plot for neuralnet, fft-double, svm, and fast                                                                                 | 29 |

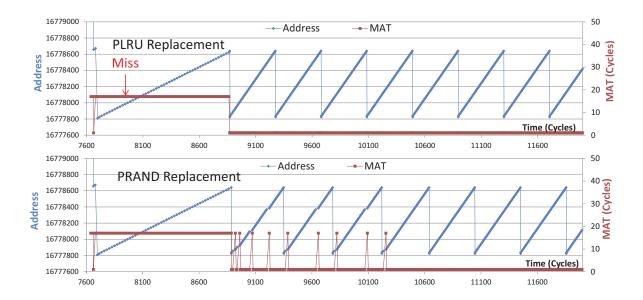

| 2.10 | Comparison on PRAND and PLRU replacement policies for execution                                                                       |    |

|      | of the singleloop benchmark                                                                                                           | 31 |

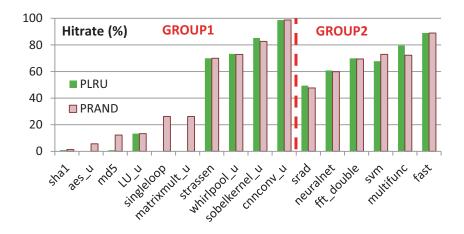

| 2.11 | Comparison on PRAND and PLRU replacement policies for all benchmarks using the baseline hardware configuration (without prefetching). | 31 |

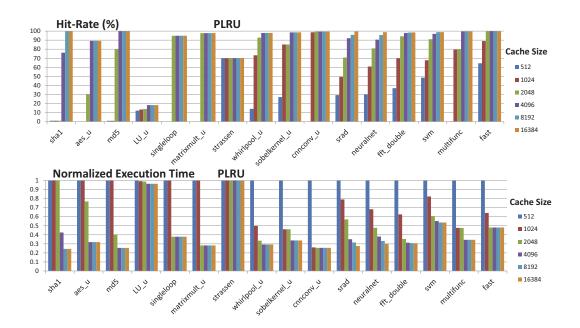

| 2 12 | Effect of cache size on hit-rate and execution time of the benchmarks.                                                                | 32 |

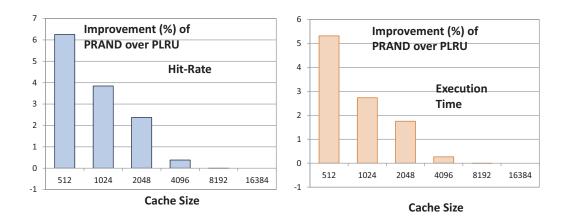

|      | Average improvement of PRAND over PLRU in (left: hit-rate, right:                                                                     |    |

| 0.14 | execution-time) when cache size is changed from 512B to 16KB                                                                          | 33 |

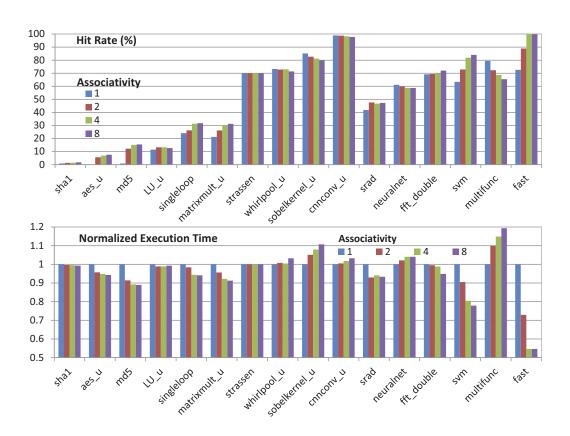

| 2.14 | Effect of cache associativity on the performance of all benchmarks                                                                    | 34 |

| 3.1  | Hardware modifications for implementation of the software prefetcher                                                                  | 36 |

| 3.2  | The software prefetching macros inside C, and the hardware registers                                                                  |    |

|      | added to icache-controller to enable software prefetch                                                                                | 36 |

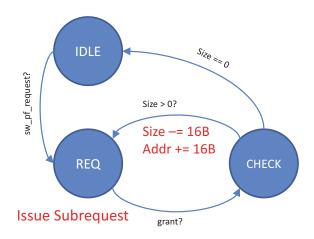

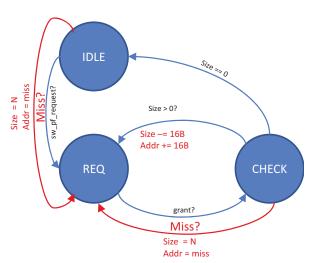

| 3.3  | The finite-state-machine issuing for the prefetch requests                                                                            | 37 |

| 3.4  | Hardware modifications for implementation of the next-line-prefetcher.                                                                | 39 |

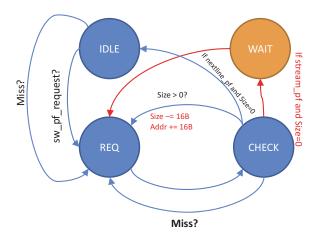

| 3.5  | Modifications to the state-machine to build a next-line-prefetcher                                                                    | 39 |

| 3.6  | Modifications to the state-machine to support stream-prefetching                                                                      | 40 |

| 4.1  | Source code of matrix-multiplication augmented with a single software                                                                 |    |

|      | prefetch                                                                                                                              | 42 |

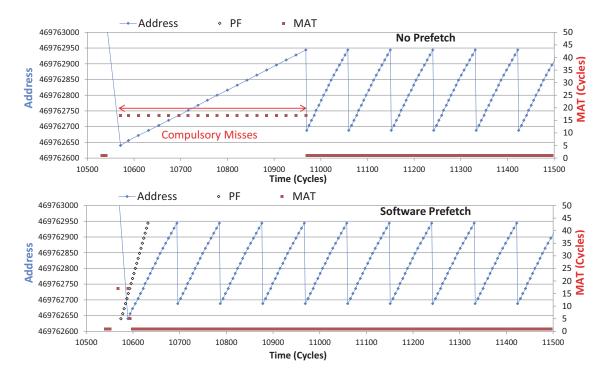

| 4.2  | Execution of the code in Figure 4.1 once without prefetching (top) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | once with one software prefetch (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42 |

| 4.3  | Demonstration of instruction request latency without prefetching (top),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | and with prefetching (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43 |

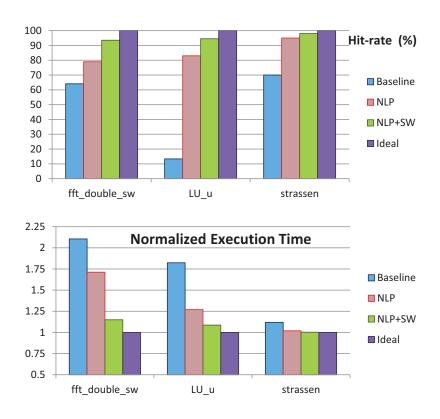

| 4.4  | Effect of software prefetching on hit-rate and execution-time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44 |

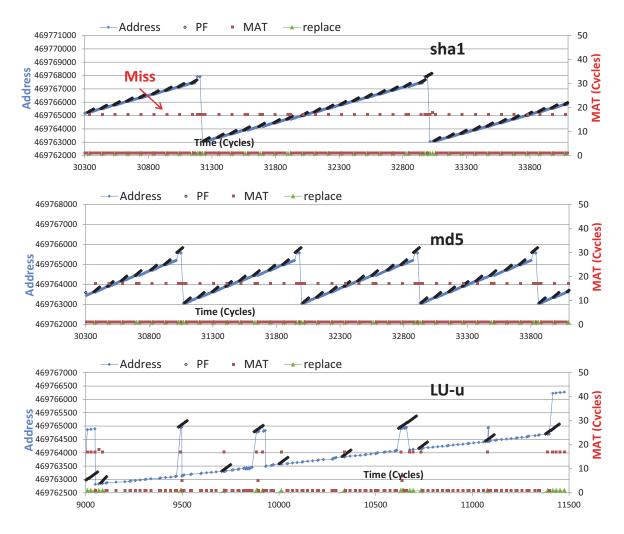

| 4.5  | The address plots for 3 benchmarks with SWP and NLP enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45 |

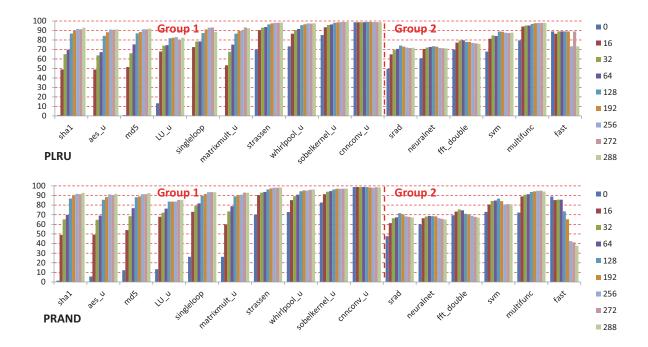

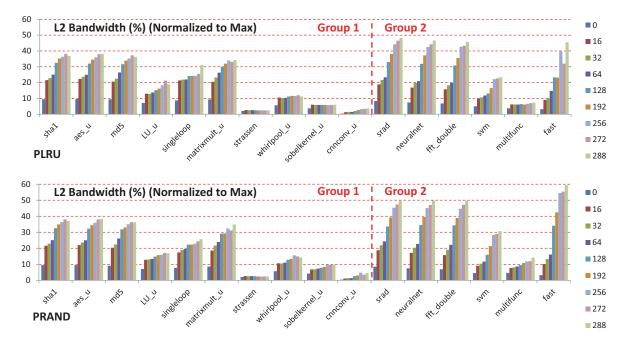

| 4.6  | Effect of prefetch-size of NLP on the ICache hit-rate. Top: PLRU re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      | placement, Bottom: PRAND replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46 |

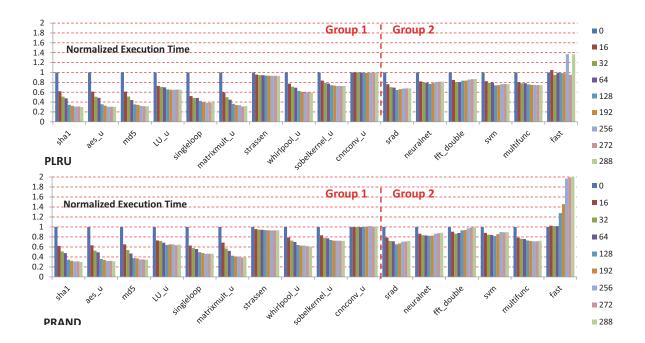

| 4.7  | Effect of prefetch-size of NLP on the total execution time. Top: PLRU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | replacement, Bottom: PRAND replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47 |

| 4.8  | Effect of prefetch-size of NLP on the L2 bandwidth (MB/sec). Top:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | PLRU replacement, Bottom: PRAND replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47 |

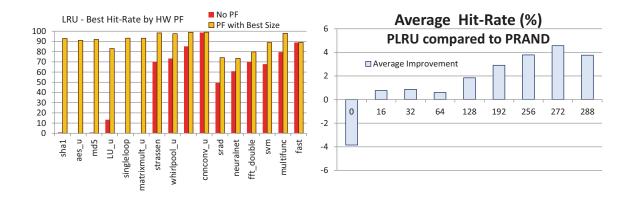

| 4.9  | The best hit-rate achieved by NLP (left), and average hit-rate improve-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | ment of prefetching compared between PLRU and PRAND (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48 |

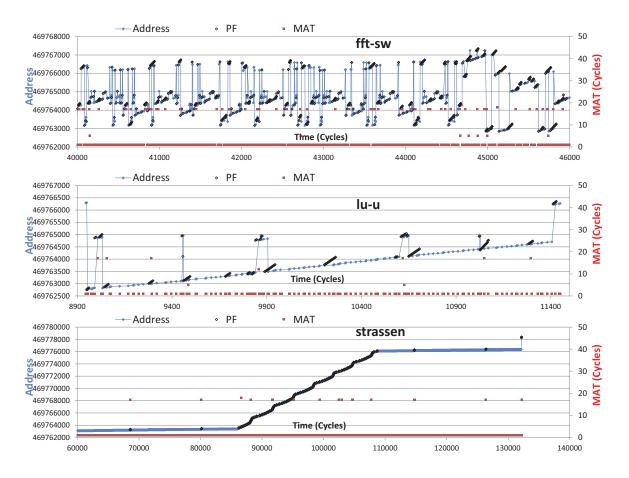

| 4.10 | The address plot of three benchmarks with PLRU replacement and NLP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | with size 256Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49 |

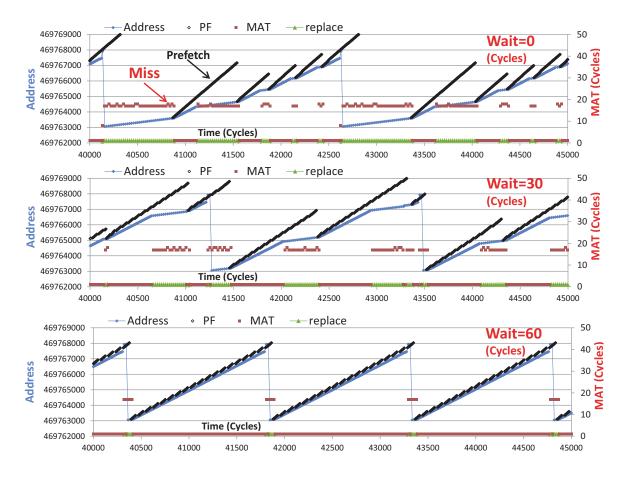

| 4.11 | Address plots for three cases of stream-prefetcher with burst-size of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | 256Bytes and wait-cycles of 0, 30, 60 (Cycles)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50 |

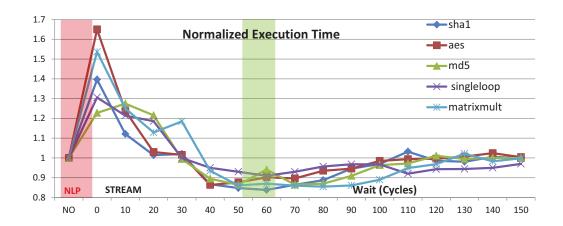

| 4.12 | The effect of wait-cycles in STP on the execution time of different bench-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51 |

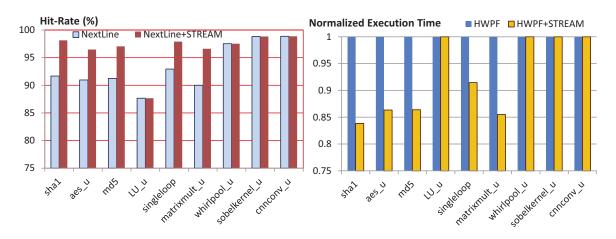

| 4.13 | The best hit-rate achieved by STP in comparison with NLP (left), and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      | the best execution time in the same experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51 |

| F 1  | Dancourte and of a surface of a |    |

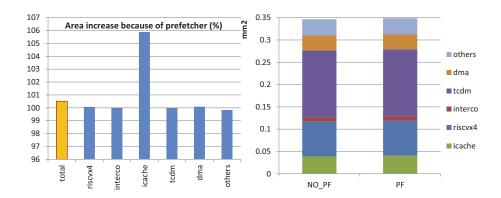

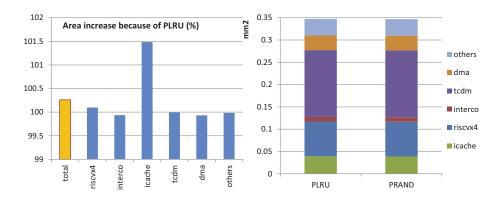

| 5.1  | Percentage of area increase due to the prefetcher (left), and average area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

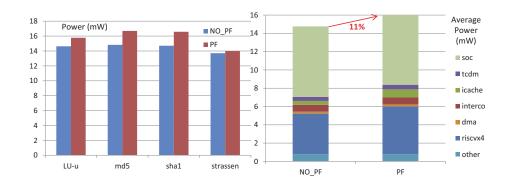

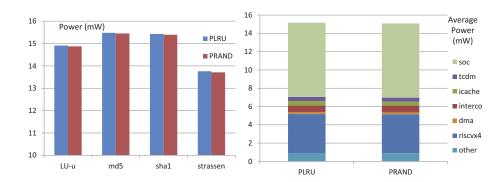

| 5.2  | breakdown in the cluster with/without prefetching (right) Total system power with/without prefetching for different benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55 |

| 9.4  | (left), average power break-down compared between the two cases (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54 |

| 5.3  | Percentage of area increase in PLRU compared to PRAND (left), and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54 |

| 5.5  | average area breakdown in the cluster with PLRU and PRAND (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54 |

| 5.4  | Total system power with PRAND/PLRU for different benchmarks (left),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 94 |

| IJ.¥ | average power break-down compared between the two cases (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55 |

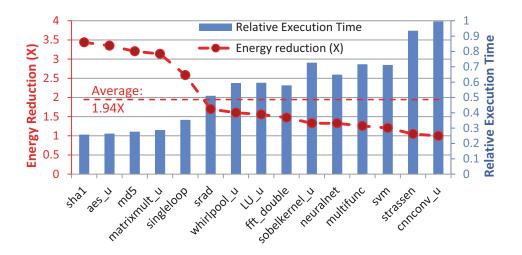

| 5.5  | Total energy reduction thanks to the proposed prefetching mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | JJ |

| 5.5  | (left-axis), relative execution time when prefetching is enabled (right-axis).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55 |

|      | (left-axis), relative execution time when prefetching is enabled (light-axis).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IJ |

# Chapter 1

## Introduction and Related Works