SCUOLA DI INGEGNERIA E ARCHITETTURA CON SEDE A CESENA CORSO DI LAUREA MAGISTRALE IN INGEGNERIA ELETTRONICA E TELECOMUNICAZIONI PER LO SVILUPPO SOSTENIBILE

# PROGETTO DI UN CONVERTITORE FULL-BRIDGE PHASE-SHIFTED ISOLATO A COMMUTAZIONE RISONANTE

Relatore: Presentata da: Prof. Rudi Paolo Paganelli Erik Casadei

Sessione I Appello I Anno Accademico 2015/2016 Parole chiave:

${\bf Full\text{-}Bridge}$

Phase-Shifted

Zero-Voltage-Switching

${\bf Current\text{-}Doubler}$

K-Factor

# Indice

| Introduzione                                            | 5  |

|---------------------------------------------------------|----|

| Specifiche in ingresso                                  | 6  |

| Descrizione della topologia di circuito scelta          | 9  |

| Schema elettrico del convertitore DC/DC                 | 0  |

| Modulazione Phase-Shifted                               | 1  |

| Switch di potenza in tecnologia GaN FET                 | 13 |

| GaN FET EPC2025                                         | 14 |

| Analisi di correnti e tensioni nel circuito 1           | 7  |

| Introduzione alla commutazione "Zero Voltage Switching" | 8  |

| Segnali di comando per gli switch                       | 9  |

| Analisi degli intervalli di funzionamento               | 21 |

| Intervallo $t_0 \div t_1$ - Powering                    | 22 |

| Intervallo $t_1 \div t_2$ - Quasi-Resonant Commutation  | 24 |

| Intervallo $t_2 \div t_3$ - Clamped zeroing             | 26 |

| Intervallo $t_3 \div t_4$ - Active zeroing              | 28 |

| Intervallo $t_4 \div t_5$ - Resonant commutation        | 30 |

| Intervallo $t_5 \div t_6$ - Passive regeneration        | 32 |

| Intervallo $t_6 \div t_7$ - Active regeneration         | 34 |

| Intervallo $t_7 \div t_8$ - Energing                    | 36 |

| Considerazioni                                          | 38 |

| Architetture di rettificatori a secondario                                       | 39  |

|----------------------------------------------------------------------------------|-----|

| Rettificatore con presa centrale                                                 | 40  |

| Rettificatore con tecnica Current Doubler                                        | 42  |

| Dimensionamenti                                                                  | 45  |

| Analisi dei casi limite                                                          | 45  |

| Dimensionamento del rapporto spire del trasformatore                             | 46  |

| Caduta di tensione sui dispositivi attivi del ponte intero                       | 46  |

| Specifiche sul Duty-Cycle del segnale di controllo del ponte intero              | 47  |

| Considerazioni sulla commutazione risonante                                      | 54  |

| Progetto dell'anello di retroazione per il convertitore                          | 57  |

| Anello di retroazione per la regolazione della tensione d'uscita                 | 57  |

| Modello ai piccoli segnali del convertitore                                      | 65  |

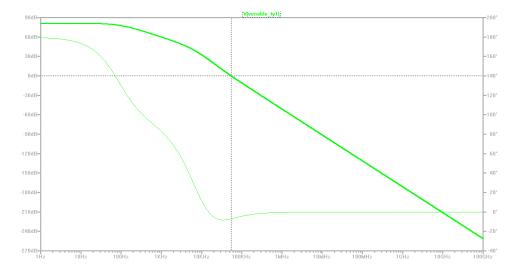

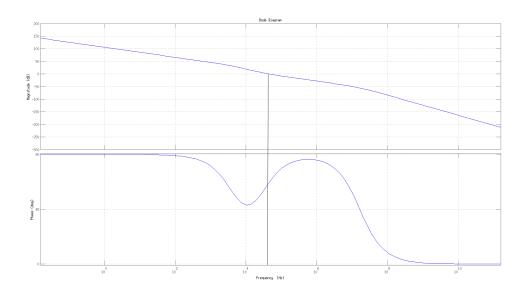

| Studio della funzione di trasferimento del convertitore                          | 68  |

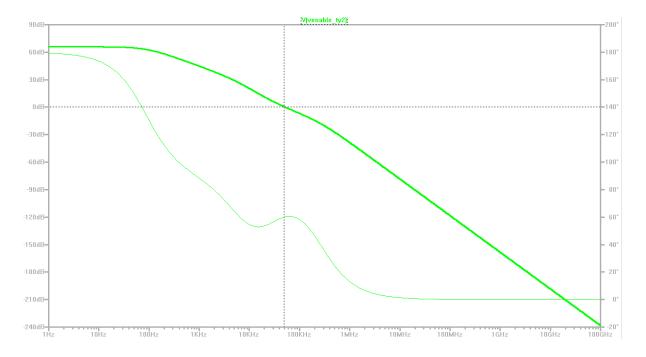

| Progetto dell'anello di retroazione in tensione mediante l'utilizzo del K Factor | 71  |

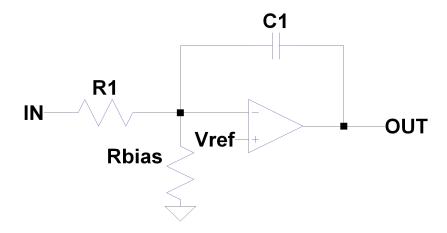

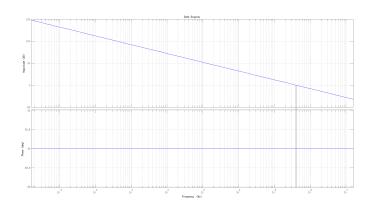

| Amplificatore di tipo 1                                                          | 74  |

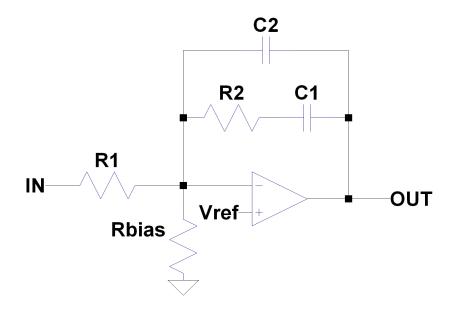

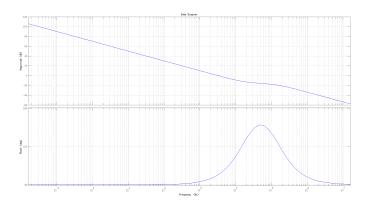

| Amplificatore di tipo 2                                                          | 75  |

| Fattore K                                                                        | 77  |

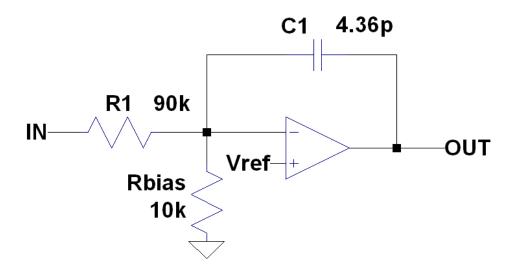

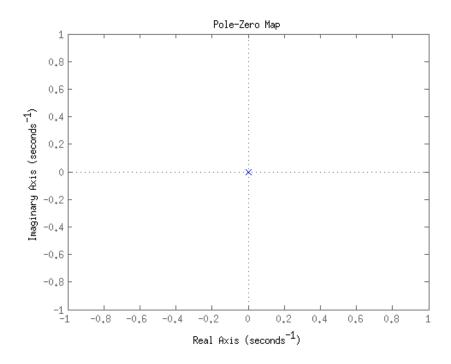

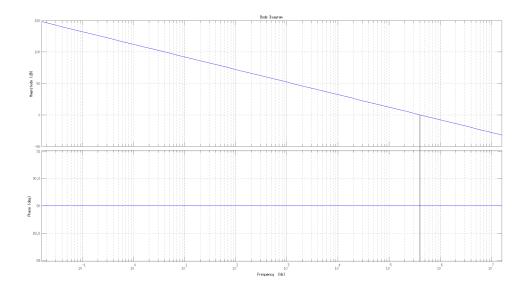

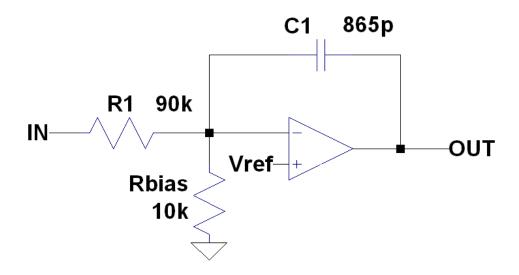

| Progetto della rete di amplificazione dell'errore di tipo 1                      | 78  |

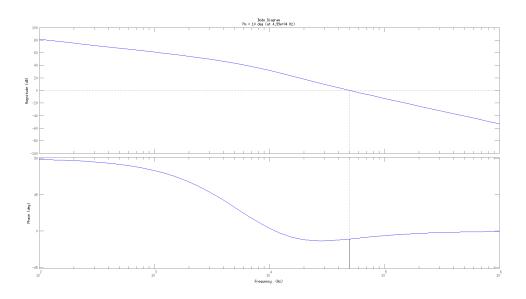

| Miglioramento della risposta d'anello con amplificatore d'errore di tipo 1       | 85  |

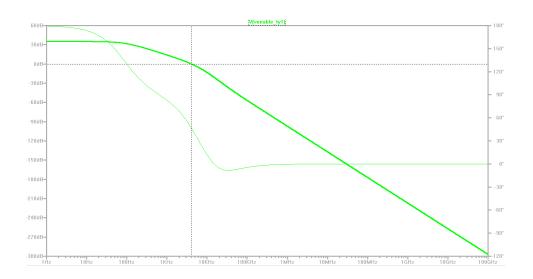

| Progetto della rete di amplificazione dell'errore di tipo 2                      | 93  |

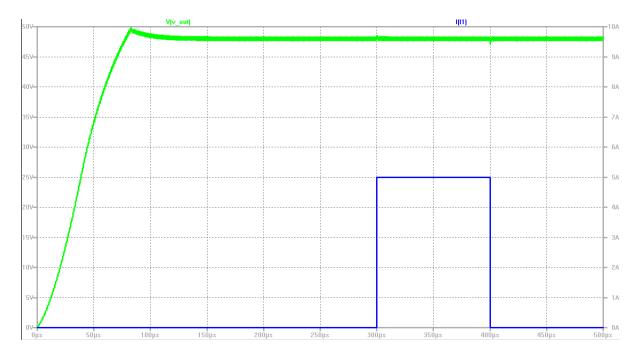

| Analisi delle prestazioni                                                        | 104 |

| Conclusioni                                                                      | 107 |

| Bibliografia                                                                     | 100 |

# Introduzione

L'evoluzione della tecnologia allo stato solido e il fiorire di nuove applicazioni determinano una forte spinta verso la miniaturizzazione dei convertitori elettronici di potenza. Questa riduzione di pesi ed ingombri è particolarmente sentita anche in quei convertitori di media potenza che necessitano di un trasformatore d'isolamento. In quest'ambito assume importante rilievo l'utilizzo di una architettura circuitale a ponte intero e di tecniche in grado di spingere la frequenza di commutazione il più in alto possibile.

Questa tesi si propone quindi di studiare a fondo il funzionamento dei convertitori DC/DC isolati di tipo Full-Bridge e pilotati con la tecnica di modulazione Phase-Shifted che ben si presta all'impiego di commutazioni risonanti del tipo Zero-Voltage-Switching. L'analisi teorica sarà corroborata da simulazioni condotte su LTspice e sarà orientata all'individuazione di una metodologia di progetto generale per questo tipo di convertitori.

Al fine di formalizzare meglio il progetto si è individuata una possibile applicazione nella alimentazione di un DC-bus per telecomunicazioni (48 Volt DC sostenuti da batterie) a partire da una fonte di energia fotovoltaica quale una stringa di pannelli operanti con tensioni variabili da 120 a 180 Volt DC.

Per questo particolare tipo di applicazione in discesa può avere senso l'impiego di un rettificatore del tipo a duplicazione di corrente, che quindi si provvederà a studiare e ad implementare a secondario del trasformatore d'isolamento.

Infine particolare cura sarà dedicata alla parte di controllo che si ha intenzione di integrare all'interno di LTspice così da riuscire simulare il comportamento dinamico del convertitore e verificare quanto predetto in via teorica mediante l'impiego della procedura che utilizza il K-Factor per la realizzazione della rete compensatrice.

#### Specifiche in ingresso

Ipotizziamo di alimentare il convertitore con una stringa di sei moduli fotovoltaici SHARP NU-180 (E1) collegati in serie. Il modulo fotovoltaico scelto, presenta le seguenti caratteristiche elettriche:

| SHARP NU-180 (E1)             |       |

|-------------------------------|-------|

| Potenza di picco              | 180W  |

| Tensione a circuito aperto    | 30V   |

| Corrente di corto circuito    | 8.37A |

| Tensione alla massima potenza | 23.7V |

| Corrente alla massima potenza | 7.6A  |

| Tensione massima di sistema   | 1000V |

Tabella 1: Caratteristiche elettriche del modulo fotovoltaico SHARP NU-180 (E1)

Scegliendo di collegare tutti i sei moduli della stringa in serie, è necessario verificare che non vengano violati i vincoli sulla tensione di ingresso al convertitore.

Nel funzionamento a circuito aperto, ogni modulo può fornire una tensione massima di 30V, che si traduce in una tensione di 180V per la stringa, da cui deriva una prima specifica progettuale.

In condizioni nominali di utilizzo, ovvero supponendo un perfetto irraggiamento solare, la massima potenza generata da ogni modulo è di 180W che si traduce in 1080W per l'intera stringa. Il valore della potenza di picco è ricavato moltiplicando il valore della tensione alla massima potenza e quello della corrente alla massima potenza. In particolare è utile ricavare il valore della tensione fornita della stringa in questa condizione di funzionamento.

$23,7V \cdot 6 = 142.2V_{dc}$  (Tensione fornita al convertitore alla massima potenza)

Analizzando il valore della corrente, essendo i moduli collegati in serie, essa è la medesima per tutti i moduli ed il suo valore è di 7.6A. Scegliendo di cablare una stringa formata dalle serie di sei moduli fotovoltaici, si è rispettato anche il vincolo fornito dal costruttore di non superare i 1000V come tensione di stringa.

Poichè da specifica la corrente di corto circuito vale 8.37A e ipotizzando che la caratteristica di potenza sia abbastanza piatta non ha troppo senso alimentare la stringa a tensioni troppo inferiori ai 130V; ammetteremo dunque che il DC/DC che si affaccia sul pannello possa operare fino a tensioni minime di 120V e con correnti massime di 8.5A, con una potenza di uscita  $P_{out}$  di 1020W.

Riassumendo, le specifiche sulle tensioni di ingresso e di uscita del convertitore sono:

- Range tensione in ingresso:  $120 \div 180 V_{dc}(142.2 V_{dc} \text{ nominali})$

- Range tensione di uscita:  $30 \div 60 V_{dc} (48 V_{dc} \text{ come tensione target})$

# Descrizione della topologia di circuito scelta

Per effettuare la trasformazione di tensione richiesta si è utilizzato un convertitore DC/DC di tipo a commutazione che utilizza dispositivi allo stato solido che funzionano come interruttori; poichè non si richiede a tali dispositivi di lavorare in zona attiva, questa modalità di funzionamento comporta una minore dissipazione di potenza permettendo al convertitore di operare con un elevato rendimento. Gli switch di potenza convertono la tensione di alimentazione continua in una tensione ad alta frequenza che alimenta il trasformatore di isolamento. L'uscita del secondario del trasformatore è raddrizzata e filtrata per produrre una tensione di uscita regolata attorno al valore scelto. L'uscita dell'alimentazione DC è regolata mediante un controllo ad anello chiuso che impiega un modulatore PWM che confronta la tensione di controllo con una rampa a dente di sega con periodo pari a quello di commutazione desiderato dal convertitore. Il segnale così generato viene poi elaborato da una logica digitale che fornisce in uscita una modulazione Phase-Shifted idonea a comandare gli switch di potenza del ponte intero sul DC-link in ingresso.

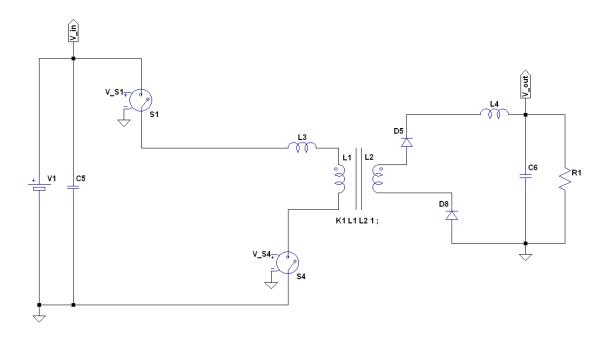

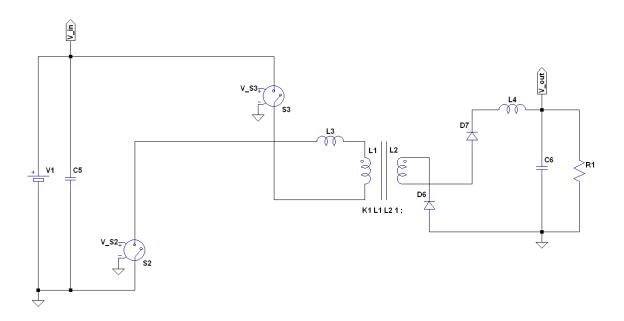

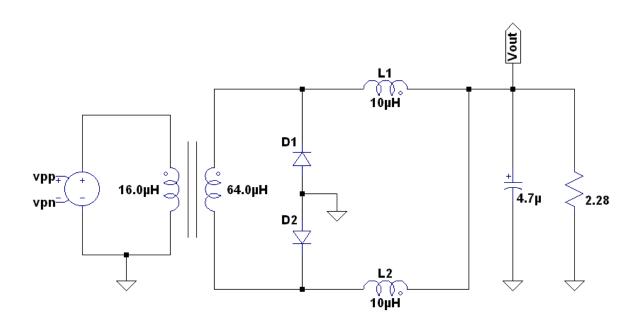

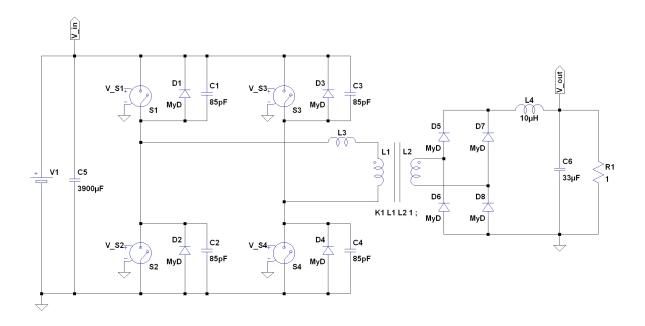

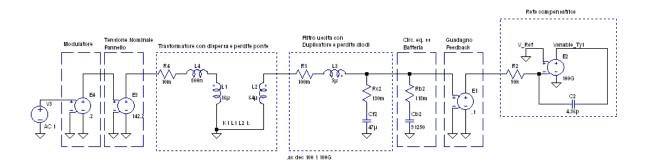

### Schema elettrico del convertitore DC/DC

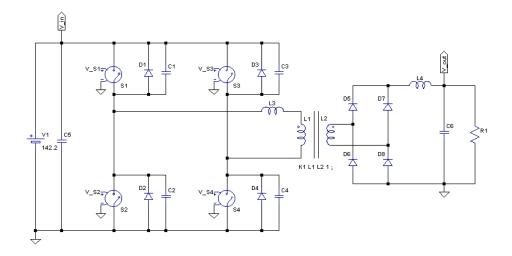

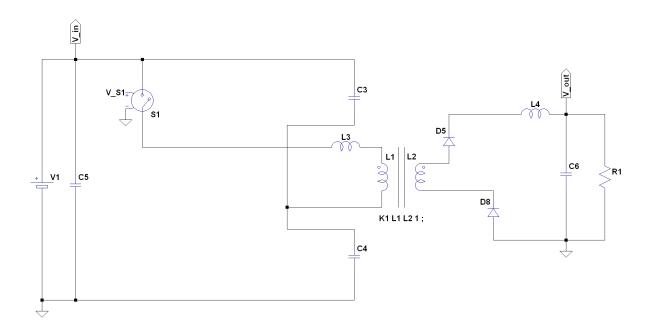

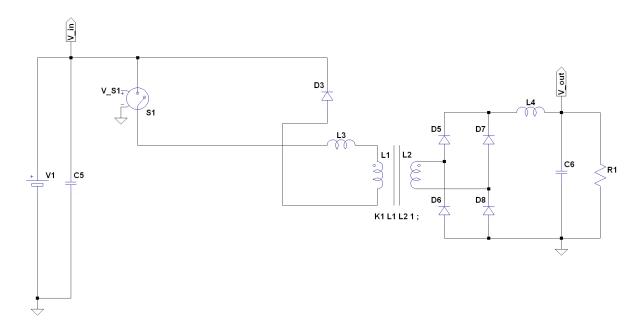

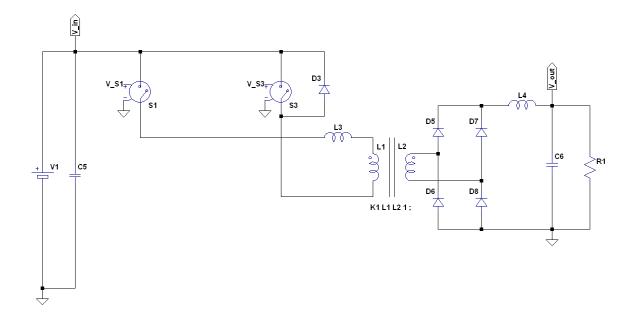

Figura 1: Schema elettrico del convertitore scelto

È possibile scomporre il circuito in macro-blocchi, ognuno caratterizzato da una specifica funzione. Subito a valle dei morsetti di alimentazione del convertitore, si trova la capacità  $C_5$  con funzione di filtro sulla corrente in ingresso. Proseguendo, troviamo il ponte intero, realizzato da quattro switch di potenza, ognuno dotato del proprio diodo in antiparallelo e della propria capacità di by-pass. Questa struttura, se opportunamente pilotata, è in grado di fornire ai capi dell'avvolgimento di primario del trasformatore una tensione alternata a tre valori  $(+V_{in}, 0, -V_{in})$  partendo dalla tensione continua in ingresso  $+V_{in}$ . Proseguendo verso l'uscita del convertitore, si trova il trasformatore di isolamento con a monte dell'avvolgimento di primario la reattanza di dispersione dello stesso che, come si vedrà, permette di creare una commutazione risonante a tensione nulla degli switch di potenza grazie anche alla presenza delle capacità di by-pass drain-source. A valle del trasformatore un ponte intero di diodi rettifica gli impulsi rettangolari di tensione rendendoli tutti positivi; il filtro LC seguente ha il compito di filtrare le armoniche superiori e ottenere in uscita il solo valore medio (DC), determinato dal duty-cycle degli impulsi rettangolari raddrizzati.

#### Modulazione Phase-Shifted

Il convertitore a ponte intero pilotato con modulazione phase-shifted è costituito da quattro switch di potenza che collegano l'avvolgimento di primario del trasformatore alla linea di alimentazione. Le condizioni di "ZVS" dei leg del ponte intero verranno realizzate mediante l'introduzione di un "dead-time" nei segnali di comando degli switch.

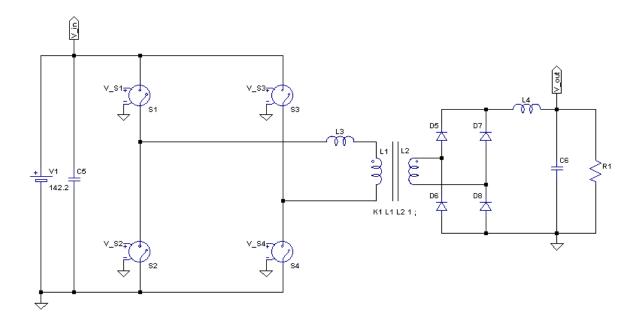

Figura 2: Schema elettrico della configurazione Phase-Shifted a ponte intero

Nella figura soprastante, è mostrata la configurazione a ponte intero con i quattro switch di potenza (S1, S2, S3 e S4) collegati all'avvolgimento di primario del trasformatore. I segnali di comando degli switch S1 ed S2 hanno un duty-cycle del 50% e sono sfasati di 180 gradi tra loro, quindi sono conduttivi per metà del periodo di commutazione in configurazione mutalmente esclusiva. Lo stesso avviene per il leg del convertitore composto dagli switch S3 e S4, ma in questo caso il segnale di commutazione PWM ha uno spostamento in fase rispetto al leg composto dagli switch S1 e S2. L'entità dello shift in fase controlla l'ammontare della sovrapposizione dei segnali che pilotano gli switch di una "diagonale" di conduzione del ponte, controllando di fatto la quantità di energia trasferita dall'alimentazione all'avvolgimento di primario del trasformatore. In questo

contesto, la componente dispersa del trasformatore e le capacità di uscita dei dispositivi possono essere messe in risonanza per realizzare una commutazione di tipo risonante e ZVS.

Figura 3: Il leg nella riga in alto determina l'inizio del  $T_{ON}$ , il leg della riga immediatamente sotto ne determina la fine; nell'ultima riga vengono mostrati gli andamenti della tensione e della corrente a primario. A sinistra è evidenziato l'effetto di uno spostamento in fase di media entità, a destra l'effetto di uno shift di maggiore entità che aumenta il duty-cycle del segnale.

Come mostrato nella figura soprastante, la quantità di energia prelevata dalla linea di alimentazione ed inviata all'avvolgimento di primario del trasformatore è regolata sulla base dello sfasamento presente tra le portanti con duty-cycle del 50% che pilotano i leg del ponte intero. È compito dell'anello di retroazione in tensione, agire sullo sfasamento di tali segnali per fornire in uscita la tensione desiderata.

#### Switch di potenza in tecnologia GaN FET

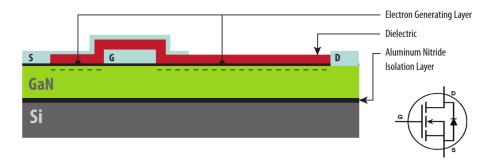

I GaN FET appartengono alla famiglia dei transistori ad effetto di campo e sono basati su una tecnologia a nitruro di gallio con un utilizzo molto simile ai power mosfet ma con efficienza superiore. Sono costruiti su un substrato basato su un wafer di silicio sul quale viene depositato un sottile strato di nitruro di allumino che serve ad isolare il dispositivo che crescerà sugli strati superiori dal silicio. Viene poi depositato superiormente, uno strato altamente resistivo di nitruro di gallio che sarà la base per la costruzione del transistor GaN. La composizione della struttura produce un accumulo di carica all'interfaccia del dispositivo che viene poi gestita dal transistor mediante i tre terminali di Gate, Drain e Source, realizzati depositando strati di metallo. La struttura di base viene poi replicata tante volte sullo stesso wafer e grazie a delle connessioni tra i terminali dei singoli dispositivi è possibile ottenere un dispositivo di potenza.

Figura 4: Struttura del transistor GaN

Per ottenere dispositivi capaci di operare a tensione elevata, la distanza tra le metallizzazioni di Drain e Gate viene aumentata rispetto alla tecnologia al silicio; data l'elevata presenza di elettroni all'interfaccia, si ottiene comunque un valore di resistività del canale più basso rispetto ai dispositivi in silicio di taglia corrispondente.

Fornendo una tensione positiva al terminale di Gate, utilizzando il terminale di Source come riferimento, si crea un campo elettrico che attira elettroni a ridosso del Gate, creando un canale conduttivo tra i terminali di Drain e Source. Allo stesso modo, rimuovendo la tensione al Gate, gli elettroni che si erano accumulati sotto di esso si disperdono e viene a formarsi quindi la cosiddetta regione svuotata.

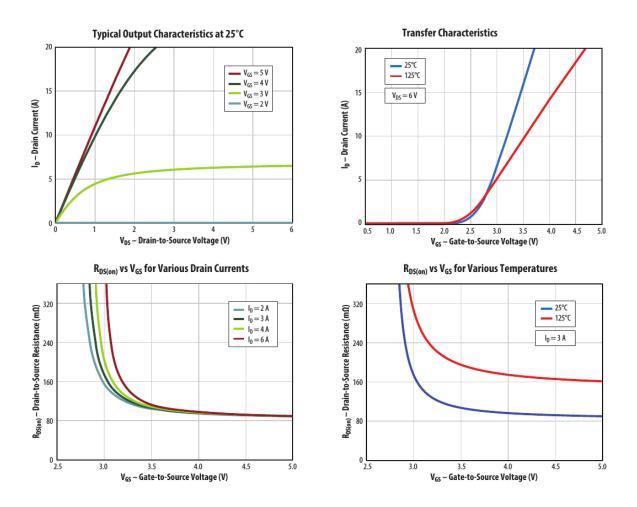

#### GaN FET EPC2025

Il dispositivo scelto per la realizzazione del ponte intero del convertitore DC/DC è l'EPC2025 che, come mostrato in seguito nel data-sheet, è appositamente sviluppato per applicazioni in convertitori ad alta frequenza grazie a degli ottimi punti di merito per quanto riguarda l'efficienza e le perdite di commutazione e conduzione.

|                   | Maximum Ratings                                                 |            |    |  |

|-------------------|-----------------------------------------------------------------|------------|----|--|

| V <sub>DS</sub>   | Drain-to-Source Voltage (Continuous)                            | 300        | V  |  |

| _                 | Continuous $(T_A = 25^{\circ}C, R_{\Theta JA} = 13^{\circ}C/W)$ | 6.3        | Δ  |  |

| (I <sub>D</sub> ) | Pulsed (25°C, $T_{PULSE} = 300 \mu s$ )                         | 20         | A  |  |

| V                 | Gate-to-Source Voltage                                          | 6          | V  |  |

| V <sub>GS</sub>   | Gate-to-Source Voltage                                          | -4         | V  |  |

| T,                | Operating Temperature                                           | -40 to 150 | °C |  |

| T <sub>STG</sub>  | Storage Temperature                                             | -40 to 150 | C  |  |

Figura 5: Estratto dal Data-sheet GaN FET EPC2025

Nella tabella appena proposta, sono mostrate le caratteristiche di potenza del dispositivo, evidenziando la massima tensione e la massima corrente che il dispositivo può gestire; in particolare, per quanto riguarda la corrente, si nota come sia possibile aumentare il limite massimo di circa 3 volte nel caso di uso impulsivo.

|                     | Static Characteristics (T <sub>1</sub> = 25°C unless otherwise stated) |                                                |     |     |     |      |

|---------------------|------------------------------------------------------------------------|------------------------------------------------|-----|-----|-----|------|

|                     | PARAMETER                                                              | TEST CONDITIONS                                | MIN | TYP | MAX | UNIT |

| BV <sub>DSS</sub>   | Drain-to-Source Voltage                                                | $V_{GS}=0~V,~I_D=120~\mu A$                    | 300 |     |     | V    |

| I <sub>DSS</sub>    | Drain Source Leakage                                                   | $V_{DS} = 240 \text{ V}, V_{GS} = 0 \text{ V}$ |     | 20  | 100 | μΑ   |

|                     | Gate-to-Source Forward Leakage                                         | $V_{GS} = 5 \text{ V}$                         |     | 0.1 | 2   | mA   |

| I <sub>GSS</sub>    | Gate-to-Source Reverse Leakage                                         | $V_{GS} = -4 V$                                |     | 20  | 100 | μΑ   |

| $V_{GS[TH]}$        | Gate Threshold Voltage                                                 | $V_{DS} = V_{GS},  I_D = 1  mA$                | 0.8 | 1.4 | 2.5 | ٧    |

| R <sub>DS(on)</sub> | Drain-Source On Resistance                                             | $V_{GS} = 5 \text{ V}, I_D = 3 \text{ A}$      |     | 90  | 120 | mΩ   |

| V <sub>SD</sub>     | Source-Drain Forward Voltage                                           | $I_s = 0.5 \text{ A}, V_{GS} = 0 \text{ V}$    |     | 2.5 |     | ٧    |

Figura 6: Estratto dal Data-sheet GaN FET EPC2025

Dalla tabella precedente si vede che la  $R_{ds_{ON}}$  di caso peggiore vale  $120m\Omega$ ; se tale valore appare molto buono tenuto conto della densità di corrente e della  $V_{gs_{ON}}$  applicata si deve però notare che invece la caduta di tensione sul diodo di Body, attivo per correnti di drain negative, è 2.5V, valore piuttosto alto che consiglia l'utilizzo di rettificazione sincrona.

| <b>Dynamic Characteristics</b> (T <sub>j</sub> = 25°C unless otherwise stated) |                                                         |                                                                                                                                                                        |     |                                                       |      |      |

|--------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------|------|------|

|                                                                                | PARAMETER                                               | TEST CONDITIONS                                                                                                                                                        | MIN | TYP                                                   | MAX  | UNIT |

| C <sub>ISS</sub>                                                               | Input Capacitance                                       |                                                                                                                                                                        |     | 200                                                   | 240  |      |

| C <sub>RSS</sub>                                                               | Reverse Transfer Capacitance                            | $V_{DS} = 240 \text{ V}, V_{GS} = 0 \text{ V}$                                                                                                                         |     | 0.1                                                   |      | ]    |

| Coss                                                                           | Output Capacitance                                      |                                                                                                                                                                        |     | 46                                                    | 70   | ] _  |

| C <sub>OSS(ER)</sub>                                                           | Effective Output Capacitance<br>Energy Related (Note 2) | V 04c 240 V V 0 V                                                                                                                                                      |     |                                                       |      | pF   |

| C <sub>OSS(TR)</sub>                                                           | Effective Output Capacitance<br>Energy Related (Note 3) | $V_{DS} = 0$ to 240 V, $V_{GS} = 0$ V                                                                                                                                  |     | 93                                                    |      |      |

| R <sub>G</sub>                                                                 | Gate Resistance                                         |                                                                                                                                                                        |     | 0.3                                                   |      | Ω    |

| $Q_{G}$                                                                        | Total Gate Charge                                       | $V_{DS} = 240 \text{ V}, V_{GS} = 5 \text{ V}, I_{D} = 3 \text{ A}$                                                                                                    |     | 1.8                                                   | 2.3  |      |

| $Q_{GS}$                                                                       | Gate-to-Source Charge                                   | $V_{DS} = 240 \text{ V, } I_D = 3 \text{ A} \\ \hline 0.32 \\ \hline 0.54 \\ \hline V_{DS} = 240 \text{ V, } V_{GS} = 0 \text{ V} \\ \hline 22 \\ \hline 33 \\ \hline$ |     |                                                       | 1    |      |

| $Q_{GD}$                                                                       | Gate-to-Drain Charge                                    |                                                                                                                                                                        |     | $V_{DS} = 240 \text{ V}, I_D = 3 \text{ A}$ 0.32 0.54 | nC   |      |

| $Q_{G(TH)}$                                                                    | Gate Charge at Threshold                                |                                                                                                                                                                        |     |                                                       | l nc |      |

| Qoss                                                                           | Output Charge                                           |                                                                                                                                                                        |     | 33                                                    | 1    |      |

| $Q_{RR}$                                                                       | Source-Drain Recovery Charge                            |                                                                                                                                                                        |     | 0                                                     |      |      |

Figura 7: Estratto dal Data-sheet GaN FET EPC2025

Il valore della capacità di uscita del dispositivo evidenziato nell'immagine precedente equivale al valore della capacità Drain-Source e sarà utile in seguito nel dimensionamento dell'induttanza di dispersione del trasformatore e per lo studio delle commutazioni risonanti. Infine, vengono riportati dei grafici che mettono in relazione alcune importanti grandezze che riguardano i transitor di potenza; come si può notare, sono del tutto simili a quelli relativi a transistor in tecnologia MOS FET: l'unica differenza riguarda la tensione di pilotaggio al Gate che non può eccedere i 5V.

Figura 8: Estratto dal Data-sheet GaN FET EPC2025

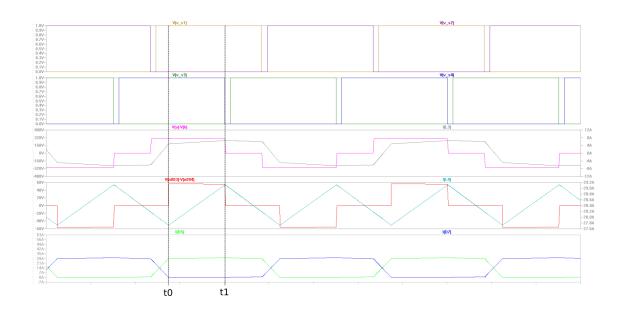

# Analisi di correnti e tensioni nel circuito

Per analizzare le forme d'onda di corrente e tensione nei vari nodi del circuito, si divide il periodo di commutazione in slot temporali, ognuno dei quali identifica un determinato regime di funzionamento caratterizzato dalle proprie forme d'onda. In particolare, è stata scelta una frequenza di commutazione per i dispositivi attivi del ponte intero di 500kHz che corrisponde ad un periodo di commutazione di  $2\mu s$ . All' interno del periodo di commutazione si distingueranno 16 fasi di funzionamento che si susseguono e ripetono ciclicamente ed iniziano e terminano in seguito all'evoluzione dello stato dei segnali di comando e in base al valore di alcuni parametri interni al circuito.

# Introduzione alla commutazione "Zero Voltage Switching"

Le commutazioni dei dispositivi attivi avvengono in condizioni "Zero Voltage Switching" (ZVS) o "Soft Turn On" in modo tale da facilitare la commutazione stessa, riducendo notevolmente le perdite di potenza e sfruttando in maniera vantaggiosa la presenza di elementi parassiti tipici di tali dispositivi, come il body diode e la capacita Drain-Source ( $C_{ds}$ ) che permettono di generare una commutazione dolce. Infatti, la combinazione delle capacità parassite degli switch di un leg, unite con l'induttanza dispersa del trasformatore, formano un bipolo risonante, che permette di avere una tensione nulla ai capi dello switch prima della sua accensione, eliminando quindi le dissipazioni di potenza dovute alla simultanea sovrapposizione di elevati valori di corrente e tensione durante la fase di accensione.

#### Segnali di comando per gli switch

Nelle fasi di energizzazione, i dispositivi attivi vengono azionati in configurazione diagonale, collegando alternativamente il primario del trasformatore alla tensione  $+V_{in}$  e  $-V_{in}$ . Viene trasferita potenza sul secondario del trasformatore unicamente durante queste fasi corrispondenti ad uno specifico duty-cycle per l'azionamento a frequenza fissa. Viene inserito un ritardo tra la commutazione di un leg e l'accensione del leg complementare in linea con le caratteristiche del phase shifted.

Nota: In particolare, il ritardo è inserito tra lo spegnimento del leg che sta terminando la fase attiva di trasferimento energetico del trasformatore e la commutazione dell'altro leg che dovrà anch'esso iniziare una fase attiva di energizzazione. All'interno di questo ritardo, si svuluppa la fase passiva di ricircolo dell'energia a primario.

Come conseguenza del ritardo, si ha che l'effettivo duty-cycle della forma d'onda a primario del trasformatore viene regolato dallo shift in fase tra i segnali di comando degli switch. Si delineano in questo modo due fasi principali di funzionamento, ovvero, una di energizzazione, dove l'energia prelevata dall'alimentazione viene fornita al carico e una di ricircolo, dove non vi é una diagonale di switch in conduzione, ma saranno accesi solo gli switch collegati ad uno dei terminali dell'alimentazione, cortocircuitando quindi il primario del trasformatore. Gli switch possono essere mantenuti nello stato di ricircolo per un certo periodo temporale che corrisponde all'off time desiderato per un particolare ciclo di commutazione. Inserendo un opportuno intervallo di "blanking time" per ciascuno dei due leg in fase di commutazione, la corrente di primario scorre attraverso la capacità parassita associata al nodo di uscita del leg (pari al parallelo delle due capacità di uscita dei dispositivi che costituiscono il leg), facendo risonare le tensioni Drain-Source al valore opposto tra i due livelli della tensione di alimentazione, creando i presupposti per un'accensione Zero Voltage Switching sugli switch opposti dello stesso leg. È importante sottolineare la profonda differenza tra la commutazione del leg che interrompe la fase di powering, idenficato come leg "forte" e il leg che inizia la nuova fase di energizzazione, identificato come leg "debole" (entrambe le commutazioni sono risonanti).

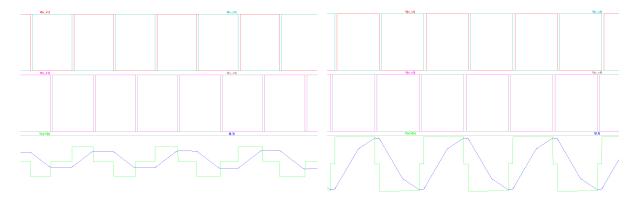

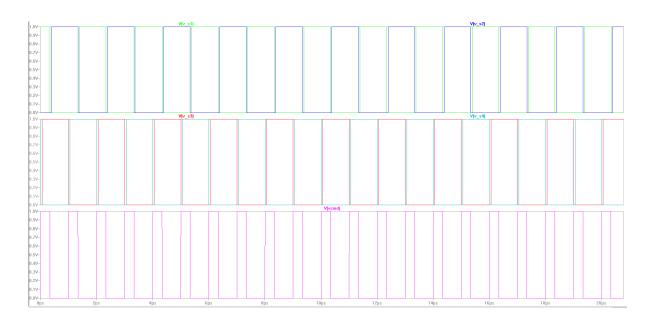

Figura 9: Forme d'onda dei segnali di comando degli switch

#### Analisi degli intervalli di funzionamento

Un singolo periodo di commutazione viene diviso in 16 slot temporali, ognuno caratterizzato da specifiche condizioni, che scandiscono il funzionamento del convertitore. Di seguito, viene riportato in dettaglio il funzionamento dei primi 8 slot temporali, riferiti al semiperiodo positivo della forma d'onda applicata all'avvolgimento di primario del trasformatore caratterizzate da un valore positivo della corrente. Il funzionamento degli 8 otto slot relativi al semiperiodo negativo è duale a quello riportato.

| # | Slot temporale | Nome intervallo              | Dispositivi in conduzione             |

|---|----------------|------------------------------|---------------------------------------|

| 1 | $t_0 \div t_1$ | POWERING +                   | S1, S4 (diagonale); D5, D8            |

| 2 | $t_1 \div t_2$ | Commutazione quasi risonante | S1, $C_{LegForte}$ ; D5, D8           |

| 3 | $t_2 \div t_3$ | Ricircolo passivo            | S1, D3; D5, D8 e D6 D7                |

| 4 | $t_3 \div t_4$ | RICIRCOLO ATTIVO +           | S1, S3; D5, D8 e D6, D7               |

| 5 | $t_4 \div t_5$ | Commutazione risonante       | $C_{LegDebole}$ , S3; D5, D8 e D6, D7 |

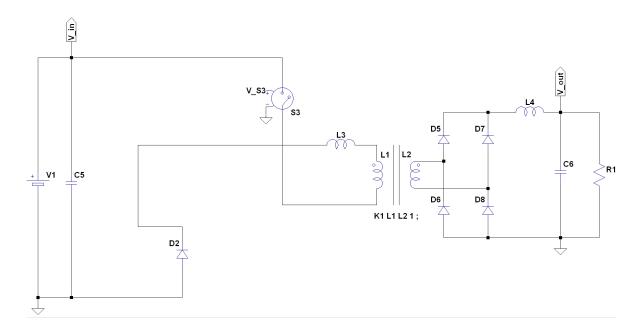

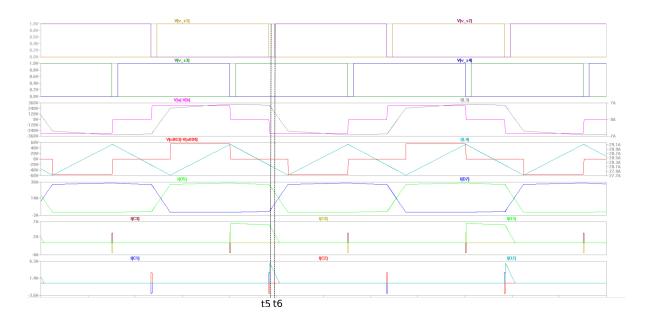

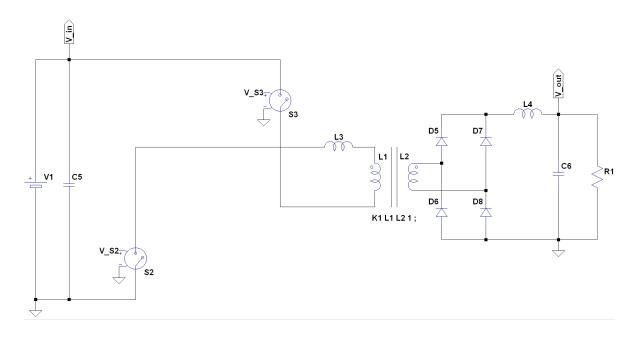

| 6 | $t_5 \div t_6$ | Rigenerazione passiva        | D2, S3; D5, D8 e D6, D7               |

| 7 | $t_6 \div t_7$ | Rigenerazione attiva         | S2, S3; D5, D8 e D6, D7               |

| 8 | $t_7 \div t_8$ | Energizzazione               | S2, S3; D5, D8 e D6, D7               |

Tabella 2: Divisione in slot temporali del semiperiodo positivo della forma d'onda in ingresso all'avvolgimento di primario del trasformatore

## Intervallo $t_0 \div t_1$ - Powering

Iniziamo la trattazione dall'intervallo in cui il trasformatore riceve potenza a primario e la eroga al rettificatore d'uscita alimentando il filtro che precede il carico. In questa fase sta quindi agendo la diagonale positiva (S1 ed S4 attivi) e con il rettificatore d'uscita anch'esso con la diagonale principale attiva (D5 e D8). La corrente sul filtro d'uscita  $I(L_4)$  cresce, altrettanto fa la corrente magnetizzante e, per conseguenza, la corrente a primario. Si tratta quindi di un intervallo energizzante, in quanto l'energia assorbita dal carico viene fornita dall'alimentazione.

Figura 10: Intervallo  $t_0 \div t_1$

Figura 11: Forme d'onda nell'intervallo  $t_0 \div t_1$

La corrente a primario,  $I(L_3)$ , continua a crescere con una pendenza che è data da  $I(L_4) \cdot \frac{N_{pri}}{N_{sec}}$  sommata ad una "piccola" quantità che è data dalla componente di corrente magnetizzante del trasformatore, mentre  $I(L_4)$ , anch'essa crescente, raggiunge il picco massimo del transitorio di salita per  $t=t_1$ , dove avviene lo spegnimento dello switch S4, pertinente al leg forte che da l'avvio all'intervallo successivo.

| Stato del ponte a primario            | S1 ed S4 ON, ogni altro elemento è interdetto |

|---------------------------------------|-----------------------------------------------|

| Stato del rettificatore a secondario  | D5 e D8 ON, ogni altro elemento è interdetto  |

| Corrente sul filtro d'uscita $I(L_4)$ | Positiva, crescente                           |

| Corrente magnetizzante                | Positiva, crescente                           |

| Considerazioni energetiche            | Transitorio energizzante, la potenza fluisce  |

|                                       | dalla sorgente al carico                      |

| Durata                                | STAZIONARIO: modulabile a piacere             |

Tabella 3: Riassunto sullo stato del circuito nell'intervallo considerato

#### Intervallo $t_1 \div t_2$ - Quasi-Resonant Commutation

Allo spegnimento di S4, la capacità  $C_{ds4}$  (C4) inizia a caricarsi, mentre,  $C_{ds3}$  (C3) si scarica, creando così i presupposti per l'accensione "ZVS" di S3; si noti che il ramo con i dispositivi S3 ed S4 è quello che pone termine alla fase di Powering. In questa fase non si attinge energia dalla sorgente in quanto non è percorsa da alcuna corrente (a parte la trascurabile corrente che scorre sul by-pass che deve caricare C4). Questa commutazione avviene a corrente praticamente costante e pari a quella di primario un istante prima dello spegnimento di S4, perchè si tratta di una commutazione quasi-risonante, ovvero un circuito LC in cui la L (dominante) è data dalla serie della reattanza di dispersione e il parallelo della reattanza magnetizzante e dell'induttanza di uscita riportata a primario, mentre C è il parallelo delle due capacità di uscita  $C_{OSS}$  dei dispositivi che commutano (considerando le capacità di bypass del leg e la capacità del filtro d'uscita come cortocircuiti). Al termine del transitorio di carica (per C4) e scarica (per C3) delle capacità Drain-Source, avviene l'entrata in conduzione del diodo D3 che fissa la tensione di uscita e determina il termine di questa fase.

Figura 12: Intervallo  $t_1 \div t_2$

Figura 13: Forme d'onda nell'intervallo  $t_1 \div t_2$

| Stato del ponte a primario            | S1, C3 e C4 ON, ogni altro elemento è interdetto            |

|---------------------------------------|-------------------------------------------------------------|

| Stato del rettificatore a secondario  | D5 e D8 ON, ogni altro elemento è interdetto                |

| Corrente sul filtro d'uscita $I(L_4)$ | Positiva, costante                                          |

| Corrente magnetizzante                | Positiva, costante                                          |

| Considerazioni energetiche            | Transitorio di commutazione (ricircolo a primario)          |

| Durata                                | DINAMICO: tipicamente inferiore a $\frac{1}{4}$ del periodo |

|                                       | naturale del risonatore                                     |

Tabella 4: Riassunto sullo stato del circuito nell'intervallo considerato

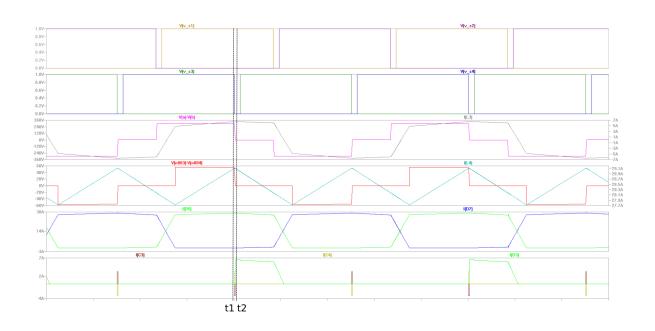

#### Intervallo $t_2 \div t_3$ - Clamped zeroing

Con l'entrata in conduzione del diodo D3, la tensione a primario si è definitivamente annullata e di conseguenza, anche la tensione riflessa a secondario è nulla. Questo determina una tensione negativa ai capi dell'induttanza di filtro di uscita L4, la cui corrente comincia a calare e una tensione nulla sull'induttanza magnetizzante che rimane costante. La corrente  $I(L_3)$  inizia quindi a diminuire leggermente, rispecchiando quanto avviene a secondario, a meno della componente magnetizzante. A secondario, l'energia viene fornita al carico dal filtro di uscita, grazie alla conduzione dei diodi D5 e D8 che erano in conduzione e continuano ad esserlo; tuttavia anche i diodi D6 e D7 vengono a polarizzarsi alla soglia di conduzione e, anzi, iniziano a condurre la parte di corrente imposta dal filtro di uscita L4 che non riesce a fluire dal primario poichè il valore nullo della tensione a primario avviene per differenza fra la tensione sulla componente dispersa e quella riflessa dal secondario che deve necessariamente essere positiva per colpa delle soglie dei diodi rettificatori.

Figura 14: Intervallo  $t_2 \div t_3$

Ci si trova dunque nella situazione in cui tutti i dispositivi del ponte di uscita sono attivi, la corrente magnetizzante è ancora leggermente in salita, la corrente di ingresso

è in discesa, così come pure la corrente sul filtro di uscita, seppure in maniera meno accentuata.

Figura 15: Forme d'onda nell'intervallo  $t_2 \div t_3$

| Stato del ponte a primario            | S1 e D3 ON, ogni altro elemento è interdetto |

|---------------------------------------|----------------------------------------------|

| Stato del rettificatore a secondario  | D5, D6, D7 e D8 ON                           |

| Corrente sul filtro d'uscita $I(L_4)$ | Positiva, decrescente                        |

| Corrente magnetizzante                | Positiva, debolmente crescente               |

| Considerazioni energetiche            | Transitorio di ricircolo a primario          |

| Durata                                | STAZIONARIO: la più breve possibile          |

Tabella 5: Riassunto sullo stato del circuito nell'intervallo considerato

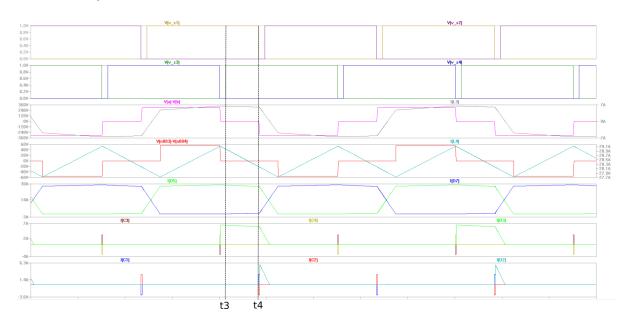

#### Intervallo $t_3 \div t_4$ - Active zeroing

Con l'accensione di S3 in ZVS grazie all'introduzione dell'opportuno blanking-time che consente di completare la commutazione del nodo in tutte le possibili condizioni nominali previste, si avvia il nuovo intervallo che sostanzialmente non differisce dal precedente in cui conduceva il diodo: la corrente a primario circola attraverso S1 e S3 (dal Source al Drain) e continua la fase di ricircolo della corrente a primario con una tensione applicata pressochè nulla (se gli switch di potenza avessero la stessa  $R_{ds_{ON}}$  sarebbe esattamente nulla).

Figura 16: Intervallo  $t_3 \div t_4$

La corrente  $I(L_4)$  continua a decrescere perchè l'induttore si vede applicata una tensione negativa pari alla  $V_{out}$ . Sul ponte raddrizzatore a secondario tutti i diodi sono in conduzione e al secondario è applicata una tensione teoricamente nulla ma, in realtà, leggermente positiva a causa della dissimmetria fra le cadute sui diodi. Questa tensione leggermente positiva viene riflessa a primario e produce un leggerissimo aumento della corrente magnetizzante (che sostanzialmente si mantiene costante) e l'applicazione di una tensione negativa sulla componente dispersa di ingresso L3 che dunque vede un calo

relativo assai più accentuato di quanto non avvenga per L4 (quest'ultima osservazione è perfettamente compatibile con l'andata in conduzione di tutti i dispositivi del ponte rettificatore).

Figura 17: Forme d'onda nell'intervallo  $t_3 \div t_4$

| Stato del ponte a primario            | S1 e S3 ON, ogni altro elemento è interdetto |

|---------------------------------------|----------------------------------------------|

| Stato del rettificatore a secondario  | D5, D6, D7 e D8 ON                           |

| Corrente sul filtro d'uscita $I(L_4)$ | Positiva, decrescente                        |

| Corrente magnetizzante                | Positiva, costante                           |

| Considerazioni energetiche            | Transitorio di ricircolo a primario          |

| Durata                                | STAZIONARIO: modulabile a piacere            |

Tabella 6: Riassunto sullo stato del circuito nell'intervallo considerato

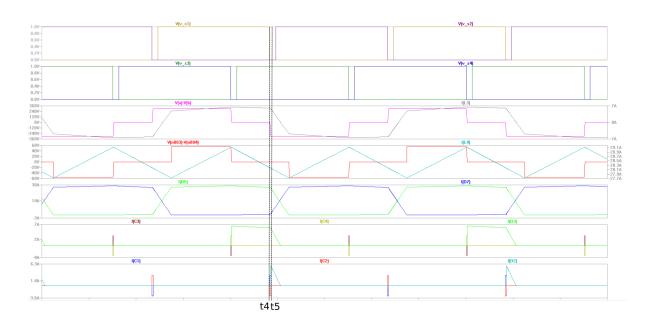

## Intervallo $t_4 \div t_5$ - Resonant commutation

Allo spegnimento di S1, il circuito si semplifica come mostrato nella figura sottostante, dando avvio alla commutazione risonante. Questa fase è caratterizzata da un transitorio di carica della capacità C1 e da uno di scarica della capacità C2 che pone le condizioni necessarie per un accensione "ZVS" di S2. Ammesso che vi sia energia a sufficienza per completare la transizione, ovvero la scarica completa del condensatore C2 (e la carica completa del condensatore C1), la fase termina con l'entrata in conduzione del diodo D2.

Figura 18: Intervallo  $t_4 \div t_5$

Figura 19: Forme d'onda nell'intervallo  $t_4 \div t_5$

| Stato del ponte a primario            | C1, C2, D2, D3 e S3 ON, ogni altro elemento         |

|---------------------------------------|-----------------------------------------------------|

|                                       | è interdetto                                        |

| Stato del rettificatore a secondario  | D5, D6, D7 e D8 ON                                  |

| Corrente sul filtro d'uscita $I(L_4)$ | Positiva, decrescente                               |

| Corrente magnetizzante                | Positiva, decrescente                               |

| Considerazioni energetiche            | Transitorio di ricircolo a primario                 |

| Durata                                | DINAMICO: tipicamente inferiore a $\frac{1}{4}$ del |

|                                       | periodo naturale del risonatore                     |

Tabella 7: Riassunto sullo stato del circuito nell'intervallo considerato

# Intervallo $t_5 \div t_6$ - Passive regeneration

Durante la fase rigenerativa passiva, la tensione a primario è pari a  $-V_{in}$  e la corrente di primario è in rapidissima decrescita. Questa fase termina con l'accensione dello switch di potenza S2 che deve avvenire non troppo presto da non consentire la commutazione del nodo e non troppo tardi, ovvero dopo l'inversione della corrente a primario che il diodo D2 non è in grado di gestire.

Figura 20: Intervallo  $t_5 \div t_6$

Figura 21: Forme d'onda nell'intervallo  $t_5 \div t_6$

| Stato del ponte a primario            | D2 e S3 ON, ogni altro elemento è interdetto |

|---------------------------------------|----------------------------------------------|

| Stato del rettificatore a secondario  | D5, D6, D7 e D8 ON                           |

| Corrente sul filtro d'uscita $I(L_4)$ | Positiva, decrescente                        |

| Corrente magnetizzante                | Positiva, decrescente                        |

| Considerazioni energetiche            | Transitorio di ricircolo a primario          |

| Durata                                | DINAMICA: la più breve possibile             |

Tabella 8: Riassunto sullo stato del circuito nell'intervallo considerato

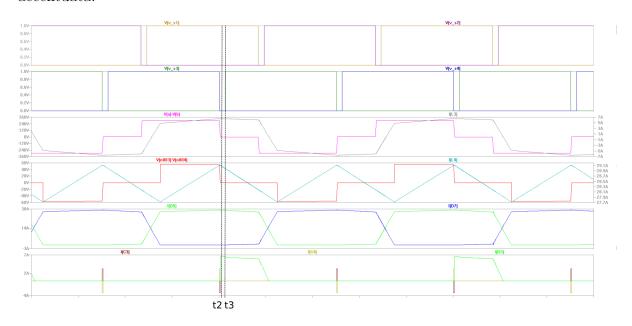

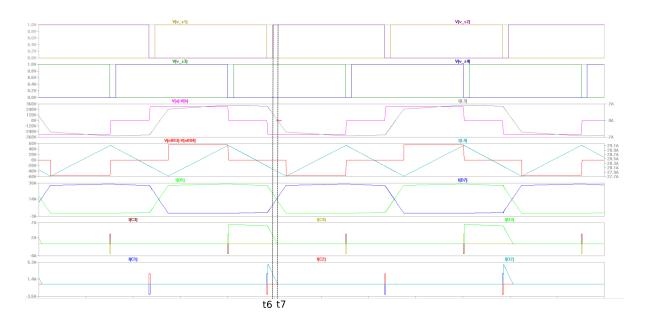

## Intervallo $t_6 \div t_7$ - Active regeneration

La fase rigenerativa attiva inizia con l'accensione dello switch di potenza S2 e la tensione applicata a primario è sempre pari a  $-V_{in}$ . La corrente di primario è in rapidissima decrescita. Durante questa fase avviene l'inversione della corrente a primario ed è proprio questo l'istante di inizio del nuovo intervallo.

Figura 22: Intervallo  $t_6 \div t_7$

Figura 23: Forme d'onda nell'intervallo  $t_6 \div t_7$

| Stato del ponte a primario            | S2 e S3 ON, ogni altro elemento è interdetto  |

|---------------------------------------|-----------------------------------------------|

| Stato del rettificatore a secondario  | D5, D6, D7 e D8 ON                            |

| Corrente sul filtro d'uscita $I(L_4)$ | Positiva, decrescente                         |

| Corrente magnetizzante                | Positiva, decrescente                         |

| Considerazioni energetiche            | Transitorio di ricircolo a primario           |

| Durata                                | DINAMICA: la più breve possibile, compatibil- |

|                                       | mente con L3 (Deve assolutamente subentrare   |

|                                       | prima dell'inversione della corrente)         |

Tabella 9: Riassunto sullo stato del circuito nell'intervallo considerato

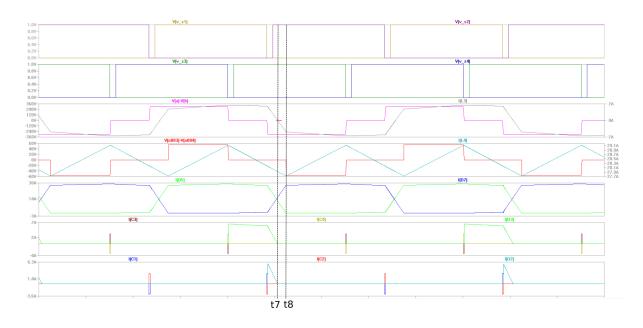

## Intervallo $t_7 \div t_8$ - Energing

In questa fase sono attivi gli switch S2 ed S3 che alimentano l'avvolgimento di primario del trasformatore, ma questa energia viene spesa sulla componente di dispersione dello stesso trasformatore, affinchè esso si agganci al livello di corrente richiesto dal filtro di uscita. L'aggancio della corrente di primario a quella richiesta al secondario, permette lo spegnimento di due diodi del ponte rettificatore a secondario e la sola conduzione della diagonale D6 e D7: questo determina la fine della fase di energizzazione e l'inizio della fase di powering con la corrente sul filtro di uscita L4 che ricomincia a salire.

Figura 24: Intervallo  $t_7 \div t_8$

Figura 25: Forme d'onda nell'intervallo  $t_7 \div t_8$

| Stato del ponte a primario            | S2 e S3 ON, ogni altro elemento è interdetto |

|---------------------------------------|----------------------------------------------|

| Stato del rettificatore a secondario  | D5, D6, D7 e D8 ON                           |

| Corrente sul filtro d'uscita $I(L_4)$ | Positiva, decrescente                        |

| Corrente magnetizzante                | Negativa, decrescente                        |

| Considerazioni energetiche            | Transitorio energizzante sul primario del    |

|                                       | trasformatore                                |

| Durata                                | DINAMICA: la più beve possibile compatibil-  |

|                                       | mente con L3                                 |

Tabella 10: Riassunto sullo stato del circuito nell'intervallo considerato

#### Considerazioni

Si può dire che le fasi di rigenerazione attiva e passiva, di energing e, infine, di powering equivalgono al duty-cycle nominale, mentre solo la fase di powering concorre al duty-cycle effettivo. Infatti, sia rigenerazione che energing sono fasi impegnate nell'inversione della corrente di primario e non portano energia sul filtro di uscita.

# Architetture di rettificatori a secondario

I circuiti rettificatori hanno lo scopo di raddrizzare la forma d'onda della tensione presente sull'avvolgimento di secondario del trasformatore rendola continua, soddisfacendo le specifiche sulla tensione di alimentazione del carico. Nel caso in esame, la forma d'onda da raddrizzare è un'onda quadra a tre livelli di periodo  $2\mu s$  e duty-cycle variabile.

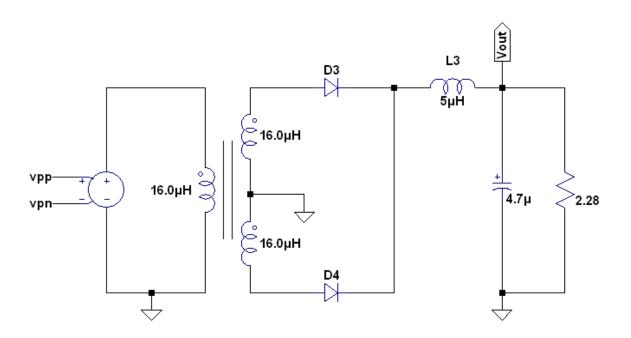

Si è scelto di analizzare il comportamento di due possibili scelte progettuali caratterizzate dal medesimo andamento dei segnali ai morsetti di uscita, in particolare, il "circuito raddrizzatore a onda intera con presa centrale" caratterizzato da un unico induttore di filtro e il circuito "Current Doubler" caratterizzato dall'uso di un trasformatore con un singolo avvolgimento a secondario e due induttori di filtro. Entrambi i circuiti necessitano dell'uso di due diodi per rettificare la tensione prelevata dal trasformatore ed alimentano il medesimo bipolo costituito dal parallelo di una capacità di filtro e il carico.

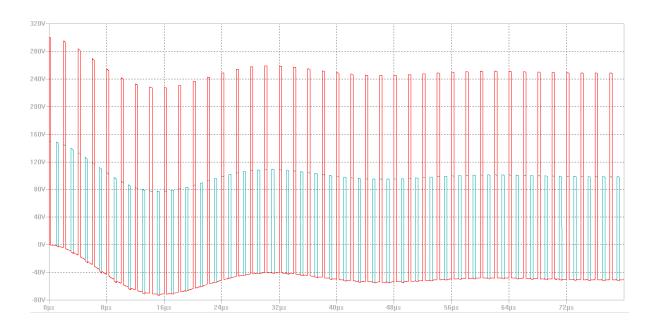

#### Rettificatore con presa centrale

Il circuito a presa centrale è caratterizzato dall'uso di un trasformatore con due avvolgimenti di secondario, aventi lo stesso numero di spire e collegati in serie in modo da fornire in uscita una tensione che verrà raddrizzata dai due diodi e filtrata dall'induttore e dalla capacità prima di essere inviata al carico.

Figura 26: Rappresentazione circuitale del raddrizzatore a secondario con presa centrale

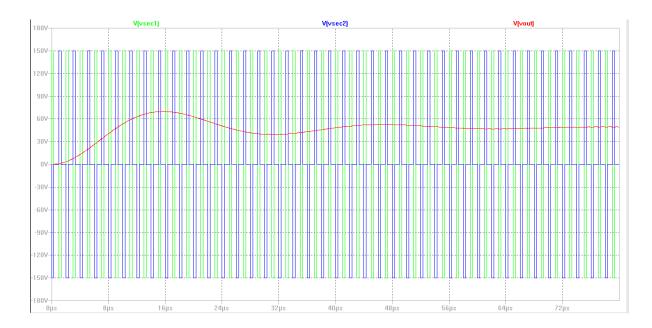

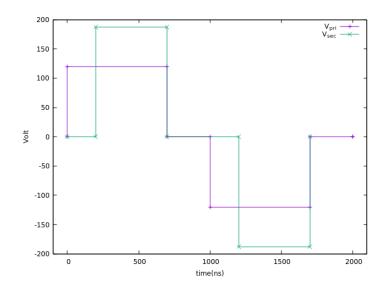

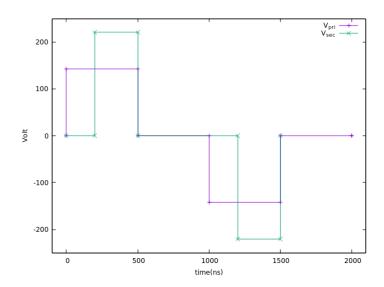

Di seguito vengono mostrate alcune forme d'onda relative al funzionamento del raddrizzatore in esame, realizzate con una tensione di alimentazione di 150V, un trasformatore costituito da tre avvolgimenti identici (con rapporto spire N : N , N) e un duty-cycle pari ad un terzo, in modo da fornire in uscita una tensione di 50V.

Figura 27: Forme d'onda relative al circuito a presa centrale

Nota :Il duty-cycle al 33.3% fa riferimento al periodo  $\frac{T}{2}$  della forma d'onda raddrizzata perchè in realtà il duty-cycle di ogni singolo avvolgimento secondario è la metà  $(\frac{1}{6}$ , alternativamente viene caricato l'avvolgimento superiore o quello inferiore a seconda di dove si trova l'impulso positivo che manda in conduzione il diodo). Si ottiene quindi:

$$V_{out_{media}} = D \cdot V_{sec}$$

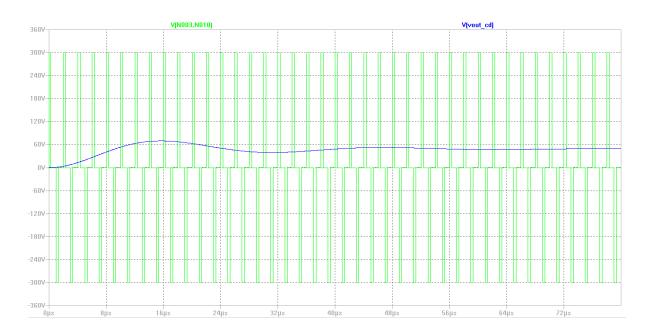

#### Rettificatore con tecnica Current Doubler

Con lo scopo di paragonare il circuito a presa centrale appena analizzato con quello current doubler, si assume come per il caso precedente, di alimentare il circuito con una tensione di 150V e di richiedere in uscita una tensione raddrizzata di 50V, utilizzando un duty-cycle pari ad un terzo.

Figura 28: Rappresentazione circuitale del raddrizzatore a secondario con tecnica current doubler

Il circuito current doubler è caratterizzato da un trasformatore costituito da un'unico avvolgimento di secondario e volendo utilizzare esattamente lo stesso trasformatore del caso precedente, il secondario sarà costituito dal doppio delle spire di quello relativo al primario (N : 2N). Per garantire le stesse prestazioni in termini di ripple, a parità di carico e del valore della capacità di filtro, i due induttori, come si avrà modo di mostrare, dovranno avere valore doppio rispetto all'unico induttore del circuito con presa centrale.

Figura 29: Forme d'onda relative al circuito current doubler

Nel grafico seguente, viene riportato un confronto tra la tensione ai capi di un induttore del circuito current doubler (linea rossa) e la tensione ai capi dell'unico induttore del circuito a presa centrale (linea blu). Si può notare come nel caso del current doubler, la tensione ha un andamento che varia con una frequenza che è la metà e un'ampiezza doppia di quella relativa al circuito con presa centrale. Questo porta alla conclusione che per fornire le stesse prestazioni in termini di livellamento della tensione di uscita, siano necessari per il current doubler, due induttori di valore doppio.

Figura 30: Forme d'onda relative al circuito current doubler

Nota: il duty-cycle al 33.3% fa riferimento al periodo  $\frac{T}{2}$  della forma d'onda del segnale sull'avvolgimento di secondario del trasformatore, perchè l'induttore superiore viene caricato durante l'impulso positivo della tensione mentre quello inferiore durante l'impulso negativo; questo significa che gli induttori si trovano ad operare con un duty-cycle della tensione ai propri capi che è la metà di quello presente ai capi dell'avvolgimento di secondario del trasformatore ( $\frac{1}{6}$  e per i rimanenti  $\frac{5}{6}$  si è nella fase di ricircolo). Si ottiene quindi:

$$V_{out_{media}} = \left(\frac{D}{2}\right) \cdot V_{sec}$$

che è la ragione per la quale si è effettuato il confronto fra i due rettificatori utilizzando un singolo secondario con un numero di spire  $(2 \cdot N)$  che è la somma delle spire dei 2 secondari dell'architettura con presa centrale (N + N).

# Dimensionamenti

#### Analisi dei casi limite

Il circuito deve garantire la regolazione dell'uscita a fronte di tutte le possibili condizioni operative dei moduli fotovoltaici in ingresso. La realizzazione di questo comportamento è demandata all'anello di retroazione, che confronta la tensione in uscita del convertitore con la tensione di riferimento desiderata, aggiornando le tempistiche dei segnali di comando del ponte intero di switch di potenza.

Ricapitolando, le specifiche sulle tensioni richieste al convertitore sono:

| $V_{in_{MIN}}$       | 120V |

|----------------------|------|

| $V_{in_{MAX}}$       | 180V |

| $V_{out_{MIN}}$      | 30V  |

| $V_{out_{MAX}}$      | 60V  |

| $V_{out_{Regolata}}$ | 48V  |

Tabella 11: Specifiche sulla tensione in ingresso e in uscita al convertitore

Una situazione limite di funzionamento è quella che prevede la massima amplificazione di tensione da parte del convertitore, ovvero, quando dovrà regolare la tensione in uscita a fronte della minima tensione disponibile in ingresso.

#### Dimensionamento del rapporto spire del trasformatore

È necessario effettuare delle considerazioni prima di dimensionare il trasformatore di isolamento. In particolare, si devono porre dei vincoli alla forma d'onda del segnale in ingresso all'avvolgimento di primario del trasformatore e alla variazione di duty-cycle desiderata nel range di funzionamento richiesto al convertitore. Inoltre è necessario considerare le perdite introdotte dagli switch che costituiscono il ponte intero nella maglia di ingresso.

#### Caduta di tensione sui dispositivi attivi del ponte intero

Dal datasheet del dispositivo di potenza scelto, l'EPC2025 a tecnologia GaN Fet, si vede come esso presenti una resistività tra il terminale di drain e quello di source pari a  $r_{ds_{ON}} = 120m\Omega$ ; per calcolare la caduta di tensione richiesta in questa fase di dimensionamento, è necessasio moltiplicare la resistività del canale di conduzione per la corrente che scorre in esso. In questo scenario, il caso peggiore è rappresentato dal valore massimo della corrente fornita dai moduli fotovoltaici che coincide con il valore della corrente di corto circuito degli stessi. In generale il convertitore opererà in una condizione nominale di duty-cycle che dipende dal dimensionamento del rapporto spire. In questa condizione di operazione molto in salita è plausibile ipotizzare che almeno un 50% di duty-cycle effettivo sia da garantire: questo significa che essendo la tensione sui moduli fotovoltaici regolata da un condensatore, i dispositivi attivi del ponte vedono scorrere una corrente media  $I_{cc}$ , ovvero essendo il ciclo di lavoro metà, una corrente a forma d'onda quadra con valore di picco doppio. Se ne deduce quindi la seguente stima di caduta sugli interruttori.

$$V_{ds_{ON}} = r_{ds_{ON}} \cdot 2 \cdot I_{cc} = 120m\Omega \cdot 2 \cdot 8.37A = 2V$$

La caduta di tensione su un singolo GaN FET, nelle peggiori condizioni di utilizzo è pari ad 2V; la maglia che connette l'avvolgimento di primario del trasformatore alla tensione di alimentazione fornita dai moduli fotovoltaici è però costituita dalla serie di due dispositivi GaN FET. Si ottiene quindi che la caduta di tensione dovuta a questo fenomeno è pari a 4V.

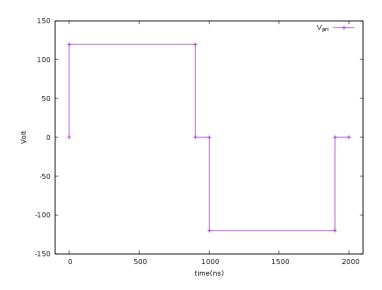

### Specifiche sul Duty-Cycle del segnale di controllo del ponte intero

Come visto in precedenza, l'intero funzionamento del convertitore è regolato dai segnali di controllo del ponte intero; in particolare, il loro andamento temporale determina la forma d'onda del segnale di alimentazione posto in ingresso all'avvolgimento di primario del trasformatore e regola il funzionamento del circuito in una delle 16 fasi di funzionamento possibili.

Si è scelto di rispettare tre specifiche di progetto a riguardo:

• Si prevede un intervallo di ricircolo di almeno 100ns. Questo significa che fra il leg in anticipo, che commuta a corrente piena, e il leg in ritardo, che commuta a corrente debole si deve rispettare un ritardo non inferiore a 100ns. Si ricorda che entrambi i leg commutano con duty-cycle 50%.

Questo impone un vincolo al massimo duty-cycle con il quale il modulatore phaseshifted che genera il disallineamento fra i leg può operare, che risulta essere:

$$d_{MAX} = \frac{T_{ON}}{T} = \frac{2000ns - (2 \cdot 100ns)}{2000ns} = 0.9 \longrightarrow 90\%$$

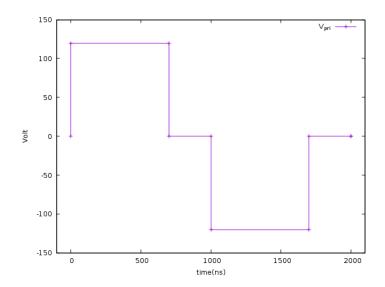

Figura 31: Rappresentazione della forma d'onda in ingresso all'avvolgimento di primario del trasformatore con duty-cycle del 90%

Nota: È fondamentale prevedere una durata dell'intervallo a 0V della tensione in ingresso, sufficiente da contenere le tre fasi di funzionamento spiegate in precedenza, commutazione quasi-risonante, ricircolo passivo e ricircolo attivo che permettono il corretto funzionamento del convertitore.

• Si sceglie di allocare uno slot temporale di durata massima pari a 200ns per l'inversione della corrente.

L'imposizione di questo vincolo, legato alla presenza dell'induttanza di dispersione del trasformatore, produce degli effetti sul duty-cycle della forma d'onda sull'avvolgimento secondario del trasformatore, considerando che durante l'intervallo di tempo necessario all'inversione della corrente di primario, al secondario la tensione è nulla perchè tutti i diodi sono accesi per consentire il ricircolo della corrente imposta dal filtro di uscita.

È possibile ora calcolare il valore massimo di  $L_3$  che permetta di rispettare tale vincolo. Questa specifica limita il valore dell'induttanza di dispersione del trasformatore e quindi anche la possibilità di ottenere commutazioni ZVS quando la corrente richiesta in uscita al convertitore è molto bassa o nel transitorio di accensione, quando il circuito di soft start impone al convertitore di operare con bassi valori di duty-cycle.

Figura 32: Confronto tra forme d'onda presenti ai capi dell'avvolgimento di primario e di secondario del trasformatore nel caso di duty-cycle del segnale in ingresso pari al 70% e con rapporto di trasformazione in salita

Partendo dall'equazione fondamentale degli induttori

$$v_L = L \cdot \frac{\partial i(t)}{\partial t}$$

e prendendo in esame una transizione del segnale in ingresso al trasformatore dal passaggio per lo zero al valore massimo (il caso duale è simmetrico), si ottiene:

$$\begin{aligned} v_{pri_{0V \to 120V}} &= L_3 \cdot \frac{\partial i(t)}{\partial t} \\ 120V &= L_3 \cdot \frac{+15A - (-15A)}{200ns} \\ L_3 &\leqslant \frac{120V \cdot 200ns}{30A} = 800nH \end{aligned}$$

Operando le scelte appena discusse ne deriva che si può garantire un duty-cycle effettivo  $(D_{eff})$  del segnale di ingresso all'avvolgimento di primario del trasformatore pari al 70% nel caso in cui la sorgente fotovoltaica in ingresso al convertitore fornisca la corrente massima.

Figura 33: Rappresentazione della forma d'onda in uscita all'avvolgimento di secondario del trasformatore con duty-cycle del 70%

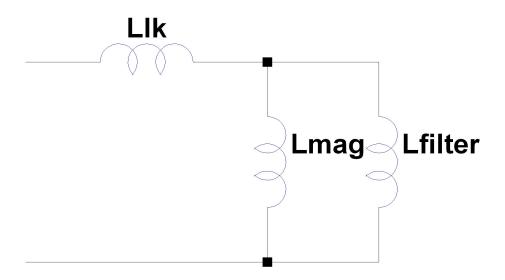

Anche dopo avere tenuto conto del duty-cycle effettivo (ridotto per effetto dell'intervallo necessario a invertire la corrente) esiste un'ulteriore forma di degrado per il guadagno di tensione fra la sorgente DC primaria e il secondario: si tratta del partitore di tensione fra l'induttanza dispersa e il parallelo fra le induttanze di magnetizzazione e quella di filtro riflessa a primario.

Il rettificatore di uscita può essere un normale rettificatore a presa centrale o un current doubler. In ogni caso la tensione media di uscita rettificata è calcolabile come valor medio della forma d'onda quadra con duty-cycle effettivo nel periodo T del ciclo intero e considerando la tensione totale ai secondari nel caso della presa centrale. Indicando dunque con  $V_{L_R}$  il degrado di tensione provocato dal partitore possiamo scrivere:

$$V_{out_{media}} = \left[ (V_{in} - V_{ds_{ON}} - V_{L_R}) \cdot \frac{N_{sec}}{N_{pri}} \right] \cdot D_{eff}$$

Per esplicitare il termine  $V_{L_R}$  possiamo fare alcune ipotesi basandoci sulla figura seguente. Poichè  $L_{lk}$  è il 5% della componente magnetizzante allora sicuramente c'è un degrado non inferiore al 95%. Dato che invece ci sarà la maggior parte della corrente che scorre sul filtro, c'è da attendersi un degrado assai più pronunciato per effetto della corrente che scorre su  $L_{filter}$  che è quella equivalente a secondario riportata a primario.

Ipotizzando  $L_{lk} = 800nH$ ,  $L_{mag} = 16\mu H$  e  $L_{filter} = \left(\frac{N_{pri}}{N_{sec}}\right)^2 \cdot 10\mu H = 2.5\mu H$  (si è ipotizzato un rapporto spire circa 2 in salita), c'è da aspettarsi un degrado dell'ordine del 66%.

Figura 34: Rappresentazione del partitore induttivo per la stima della caduta di tensione sulla componente di dispersione del trasformatore

È ora possibile calcolare la tensione media rettificata in uscita  $(V_{out_{media}})$  nel caso di utilizzo di un finale con funzionamento a current doubler:

$$V_{out_{media}} = \left(\frac{N_{sec}}{N_{pri}}\right) \cdot \frac{D_{eff}}{2} \cdot V_{in}$$

dove  $D_{eff}$  è il duty-cycle effettivo, ovvero, quello effettivamente presente a secondario e decurtato dell'intervallo di  $T_{ON}$  impiegato per l'inversione della corrente a primario. Tenendo conto delle cadute sui dispositivi attivi del ponte intero in ingresso e delle perdite dovute al partitore induttivo, l'equazione diventa:

$$V_{out_{media}} = \left(\frac{N_{sec}}{N_{pri}}\right) \cdot \frac{D_{eff}}{2} \cdot \left(V_{in} - 2 \cdot V_{ds_{ON}}\right) \frac{L_{mag} \|L_{filter}^{'}}{L_{mag} \|L_{filter}^{'} + L_{lk}}$$

dove si può porre

$$L_{filter}^{'} = L_{filter} \cdot \left(\frac{N_{pri}}{N_{sec}}\right)^{2} = L_{filter} \cdot \rho^{2}$$

Unendo gli ultimi due risultati, si ottiene:

$$\begin{split} V_{out_{media}} &= (V_{in} - 2 \cdot V_{ds_{ON}}) \cdot \frac{D_{eff}}{2} \cdot \left(\frac{N_{sec}}{N_{pri}}\right) \cdot \frac{\frac{L_{mag} \cdot L_{filter}'}{L_{mag} + L_{filter}'}}{\frac{L_{mag} \cdot L_{filter}'}{L_{mag} + L_{filter}'}} + L_{lk} \\ V_{out_{media}} &= (V_{in} - 2 \cdot V_{ds_{ON}}) \cdot \frac{D_{eff}}{2} \cdot \frac{1}{\rho} \cdot \frac{L_{mag} \cdot L_{filter} \cdot \rho^2}{L_{mag} \cdot L_{filter} \cdot \rho^2 + L_{lk} \cdot \left(L_{mag} + L_{filter} \cdot \rho^2\right)} \\ V_{out_{media}} &= (V_{in} - 2 \cdot V_{ds_{ON}}) \cdot \frac{D_{eff}}{2} \cdot \frac{L_{mag} \cdot L_{filter} \cdot \rho^2 + L_{lk} \cdot \left(L_{mag} + L_{filter} \cdot \rho^2\right)}{\frac{L_{lk} \cdot L_{mag}}{\rho} + \left(L_{mag} + L_{lk}\right) \cdot L_{filter} \cdot \rho} \end{split}$$

Utilizzando per i parametri i seguenti valori

| $L_{lk}$      | 800nH     |

|---------------|-----------|

| $L_{mag}$     | $16\mu H$ |

| $L_{filter}$  | $10\mu H$ |

| $V_{in}$      | 120V      |

| $V_{ds_{ON}}$ | 2V        |

si ottiene che utilizzando  $\rho = \frac{N_{pri}}{N_{sec}} = \frac{1}{2}$  sarebbe necessario un duty-cycle efficace  $(D_{eff})$  del 60% per ottenere una tensione di uscita leggermente superiore a 50V, offrendo un margine del 10% sulla specifica progettuale che limita il duty-cycle massimo.

Avendo dimensionato il rapporto spire del trasformatore è possibile verificare il valore del duty-cycle utilizzato dal modulatore in condizioni di funzionamento nominale, ovvero quando la tensione fornita dai moduli fotovoltaici si assesta al valore di 142.2V. In queste condizioni, risulta che il duty-cycle sia di poco inferiore al 50%. Il rapporto spire scelto come 1:2 risulta essere idoneo all'applicazione, in quanto consente al modulatore di operare con valori di duty-cycle appropriati, superiori al 50% quando viene richiesta piena potenza e inferiori quando il carico richiederà meno potenza.

Figura 35: Forme d'onda ai capi degli avvolgimenti del trasformatore nel funzionamento nominale

Nota: Il valore dell'intensità di corrente prelevata dai moduli fotovoltaici è nella peggiore delle ipotesi pari alla corrente di corto circuito, ovvero a 8.37A. Considerando di operare alla massima corrente, quindi con un duty-cycle efficace del 60%, ci sarà una corrente da commutare con un intensità quasi doppia, ovvero pari a 13.95A.

Infine, un'ulteriore specifica progettuale prevede che il valore dell'induttanza di dispersione sia pari al 5% del valore induttivo dell'avvolgimento di primario; con i valori numerici ottenuti in precedenza è possibile ricavare i valori induttivi degli avvolgimenti del trasformatore:

$$N^{2} = \left(\frac{N_{pri}}{N_{sec}}\right)^{2} = \left(\frac{1}{2}\right)^{2} = 0.25 = \frac{L_{1}}{L_{2}}$$

$$L_{1} = \frac{100 \cdot L_{3}}{5} = \frac{100 \cdot 800nH}{5} = 16\mu H$$

$$L_{2} = \frac{L_{1}}{N^{2}} = \frac{16\mu H}{0.25} = 64\mu H$$

#### Considerazioni sulla commutazione risonante

Nel capitolo precedente, nel dimensionamento del rapporto spire del trasformatore, si è dimensionata anche l'induttanza di dispersione dello stesso, seguendo unicamente come direttiva la durata dello slot temporale disponibile per invertire il valore della corrente sull'avvolgimento di primario del trasformatore, non garantendo però di riuscire ad effettuare sempre delle commutazioni ZVS.

Il tempo di transizione massimo si ha nelle transizioni del leg debole (formato dalla coppia S1 ed S2) del convertitore, mentre opera nella condizione di minima corrente al carico.

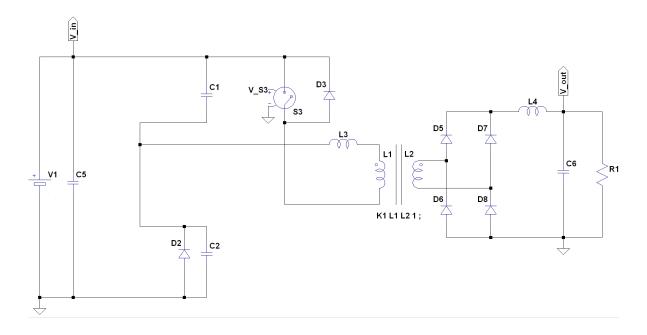

Figura 36: Schema elettrico del convertitore

È necessario che il circuito risonante rispetti due condizioni ed antrambe sono correlate all'energia immagazzinata nell'induttore di dispersione  $L_3$ .

• L'induttanza di dispersione deve immagazzinare sufficiente energia da permettere alle capacità del bipolo risonante di caricarsi/scaricarsi al "rail" opposto di alimentazione ( $V_{in}$  o GND). • La transizione appena citata deve avvenire all'interno del intervallo di tempo stabilito (Dead-Time).

Se una o entrambe le condizioni non venissero rispettate, la condizione Zero Voltage Switching non sarebbe garantita e si avrebbe una commutazione più dissipativa.

Gli elementi che formano il bipolo risonante sono l'induttore di dispersione del trasformatore  $L_3$  e la capacità  $C_R$ , costituita dal parallelo delle due capacità degli switch di un leg. Per garantire le commutazioni "ZVS", il tempo che ottimizza la transizione deve essere all'incirca un quarto del periodo del bipolo risonante.

La pulsazione di risonanza del bipolo è:

$$\omega_R = \frac{1}{\sqrt{L_3 \cdot C_R}}$$

$$t_{max_{transizione}} = \frac{\pi}{2 \cdot \omega_R}$$

La capacità Drain-Source degli switch deve essere moltiplicata di un fattore  $\frac{4}{3}$  per tenere conto dell'incremento della stessa nell'operare a tensioni elevate; considerando che, ad ogni transizione, si avranno due capacità Drain-Source in parallelo è possibile unire questo concetto al fattore correttivo precedente, moltiplicandolo di un fattore 2.

La capacità del bipolo risonante, risulta essere:

$$C_R = \frac{8}{3} \cdot C_{OSS} = 187pF$$

con  $C_{OSS} = 70 pF$  (come specificato nel data-sheet del dispositivo in tecnologia GaN FET EPC2025)

L'energia capacitiva necessaria per completare la transizione risulta essere:

$$W(C_R) = \frac{1}{2} \cdot C_R \cdot V_{ab}^2 = 1.88 \mu J$$

(calcolata in condizioni di funzionamento nominale, quando  $V_{in} = 142.2V$ )

L'energia immagazzinata nell'induttanza  $L_3$  deve essere maggiore dell'energia necessaria a caricare e scaricare le capacità di uscita degli switch che formano il leg che commutano all'interno del periodo di tempo massimo per la transizione. All'interno del trasformatore, esiste dell'energia immagazzina nell'induttanza magnetizzante finchè la corrente al secondario blocca la tensione a primario a zero. La corrente magnetizzante deve scorrere sugli avvolgimenti a primario e concorre all'immagazzinamento di energia sulla componente dispersa, soprattutto nel caso di carichi leggeri.

L'energia immagazzinata nell'induttanza del bipolo risonante  $L_3$  è:

$$W(L_R) = \frac{1}{2} \cdot L_R \cdot I(L_3)^2$$

Il valore minimo della corrente a primario richiesta dal circuito può essere valutata secondo la seguente relazione:

$$I(L_3)_{MIN} = \sqrt{\frac{C_R \cdot V_{IN}^2}{L_3}} = \sqrt{\frac{1.86 \cdot 10^{-10} \cdot (142.2)^2}{800 \cdot 10^{-9}}} = 2.17A$$

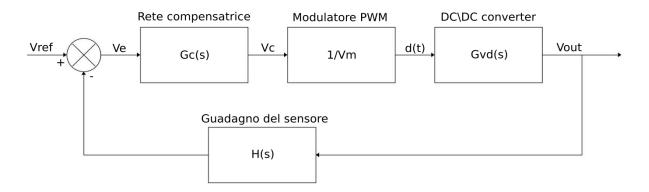

# Progetto dell'anello di retroazione per il convertitore

Anello di retroazione per la regolazione della tensione d'uscita

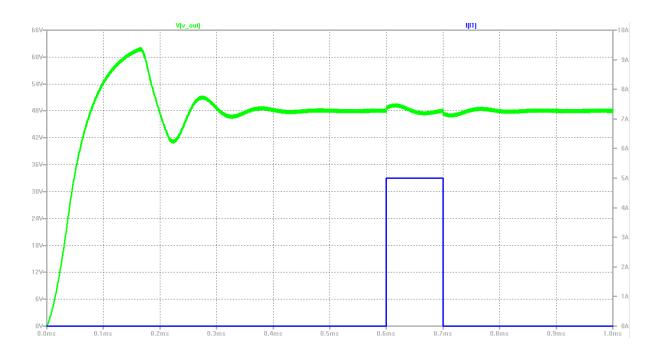

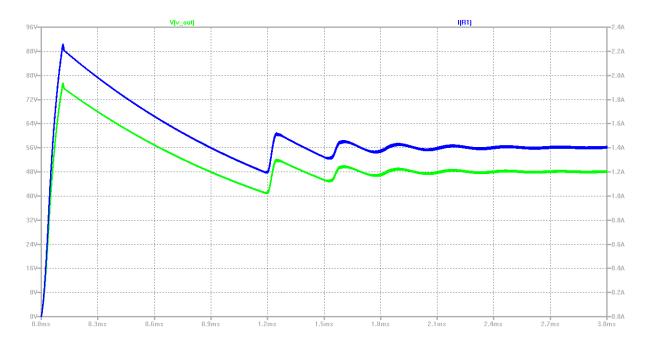

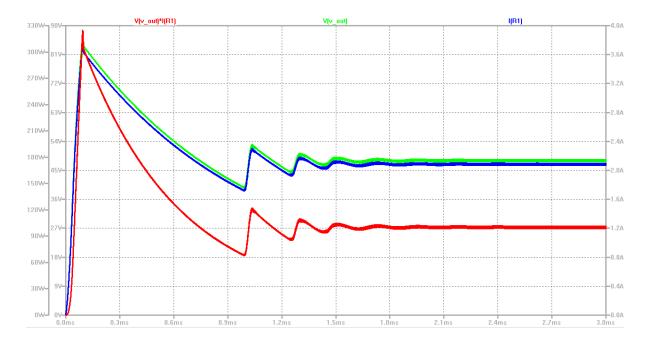

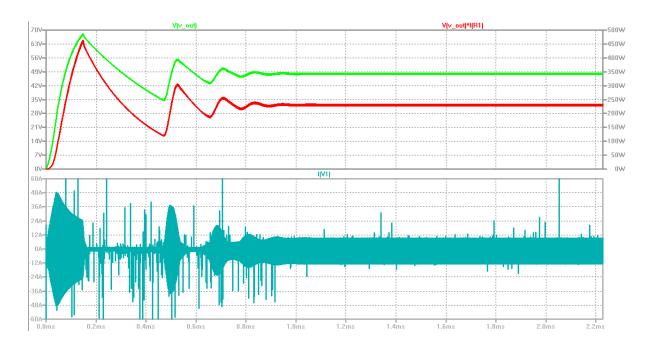

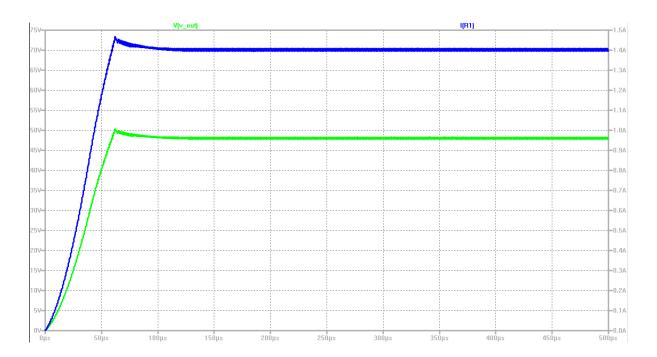

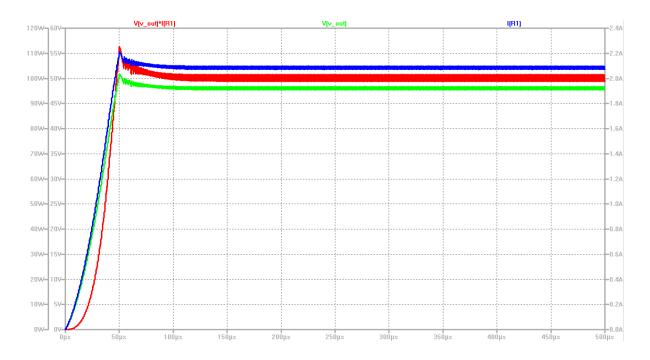

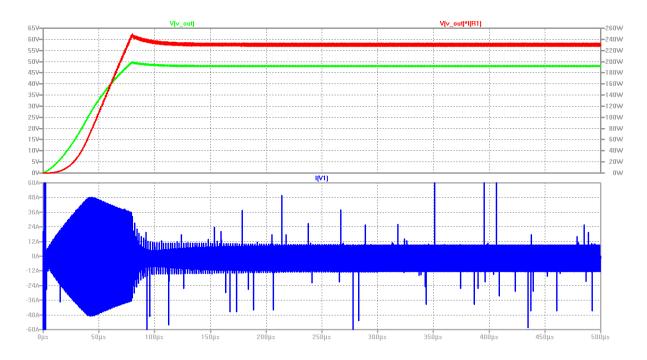

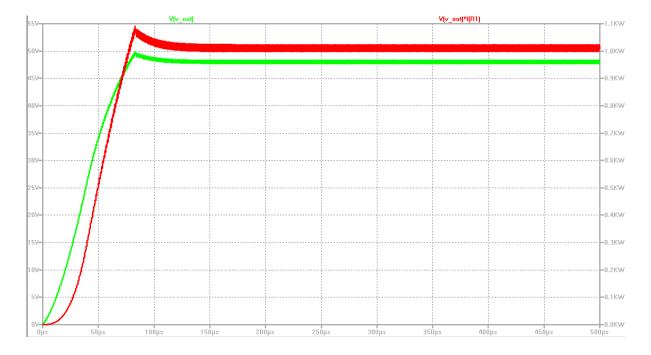

La tensione di uscita di un convertitore in corrente continua è controllata in modo da rimanere all'interno di un determinato intervallo di tolleranza in risposta a cambiamenti del carico o della tensione della linea di ingresso. Si ottiene questo risultato usando un sistema di controllo in anello chiuso a retroazione negativa che confronta il valore istantaneo della tensione di uscita del convertitore con un valore di riferimento. L'anello di retroazione, genera un segnale con modulazione a larghezza d'impulso che pilota la rete di generazione dei segnali con modulazione phase-shifted a monte degli switch di potenza. Si è inoltre introdotta una rete di soft-start per rendere più graduale l'accensione del convertitore, forzandolo ad operare nelle fasi iniziali con piccoli valori di duty-cycle.

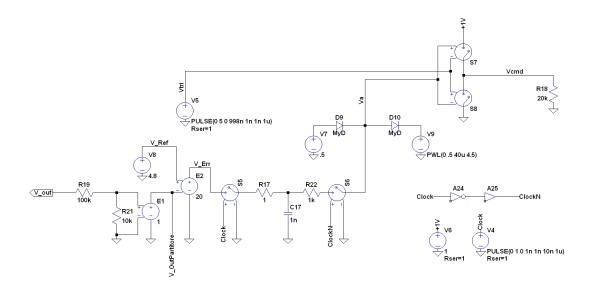

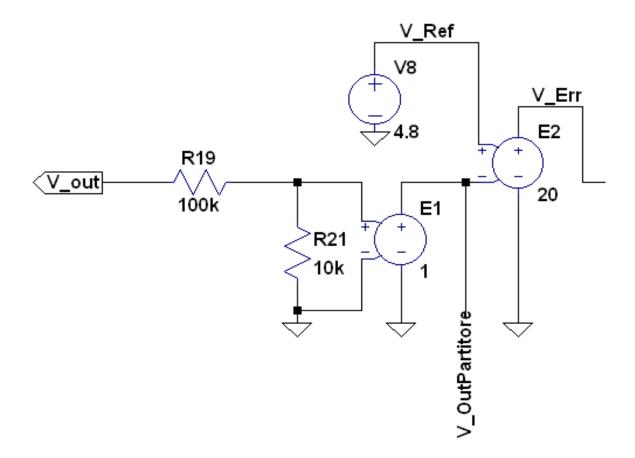

Figura 37: Anello di retroazione per la regolazione della tensione di uscita

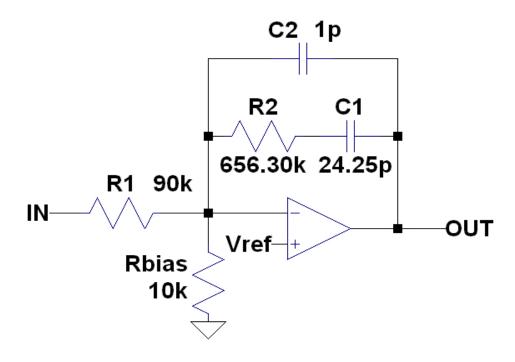

Analizzando l'anello di retroazione, troviamo nella parte iniziale il partitore resistivo che preleva la frazione della tensione di uscita che si deve confrontare con il riferimento, subito seguito dall'amplificatore d'errore, ovvero il blocco che effettua il controllo vero e proprio tra il valore di tensione istantaneo in uscita dal convertitore e la tensione di riferimento scelta.

Figura 38: Rete di condizionamento del segnale e amplificatore d'errore

Più nel dettaglio, nell'amplificatore d'errore viene eseguita una sottrazione tra il segnale di riferimento e il valore attuale della tensione in uscita dal convertitore; il tutto poi viene moltiplicato per il guadagno dell'amplificatore: più elevato è il guadagno e maggiori saranno i benefici derivanti dalla retroazione; tuttavia, un guadagno troppo elevato potrebbe portare ad avere dei comportamenti instabili.

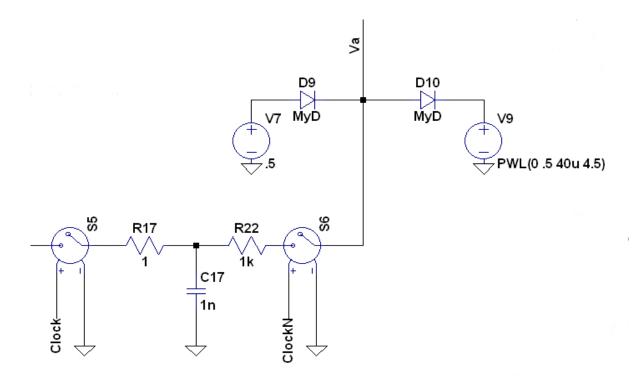

Il segnale errore così ottenuto costituisce il segnale analogico che si deve confrontare con il segnale a rampa per generare la modulazione PWM; prima del confronto però è necessario adottare qualche condizionamento: innanzitutto si preferisce effettuare il campionamento del segnale errore per disporre di un valore costante lungo tutto il periodo; inoltre è bene imporre dei limiti ben precisi per evitare la generazione di duty-cycle troppo piccoli o troppo grandi; infine, proprio grazie a una gestione dinamica del limite

superiore è possibile implementare il circuito di soft-start che consente un lento incremento del duty-cycle fino al valore massimo anche nel caso in cui si parta con un valore enorme del segnale analogico d'errore (come avviene allo start-up quando la tensione di uscita parte da zero ed è ben lontana dal valore desiderato).

Figura 39: Circuito per la trasformazione del segnale d'errore in una rampa e per limitare l'escursione del segnale in modulazione PWM

Si è così giunti al modulatore PWM vero e proprio che confronta il segnale generato negli step precedenti con un segnale a rampa periodico. Il circuito si compone di un comparatore che fornisce un uscita due livelli. L'uscita sarà a valore logico alto quando il segnale analogico derivante dall'errore ha un valore superiore a quello della rampa per poi commutare al valore logico basso nell'istante in cui il segnale della rampa eccede il valore di quello analogico; il segnale rimane basso fino al termine del periodo in cui la rampa rapidamente torna al valore minimo ed inizia il nuovo  $T_{ON}$ .

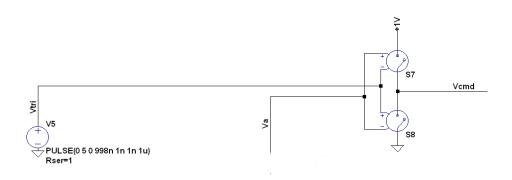

Figura 40: Modulatore a larghezza d'impulso(PWM)

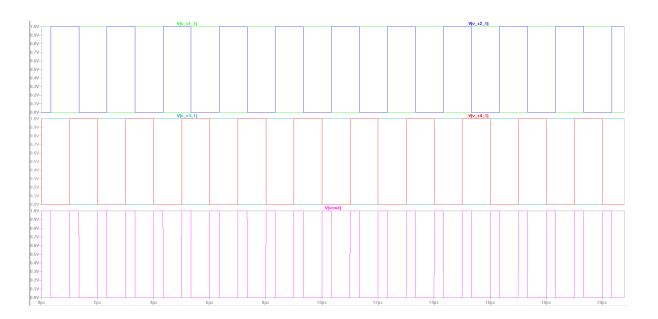

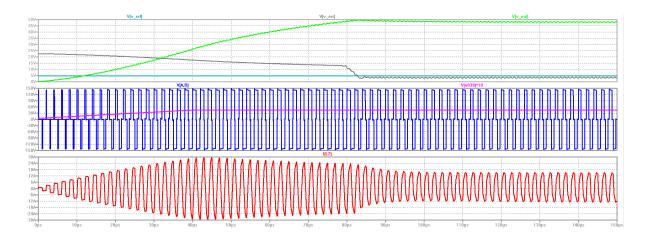

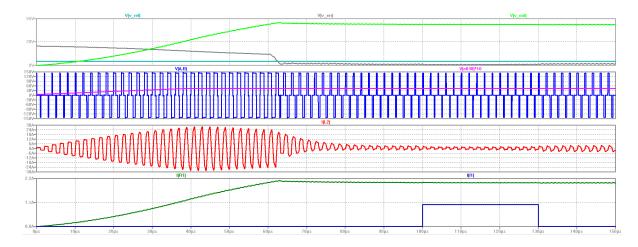

L'uscita a due livelli del modulatore PWM, identificata con  $V_{cmd}$ , è un onda quadra con periodo di  $1\mu s$ , ovvero la metà del periodo di commutazione scelto per i singoli leg del ponte intero. Si ottengono quindi due fronti di salita e due di discesa del segnale  $V_{cmd}$  all'interno del periodo di commutazione che verranno elaborati da un modulatore Phase-Shifted, costituito da una rete sequenziale di due flip-flop D.

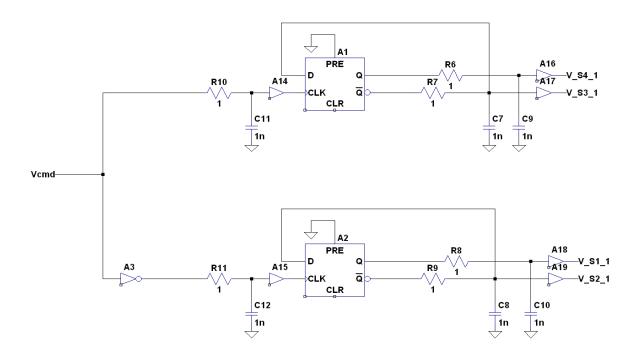

Figura 41: Modulatore Phase-Shifted

Il segnale  $V_{cmd}$ , viene utilizzato come segnale di clock per i due flip-flop e sull'ingresso D viene retroazionato il valore attuale negato dell'uscita dello stesso. Si noti come il segnale di clock non sia lo stesso per i due flip-flop, infatti, il flip-flop responsabile della commutazione del leg forte (A1) riceve il segnale "normale" e le commutazioni delle sue uscite avvengono sui fronti di salita di  $V_{cmd}$ , mentre il flip-flop A2, responsabile della commutazione del leg debole, riceve la versione negata del segnale di clock e le commutazioni delle sue uscite avvengono sui fronti di discesa di  $V_{cmd}$ . A questo punto dell'elaborazione si ottengono dei segnali di comando degli switch di un leg duali, ovvero, allo spegnimento di uno switch è seguito in contemporanea, l'accensione del duale.

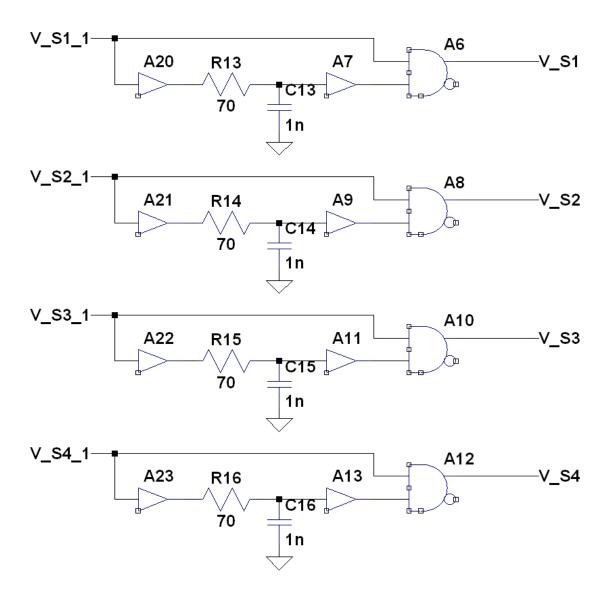

Figura 42: Forme d'onda dei segnali generati dal modulatore Phase-Shifted

Per garantire il corretto funzionamento del circuito, in accordo con la teoria già presentata, è necessario inserire un Blanking-Time nei segnali di comando degli switch di potenza di ogni leg. Si è quindi aggiunta una rete che ritarda le commutazioni delle uscite dei flip-flop che permette di inserire un ritardo tra lo spegnimento di uno switch di un leg e l'accensione del suo duale. I segnali così ottenuti sono pronti per pilotare i dispotivi attivi del ponte intero, comandati dal segnale  $V_{cmd}$ , che regola le tempistiche di accensione e spegnimento dei due leg.

Figura 43: Rete per la generazione del Blanking-Time

Figura 44: Forme d'onda dei segnali di comando degli switch di potenza del ponte intero con intervallo di Blanking-Time

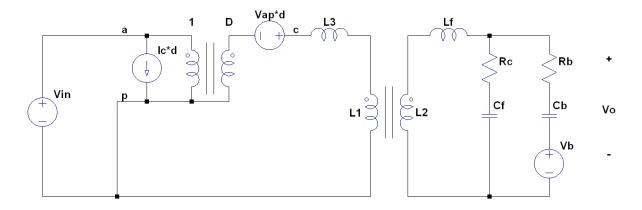

#### Modello ai piccoli segnali del convertitore

Al fine di effettuare lo studio della funzione di trasferimento del convertitore, è necessario ricavare il modello ai piccoli segnali dello stesso. Infatti, grazie a tale modello è possibile effettuare una analisi della stabilità della rete, permettendo poi di procedere con la progettazione di un anello di retroazione che permetta di controllare le variabili di uscita del convertitore nella maniera desiderata. Esistono diversi metodi per ricavare un modello alle variazioni di un convertitore. In particolare, si è scelto di utilizzare un modello equivalente ai piccoli segnali del circuito derivato dal modello semplificato dei convertitori a commutazione PWM illustrato in [1, Erickson].

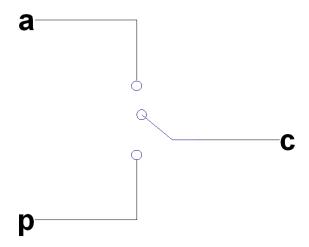

Partendo dalla definizione di un modello di switch single-pole double-through a tre terminali, valido per le tre principali tipologie di convertitori (Buck, Boost, Buck-Boost), traducendolo poi in un circuito formato di soli generatori dipendenti di tensione e corrente ed effettuando una linearizzazione dei parametri attorno al punto di lavoro, si ottiene il modello ai piccoli segnali del convertitore DC/DC.

Figura 45: Modello di switch a tre terminali

I terminali active (a) e passive (p), costituiscono la porta comandata in tensione, mentre common (c) è il terminale, in genere riferito a passive, della porta comandata in corrente.

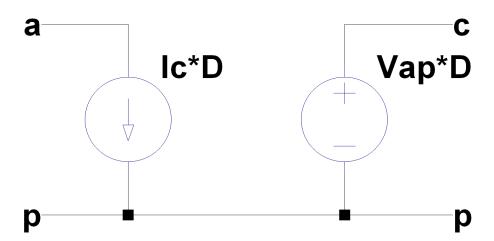

Figura 46: Rappresentazione della rete di switch mediante generatori dipendenti

La tensione  $v_{ap}(t)$  alla porta di ingresso, rappresenta la tensione sugli switch della rete, mentre la corrente  $i_c(t)$  rappresenta la corrente in uscita sul terminale common. Di conseguenza, sono stati indicati come dipendenti i generatori di corrente  $i_c \cdot D(t)$  e di tensione  $v_{ap} \cdot D(t)$  che rappresentano gli esatti segnali presenti ai terminali della rete di partenza.

Quello ottenuto fin'ora è un modello di grande segnale e perturbando le forme d'onda attorno al punto di lavoro, si ottiene il modello ai piccoli segnali linearizzato.

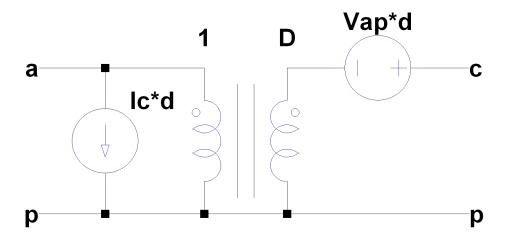

Figura 47: Modello semplificato ai piccoli segnali del convertitore a commutazione PWM

Il generatore di tensione indipendente  $v_{ap} \cdot d$  è controllato dalle variazioni del dutycycle, così come il generatore indipendente di corrente  $i_c \cdot d$ , mentre il trasformatore con rapporto spire 1:D modella la presenza del duty-cycle nominale del circuito e trasduce verso destra le variazioni di  $V_{in}$  e verso sinistra le variazioni di corrente assorbita.

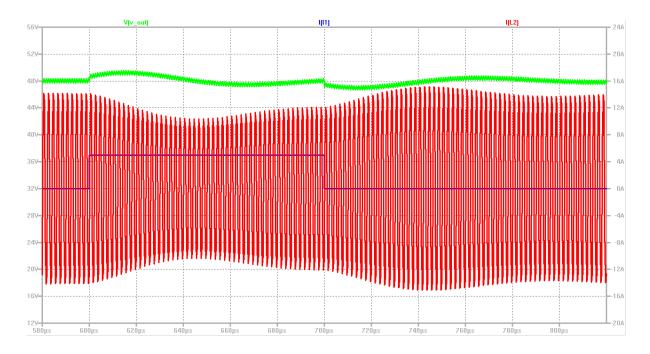

La corrente di uscita del convertitore a ponte intero dotato di current doubler è formata dalla somma delle correnti dei due induttori di filtro. Quindi il modello equivalente ai piccoli segnali del convertitore può essere rappresentato come il parallelo di due convertitori Buck. Considerando che i due induttori posti sull'uscita condividono un unica capacità di filtro, il valore dell'induttanza nel modello equivalente ai piccoli segnali per il convertitore Buck singolo che rappresenta il parallelo dei due diventa la metà del valore originale.

Con lo scopo di ottenere la funzione di trasferimento del circuito in esame è necessario disporre dei dati relativi al carico che esso dovrà alimentare. In particolare si fa riferimento ad una batteria con capacità equivalente pari a  $C_b = 91250F$  e con resistenza equivalente di  $R_b = 118m\Omega$ .

Figura 48: Modello equivalente ai piccoli segnali del convertitore Phase Shifted Full Bridge

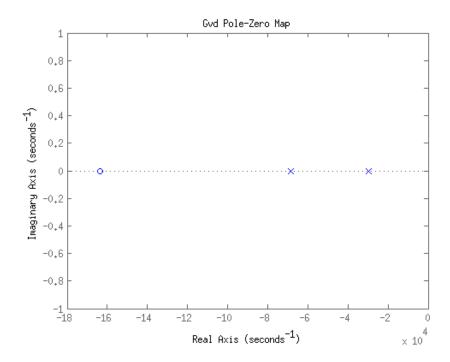

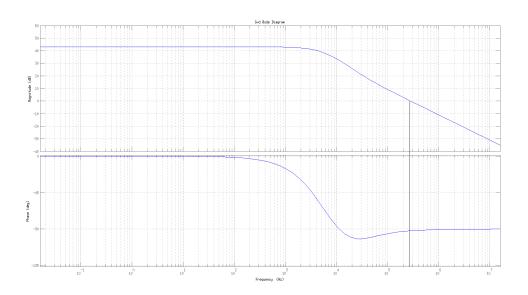

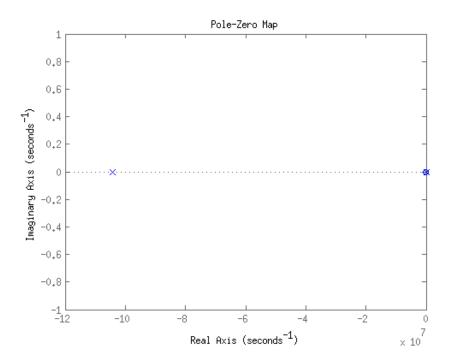

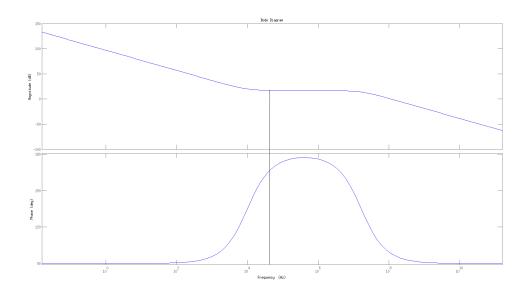

#### Studio della funzione di trasferimento del convertitore

Partendo dal modello equivalente ai piccoli segnali del convertitore ricavato in precedenza è possibile ricavare l'impedenza equivalente di uscita e la funzione di trasferimento  $G_{vd}$ , che per definizione mette in relazione la variazione della tensione di uscita con la variazione del duty-cycle.

L'impedenza equivalente  $Z_{eq}$  è composta dal parallelo dell'impedenza della capacità di filtro di uscita con l'impedenza della batteria di carico.

$$Z_{eq} = \left(R_b + \frac{1}{sC_b}\right) \| \left(R_c + \frac{1}{sC_f}\right) = \frac{s^2(R_bR_cC_bC_f) + s(R_bC_b + R_cC_f) + 1}{s^2(R_bC_bC_f + R_cC_bC_f) + s(C_b + C_f)}$$

La funzione di trasferimento  $G_{vd}(s)$  è per definizione

$$G_{vd}(s) = \frac{\delta v_o}{\delta d}|_{v_{in}=0} = \frac{v_{sec}}{d} \cdot \frac{v_o}{v_{sec}} = \frac{v_{sec}}{d} \cdot \frac{Z_{eq}}{(sL_f + Z_{eq})} = G_{vd}(s) = 142.2 \cdot \frac{s^2(R_bR_cC_bC_f) + s(R_bC_b + R_cC_f) + 1}{s^3(R_bC_bC_fL_f + R_cC_bC_fL_f) + s^2(C_bL_f + C_fL_f + R_bR_cC_bC_f) + s(R_bC_b + R_cC_f) + 1}$$

Considerando che la costante di tempo dovuta al bipolo che modella la batteria è pari a  $\tau_B = R_b \cdot C_b = 118m\Omega \cdot 91250F = 10767.5s$  (circa 3 ore), è possibile trascurare il suo contributo nell'analisi della funzione di trasferimento, quindi la nuova funzione di trasferimento risulta essere